【 FPGA 】序列检测器的Mealy状态机实现

【摘要】 上篇博文讲了使用Moore状态机来设计一个序列检测器:序列检测器的Moore状态机实现

原理一致,这里只不过采用了Mealy状态机实现,快速给出:

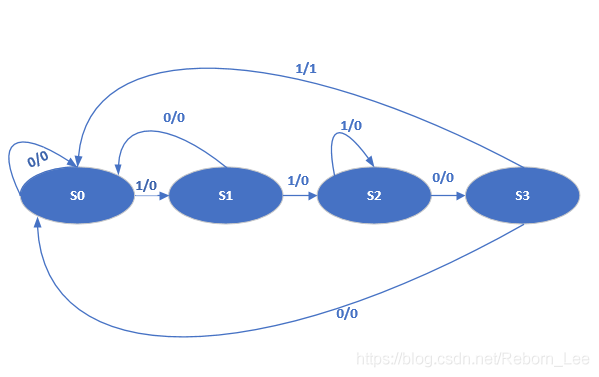

状态转移图如下:被检测序列为1101,也就是说,如果出现1101序列,则输出为1,否则输出为0。

Verilog HDL代码为:

`timescale 1ns / 1ps//// Company: // Enginee...

上篇博文讲了使用Moore状态机来设计一个序列检测器:序列检测器的Moore状态机实现

原理一致,这里只不过采用了Mealy状态机实现,快速给出:

状态转移图如下:被检测序列为1101,也就是说,如果出现1101序列,则输出为1,否则输出为0。

Verilog HDL代码为:

-

`timescale 1ns / 1ps

-

//

-

// Company:

-

// Engineer:

-

//

-

// Create Date: 2019/01/04 20:34:06

-

// Design Name:

-

// Module Name: seq_det_mealy

-

// Project Name:

-

// Target Devices:

-

// Tool Versions:

-

// Description:

-

//

-

// Dependencies:

-

//

-

// Revision:

-

// Revision 0.01 - File Created

-

// Additional Comments:

-

//

-

//

-

-

-

module seq_det_mealy(

-

input clk,

-

input reset,

-

input din,

-

output reg dout

-

);

-

-

localparam [1:0]

-

s0 = 2'b00,

-

s1 = 2'b01,

-

s2 = 2'b10,

-

s3 = 2'b11;

-

-

reg [1:0] current_state,next_state;

-

-

always @(posedge clk, posedge reset)

-

begin

-

if(reset)

-

current_state <= s0;

-

else

-

current_state <= next_state;

-

-

end

-

-

always @ *

-

begin

-

case(current_state)

-

s0:

-

if(din == 1'b1) next_state = s1;

-

else next_state = s0;

-

s1:

-

if(din == 1'b1) next_state = s2;

-

else next_state = s1;

-

s2:

-

if(din == 1'b0) next_state = s3;

-

else next_state = s2;

-

s3: next_state = s0;

-

default: next_state = s0;

-

endcase

-

-

end

-

-

always @ *

-

begin

-

if(reset) dout = 1'b0;

-

else if( (current_state == s3)&&(din == 1'b1) ) dout = 1'b1;

-

else dout = 1'b0;

-

-

end

-

-

-

endmodule

用上篇博文的测试代码:

-

`timescale 1ns / 1ps

-

//

-

// Company:

-

// Engineer:

-

//

-

// Create Date: 2019/01/04 15:24:59

-

// Design Name:

-

// Module Name: seq_det_moore_tb

-

// Project Name:

-

// Target Devices:

-

// Tool Versions:

-

// Description:

-

//

-

// Dependencies:

-

//

-

// Revision:

-

// Revision 0.01 - File Created

-

// Additional Comments:

-

//

-

//

-

-

-

module seq_det_mealy_tb;

-

reg clk,reset;

-

reg din;

-

wire dout;

-

reg [20:0] din_mid;

-

integer i;

-

-

// Note: CLK must be defined as a reg when using this method

-

-

parameter PERIOD = 10;

-

-

always begin

-

clk = 1'b0;

-

#(PERIOD/2) clk = 1'b1;

-

#(PERIOD/2);

-

end

-

-

initial begin

-

-

reset = 1'b1;

-

din_mid = 21'b110111010110100101101;

-

-

# 20

-

reset = 1'b0;

-

-

din = 1'b0;

-

for(i = 0;i < 21;i = i + 1)

-

begin

-

#PERIOD

-

din = din_mid[i];

-

end

-

-

end

-

-

seq_det_mealy uu1(.clk(clk),.reset(reset),.din(din),.dout(dout));

-

-

-

endmodule

行为仿真波形图:

这篇博文是在上篇博文的基础上改的,相对而言, 意义就没有那篇博文有意义!

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/85798105

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)