GT Transceiver的复位与初始化(3)TX初始化和复位流程

TX初始化与复位过程

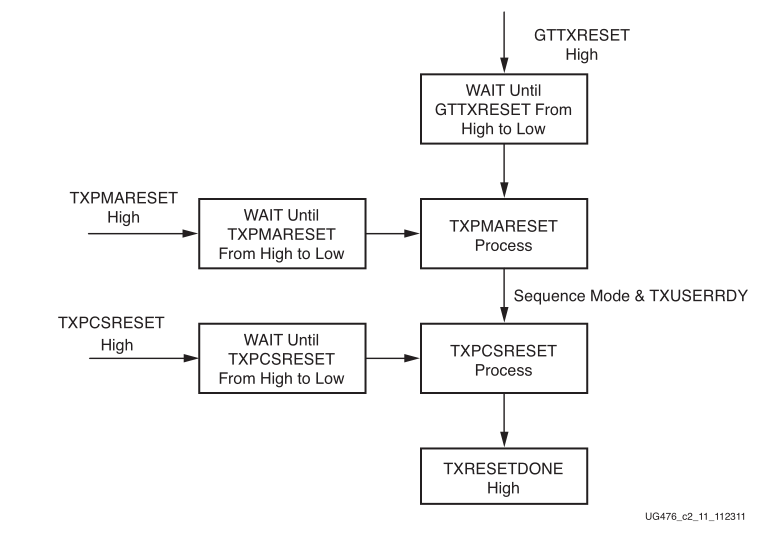

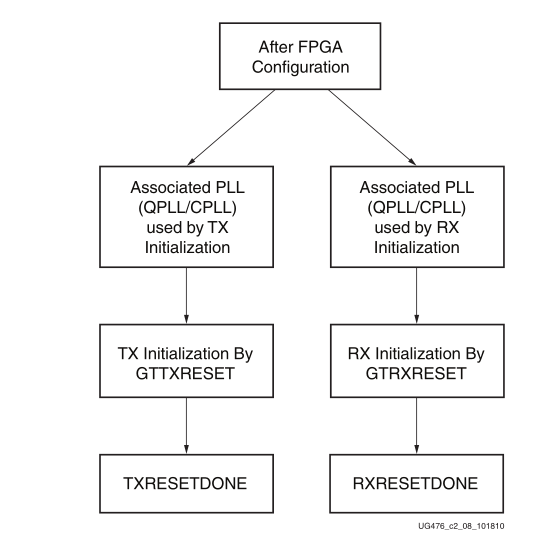

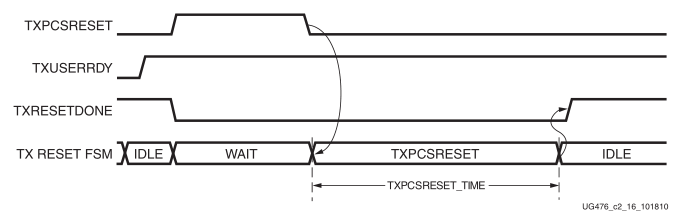

GTX/GTH收发器TX使用一个复位状态机来控制复位过程。GTX/GTH收发器TX被划分为两个复位区域,TX PMA和TX PCS。该分区允许TX初始化和复位只在顺序模式下操作,如下图所示:

初始化TX必须在顺序模式下使用GTTXRESET。激活GTTXRESET输入可以自动触发一个完整的异步TX复位。复位状态机执行复位顺序,其覆盖整个TX PMA和TX PCS。

在正常工作期间,当需要时,顺序模式允许用户从激活TXPMARESET开始复位TX,并继续执行复位状态机,直到TXRESETDONE从低电平转换为高电平。

TX复位状态机在检测到TXUSERRDY为高电平时才会复位PCS。用户应在满足如下这些条件后将TXUSERRDY驱动为高电平。

-

当使用PLL或MMCM时,应用程序使用的所有时钟,包括TXUSRCLK/TXUSRCLK2都显示为稳定或锁定。

-

用户接口准备好向GTX/GTH收发器传输数据。

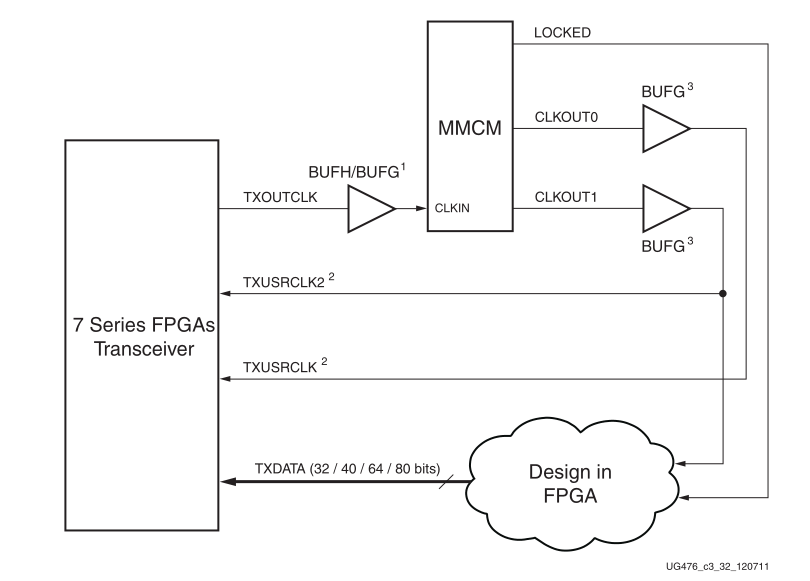

看完这段描述想说的是:TXUSERRDY 是TX的一个输入端口,当TXUSRCLK和TXUSRCLK2稳定时,该端口由用户的应用驱动为高电平。例如,如果一个MMCM被用来产生TXUSRCLK和TXUSRCLK2,那么这里可以使用MMCM锁定信号。

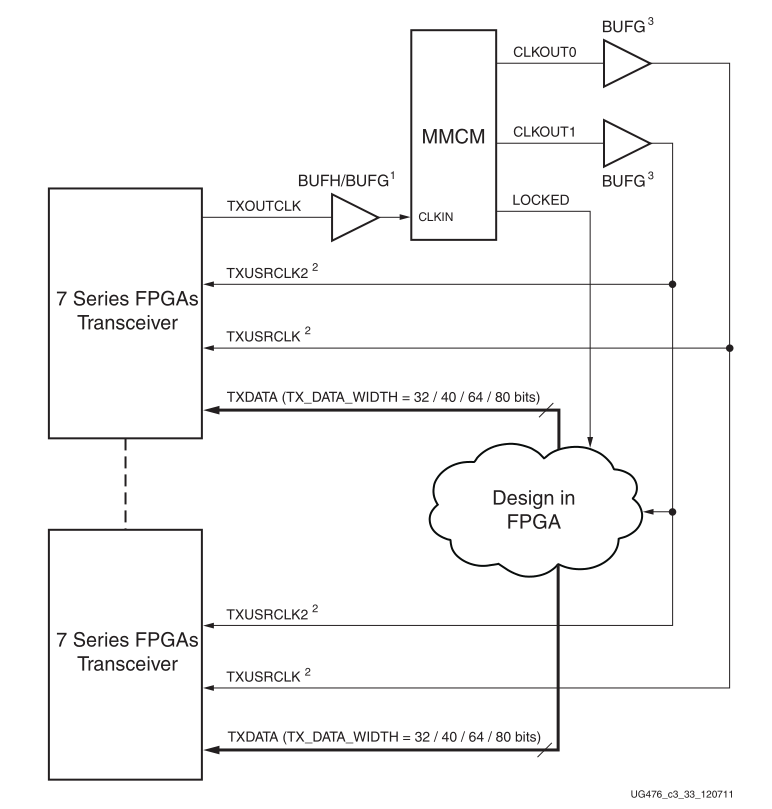

这里说的MMCM是文章《GT Transceiver中的重要时钟及其关系(7)TXUSRCLK以及TXUSRCLK2的产生》中提到的:

或:

中驱动TXUSERCLK的MMCM,时钟稳定后LOCKED会拉高,其可作为TXUSERRDY 。

GTX/GTH收发器在完成配置后的复位

FPGA配置完成后,需要满足下面的条件才能开始顺序复位状态机:

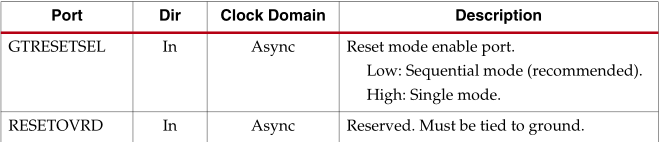

- GTRESETSEL必须拉低以启用顺序模式(见文章:《GT Transceiver的复位与初始化(1)Transceiver复位的两种类型和两种模式》)

-

必须使用GTTXRESET。

-

在整个复位过程中,TXPMARESET和TXPCSRESET必须在TXRESETDONE被检测到高电平之前被持续驱动为低电平。

-

GTTXRESET不能被驱动为低电平,直到相关的PLL被锁定。

如果复位模式在配置时被默认为顺序模式,那么C/QPLLRESET和GTTXRESET可以在配置完成后等待至少500 ns后有效。

如果复位模式默认为单一模式,那么用户必须:

-

配置完成后至少要等待500 ns。

-

将复位模式改为顺序模式。

-

再等待300-500 ns。

-

使能C/QPLLRESET和GTTXRESET。

注意:这里为什么会提到C/QPLLRESET呢?这是因为CPLL或QPLL需要先进行复位:

文章:《GT Transceiver的复位与初始化(1)Transceiver复位的两种类型和两种模式》开头就已提到:

可见,FPGA配置完成后,需要先进行相关PLL复位,之后进行TX复位。

C/QPLLRESET和GTTXRESET也有一个先后顺序,C/QPLLRESET在先,GTTXRESET在后。

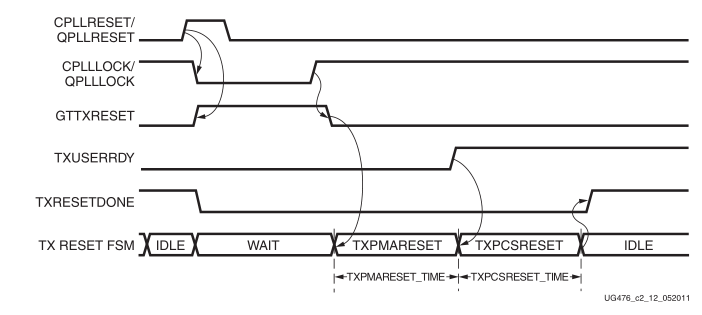

TX复位的时序如下:

建议使用CPLLL或QPLL的相关PLLLOCK将GTTXRESET从高电平释放到低电平,如上图所示。TX复位状态机在检测到GTTXRESET为高电平时等待,直到GTTXRESET被释放为低电平, 启动复位序列。

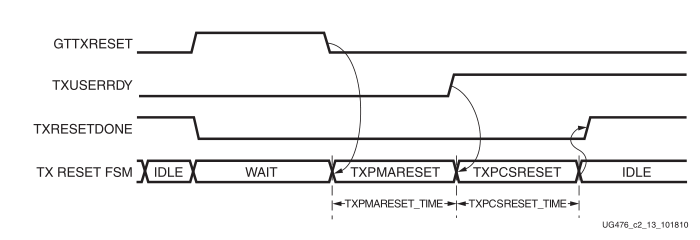

响应GTTXRESET脉冲的GTX/GTH收发器TX复位

GTX/GTH收发器允许用户在任何时候通过发送GTXRESET的高电平有效脉冲来完全复位整个TX。

TXPMARESET_TIME和TXPCSRESET_TIME可以静态设置或通过DRP端口重新编程,以调整应用GTTXRESET前所需的复位时间。

使用GTTXRESET时必须满足这些条件:

-

GTRESETSEL必须被驱动为低电平以使用顺序模式。

-

在整个复位过程中,TXPMARESET和TXPCSRESET必须在TXRESETDONE被检测到高电平之前被持续驱动为低电平。

-

相关的PLL必须指示锁定。

-

该异步GTTXRESET脉冲宽度的指导原则是参考时钟的一个周期。

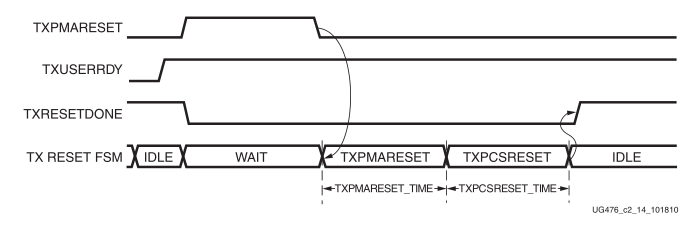

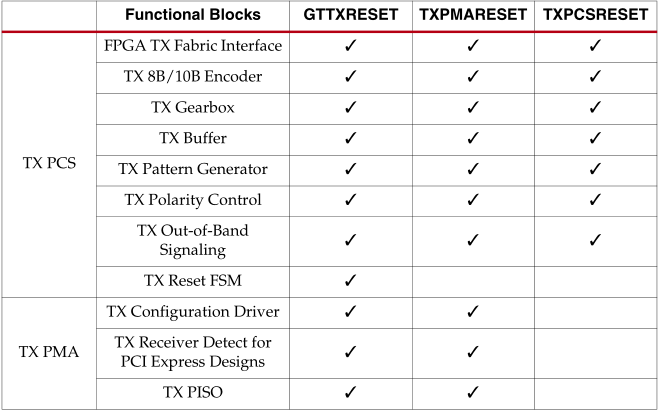

TX 组件复位

TX PMA和TX PCS可以单独复位。在TXPMARESET或TXPCSRESET过程中,GTTXRESET必须保持为低电平才能完成。

将TXPMARESET从高电平驱动到低电平开始PMA复位过程。

在TXPMARESET过程中,TXPCSRESET必须被持续驱动为低电平。

在顺序模式下,如果TXUSERRDY为高电平,复位状态机在完成PMA复位后自动启动PCS复位。

当TXUSERRDY为高电平时,将TXPCSRESET从高电平驱动到低电平开始PCS复位过程。

当PCS处于复位过程时,TXPMARESET必须被持续驱动为低电平。

在 顺序模式下,复位状态机只对PCS进行复位。

TX复位总结

下表总结了GTX/GTH收发器TX可用的所有复位以及在顺序模式下受其影响的组件。

在顺序模式下使用TXPMARESET可以重置GTTXRESET所涵盖的一切,除了TX复位状态机。

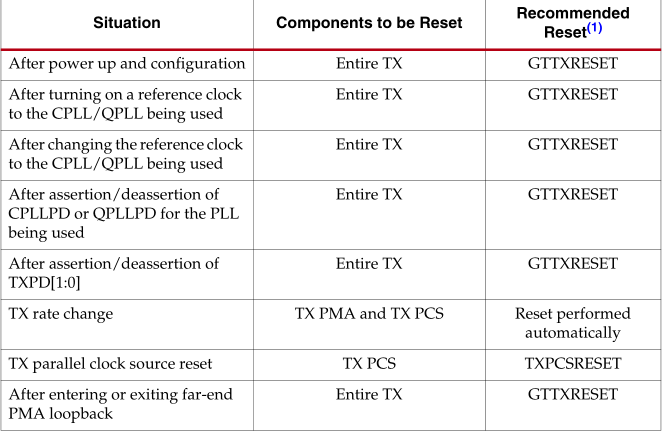

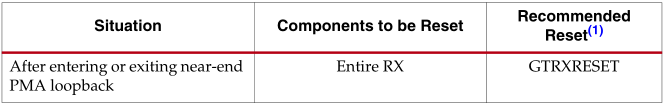

在不同场景下推荐使用的复位方式:

可见:

- 在上电配置完成后,需要对整个TX进行复位。

- 如果参考时钟改变或GTX/GTH收发器在配置后上电,GTTXRESET应在PLL完全完成其复位程序后有效。

- 每当PLL的参考时钟输入被改变时,PLL必须在之后复位,以确保它锁定在新的频率上。GTTXRESET应该在PLL完全完成其复位程序后有效

- 当正在使用的CPLL或QPLL在断电后回到正常工作状态时,必须对PLL进行复位。GTTXRESET应该在PLL完全完成其复位程序后有效。

- 在TXPD信号失电后,GTTXRESET必须有效。

- 当TX速率改变时,所需的复位序列会自动执行。当TXRATEDONE有效时,它表明速率变化和必要的复位序列都已应用并完成。如果TX buffer被启用,TXBUF_RESET_ON_RATE_CHANGE属性应被设置为TRUE,以允许TX缓冲器在速率改变后自动复位。如果使用TX buffer旁路模式,在TXRATEDONE有效后必须重复对齐。

- 驱动TXUSRCLK和TXUSRCLK2的时钟必须是稳定的,以便正确操作。这些时钟通常由FPGA中的MMCM驱动,以满足相位和频率要求。如果MMCM失去锁定并开始产生不正确的输出,应在时钟源重新锁定后有效TXPCSRESET。如果使用TX缓冲器旁路模式,在完成复位程序后必须重复对齐。

注意:上面提到的所有的有效,指的是触发条件有效,例如GTTXRESET有效,指的是一个高脉冲,触发TX复位。

往期回顾

GT Transceiver的复位与初始化(2)CPLL复位以及QPLL复位

GT Transceiver的复位与初始化(1)Transceiver复位的两种类型和两种模式

GT Transceiver中的重要时钟及其关系(10)RXOUTCLK的来源及其生成

GT Transceiver中的重要时钟及其关系(9)RXUSERCLK和RXUSER_CLK2的生成

GT Transceiver中的重要时钟及其关系(8)TXOUTCLK的来源及其产生

GT Transceiver中的重要时钟及其关系(7)TXUSRCLK以及TXUSRCLK2的产生

GT Transceiver中的重要时钟及其关系(6)TXUSRCLK以及TXUSRCLK2的用途与关系

GT Transceiver中的重要时钟及其关系(5)QPLL的工作原理介绍

GT Transceiver中的重要时钟及其关系(4)CPLL的工作原理介绍

GT Transceiver中的重要时钟及其关系(3)多个外部参考时钟使用模型

GT Transceiver中的重要时钟及其关系(2)单个外部参考时钟使用模型

GT Transceiver中的重要时钟及其关系(1)GT Transceiver参考时钟

FPGA的设计艺术(8)最佳的FPGA开发实践之严格遵循过程

高速串行总线设计基础(六)揭秘SERDES高速面纱之数据包与参考时钟要求

高速串行总线设计基础(八)揭秘SERDES高速面纱之CML电平标准与预加重技术

TCL中Ports/Pins/Nets/Cells/Clocks之间的交互关系?

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/120982787

- 点赞

- 收藏

- 关注作者

评论(0)