【FPGA】SRIO IP核的三层协议的作用?

SRIO这种高速串口复杂就复杂在它的协议上,三层协议:逻辑层,传输层以及物理层。

数据手册会说这三层协议是干什么的呢?也就是分工(【FPGA】SRIO IP核系统总览以及端口介绍(一)(User Interfaces 之 I/O Port)):

逻辑层定义整体协议和数据包格式。 这是端点启动和完成事务(transaction)所必需的信息。

传输层提供数据包从端点移动到端点所需的路由信息。

物理层描述了设备级接口细节,例如数据包传输机制,流控制,电气特性和低级错误管理。

这种划分提供了将新事务类型添加到逻辑规范的灵活性,而无需修改传输或物理层规范。

这种语言层次的描述貌似让人不太理解说了什么?

下面用图片来说明( 串行 RapidIO: 高性能嵌入式互连技术):

上图为4通道的SRIO数据传输原理图,如果要用单通道的话(FPGA端)在IP核定制的时候选择单通道即可。

数据从远程设备(假设为DSP的SRIO端)传输过来,FPGA端(假设我们这端为FPGA的SRIO端口)通过RX接收到串行数据,先到达物理层进行时钟恢复,串并转换,之后进行8b/10b解码操作、CRC校验,这一系列的操作都在物理层完成,之后进入传输层,进而到达逻辑层,我们需要的也是对逻辑层进行操作,对操作的对象正是逻辑层上的端口数据信息。

数据手册上说了,逻辑层定义了整体协议和数据包格式。

拿逻辑层上的IO口来说,有这样两对信号,ireq/iresp和treq/tresp;

假设我们这端是FPGA端,我们接收来自DSP端的数据,那FPGA端就是initiator,而DSP端就是target,这样的话,我们接收后需要处理的数据在FPGA上就是treq/tresp channel上的数据。

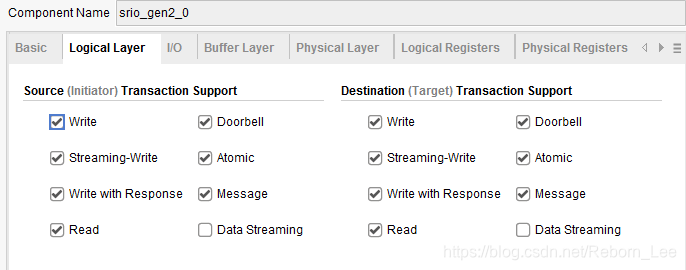

数据的发送是以包的形式发送的,而能发送以及接收到什么的包可以在IP核上定制(FPGA端)。

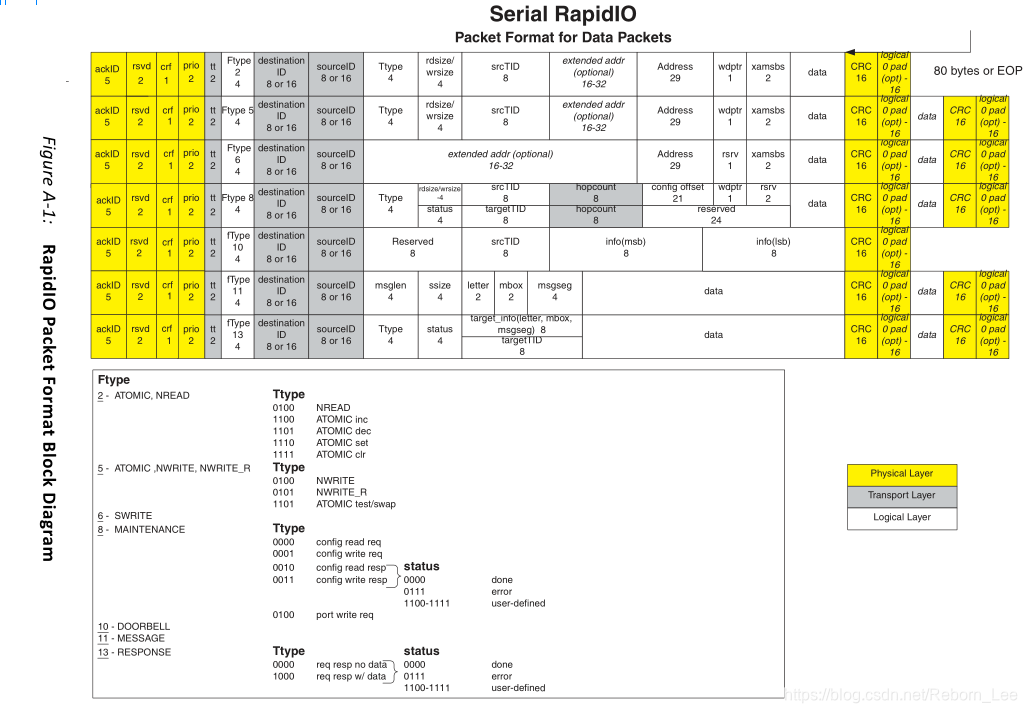

包的格式:

大概情况是这样的:

这个包是物理层上的包,我们使用SRIO IP核时,需要关注的包是逻辑层上的HELLO格式的包。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/91323617

- 点赞

- 收藏

- 关注作者

评论(0)