HDLBits 系列(16)Something about Counter

目录

原题复现

题目1

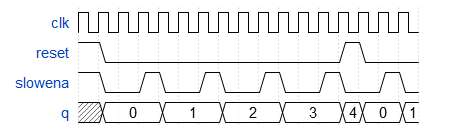

一般的计数器我就不说了,这里看下面的要求:

我的设计

也就是计数不仅由时钟控制,还需要判断计数使能是否有效,在这里就是slowena,下面就设计一个计数器技术从0到9,且计数由使能控制。

-

module top_module (

-

input clk,

-

input slowena,

-

input reset,

-

output [3:0] q);

-

always@(posedge clk) begin

-

if(reset) q <= 0;

-

else if(slowena & q < 9) q <= q + 1;

-

else if(slowena & q >= 9) q <= 0;

-

end

-

-

endmodule

题目2

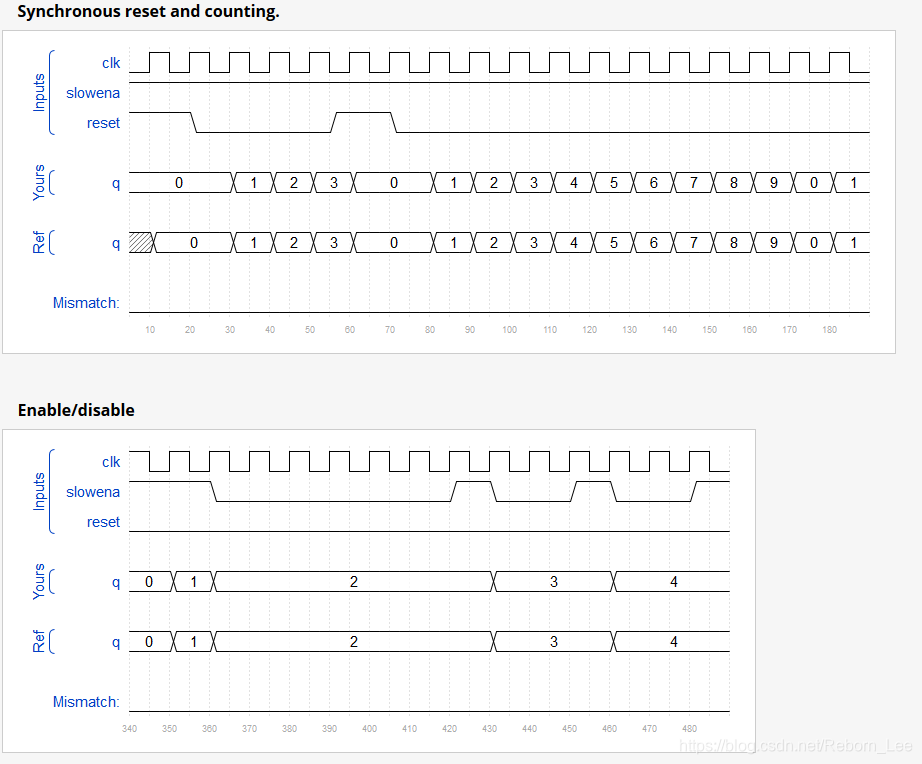

再来一题稍微更难一点的计数器相关的题目:

Design a 1-12 counter with the following inputs and outputs:

Reset Synchronous active-high reset that forces the counter to 1

Enable Set high for the counter to run

Clk Positive edge-triggered clock input

Q[3:0] The output of the counter

You have the following components available:

- the 4-bit binary counter (count4) below, which has Enable and synchronous parallel-load inputs (load has higher priority than enable). The count4 module is provided to you. Instantiate it in your circuit.

- logic gates

-

module count4(

-

input clk,

-

input enable,

-

input load,

-

input [3:0] d,

-

output reg [3:0] Q

-

);

Module Declaration

-

module top_module (

-

input clk,

-

input reset,

-

input enable,

-

output [3:0] Q,

-

output c_enable,

-

output c_load,

-

output [3:0] c_d

-

);

审题

如何设计这么一个计数器呢?

难点在于c_enable, c_load, c_d[3:0三个控制变量,我们先来看看他是什么意思吧。

这个计数器的功能是实现从1到12的计数,因此,如果复位reset有效,则计数复位为1,我们需要做的不是自己设计一个计数器,而是需要例化题目给的一个计数器,题目给的计数器需要有一个输入信号为load信号,我们需要产生一个load信号给予它,何时给予load信号有效呢?

当然是复位信号有效或者计数满(12)且计数使能有效;

因此,我们可以设计如下电路:

我的设计

-

module top_module (

-

input clk,

-

input reset,

-

input enable,

-

output [3:0] Q,

-

output c_enable,

-

output c_load,

-

output [3:0] c_d

-

); //

-

-

//4-bit计数器的控制信号

-

assign c_enable = enable;

-

//带复位和置位,

-

assign c_load = reset | (Q == 4'd12 & enable == 1'b1);

-

// assign c_d = c_load ? 4'b1: 4'bx;

-

-

assign c_d = 4'b1;

-

-

count4 inst_count4

-

(

-

.clk(clk),

-

.enable(c_enable),

-

.load(c_load),

-

.d(c_d),

-

.Q(Q)

-

);

-

-

endmodule

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/103230319

- 点赞

- 收藏

- 关注作者

评论(0)