GT Transceiver中的重要时钟及其关系(6)TXUSRCLK以及TXUSRCLK2的用途与关系

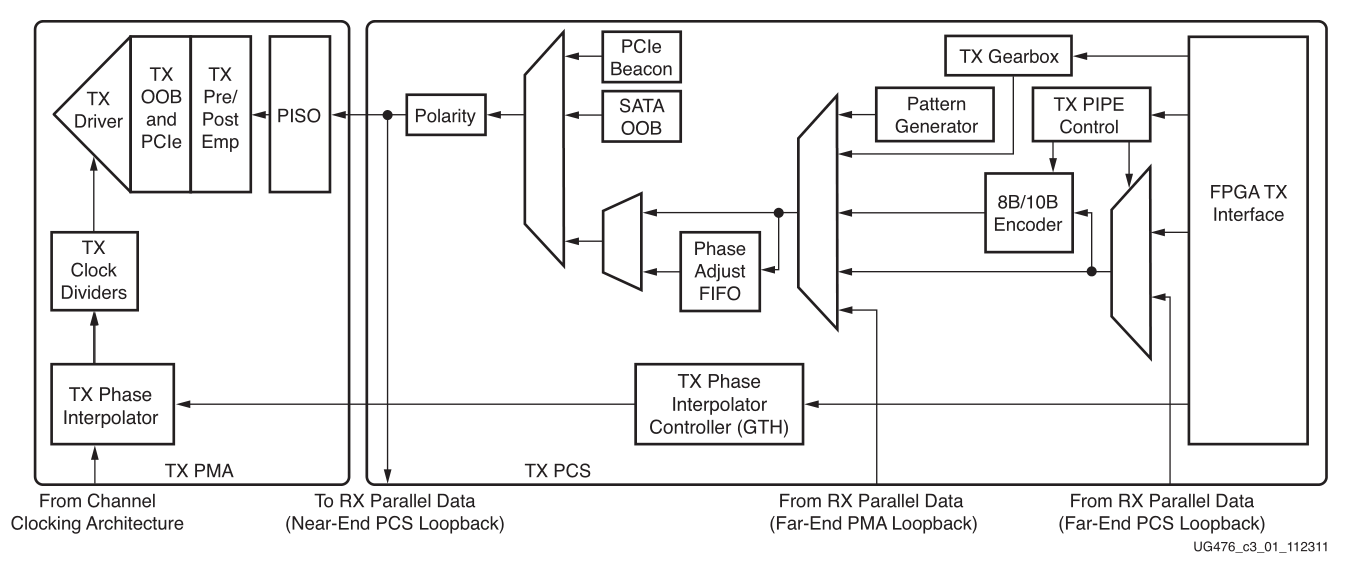

如下为transceiver的TX模块的结构框图:

今天内容不是介绍其内部各个结构的作用,而是介绍这里面存在时钟及其关系。

时钟仍然使我们今天的主题。

首先是框图的最右边FPGA TX Interface,即FPGA TX接口,它是FPGA通往GT Transceiver TX数据通路的通道。

The FPGA TX 接口包含两个并行时钟,TXUSRCLK a和TXUSRCLK2。

TXUSRCLK是GTX/GTH transceiver中PCS逻辑的内部时钟。

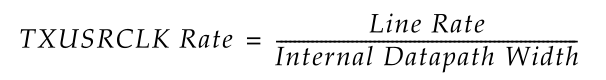

TXUSRCLK所需的速率取决于GTXE2_CHANNEL/GTHE2_CHANNEL源的内部数据通路宽度和GTX/GTH发射器的TX线速率。

下面公式显示了如何计算TXUSRCLK的所需速率。

TXUSRCLK2是进入GTX/GTH Transceiver TX端所有信号的主要同步时钟。

进入GTX/GTH Transceiver TX端的大多数信号都是在TXUSRCLK2的正沿上采样的。

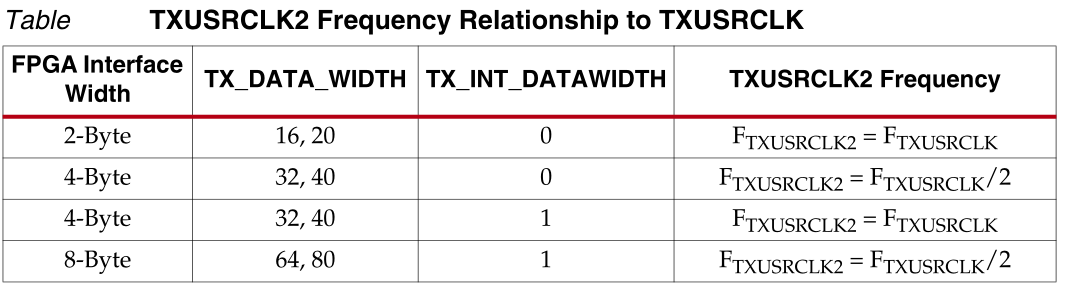

接口上的并行时钟(TXUSRCLK2)的速率由TX线路速率、TXDATA端口的宽度以及是否启用8B/10B编码决定。

TXUSRCLK2和TXUSRCLK有一个基于TX_DATA_WIDTH和TX_INT_DATAWIDTH设置的固定速率关系。

下显示了每个TX_DATA_WIDTH和TX_INT_DATAWIDTH值的TXUSRCLK2和TXUSRCLK之间的关系。

线路速率大于6.6Gb/s需要一个4字节的内部数据通路,将TX_INT_DATAWIDTH设置为1。

对于TXUSRCLK和TXUSRCL2,必须遵守这些关于时钟之间关系的规则。

- TXUSRCLK和TXUSRCLK2必须是正边对齐的,它们之间的偏移尽可能小。因此,低偏移的时钟资源(BUFG、BUFH、和 BUFR)应被用来驱动TXUSRCLK和TXUSRCLK2。

- 即使它们可能以不同的频率运行,TXUSRCLK、TXUSRCLK2和 Transmitter参考时钟必须有相同的振荡器作为其来源。因此 TXUSRCLK和TXUSRCLK2必须是发射器参考时钟的倍频或分频版本。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/120797957

- 点赞

- 收藏

- 关注作者

评论(0)