GT Transceiver的总体架构梳理

前言

对于7系列的FPGA,共有3个系列,每个系列都有各自的高速收发器,称为吉比特收发器,即Gigabit Transceiver,简称为GT。

每个系列的GT叫法略有不同,分别为:

- A7 的GTP

- V7的GTH

- K7的GTX

- 少量V7的GTZ

它们之间的区别在于最高线速率不同,GTZ>GTH>GTX>GTP.

结构大致相同。

正文

下面就K7而言, 梳理一下GTX Transceiver的结构。

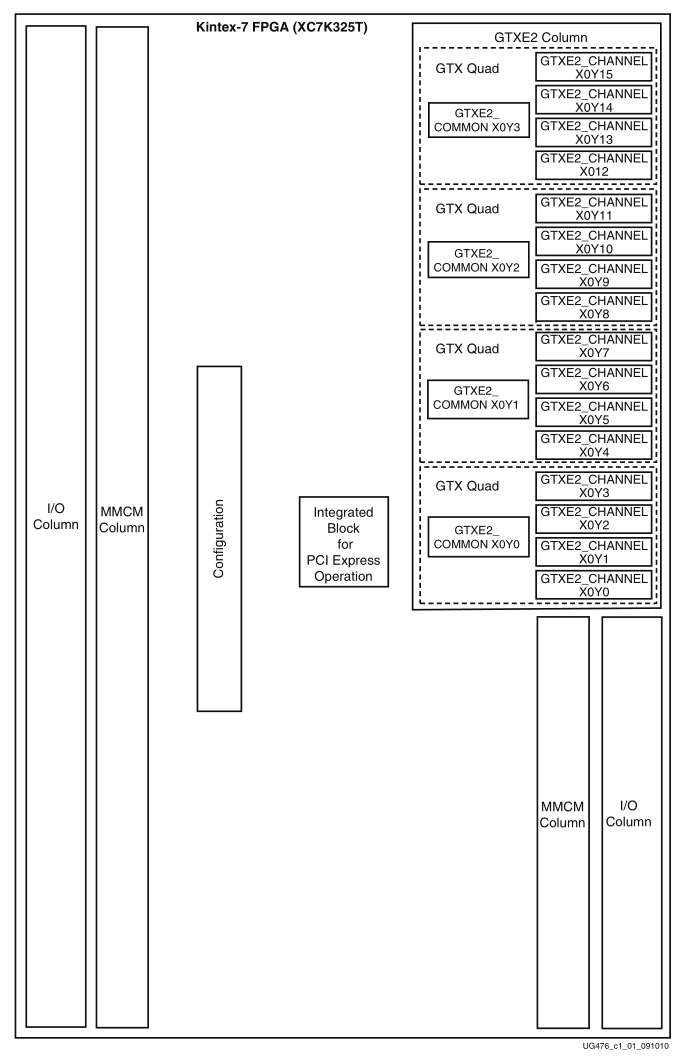

以XC7K325T为例,其包含总的Transceiver数量以及分布如下:

可见,一个K7325T FPGA的Transceiver总体架构是由

- 4个GTX QUAD,

- 每个GTX QUAD包含4个GTX Channel,故该FPGA包含16个GTX Channel,

- 也就说我们常说的,有16个GTX Transceiver。

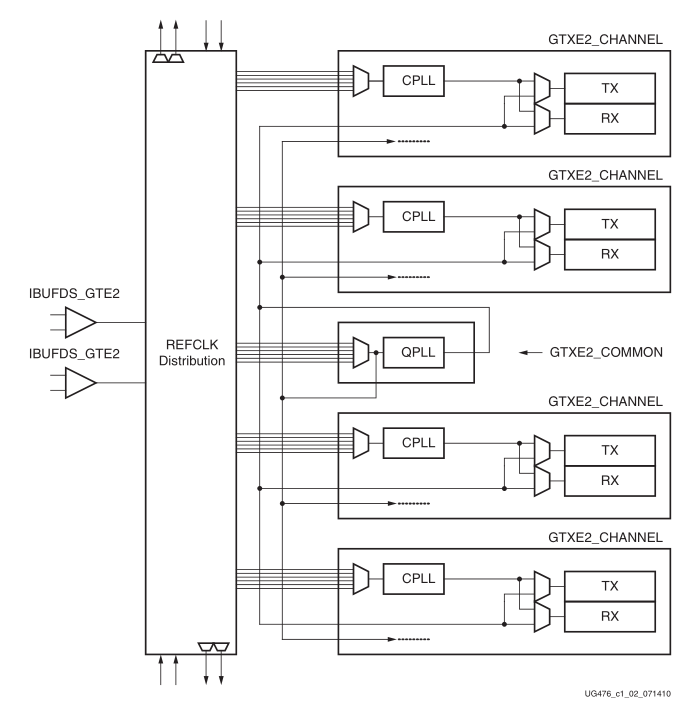

我们看它的GTX QUAD的组成,如下图:

可见, 它是由:

- 4个GTXE2_CHANNEL原语

- 1个GTXE2_COMMON原语

构成。

其中GTXE2_COMMON原语包含一个QPLL,之所以叫做QPLL,其中的Q含义就是QUAD,即一个GTX QUAD公用的PLL。

每一个GTXE2_CHANNEL原语由:

- 1个Channel PLL,即CPLL

- 1个Transmitter

- 1个Receiver

组成。

之所叫叫CPLL,即Channel PLL,含义是每一个Channel单独拥有的PLL。

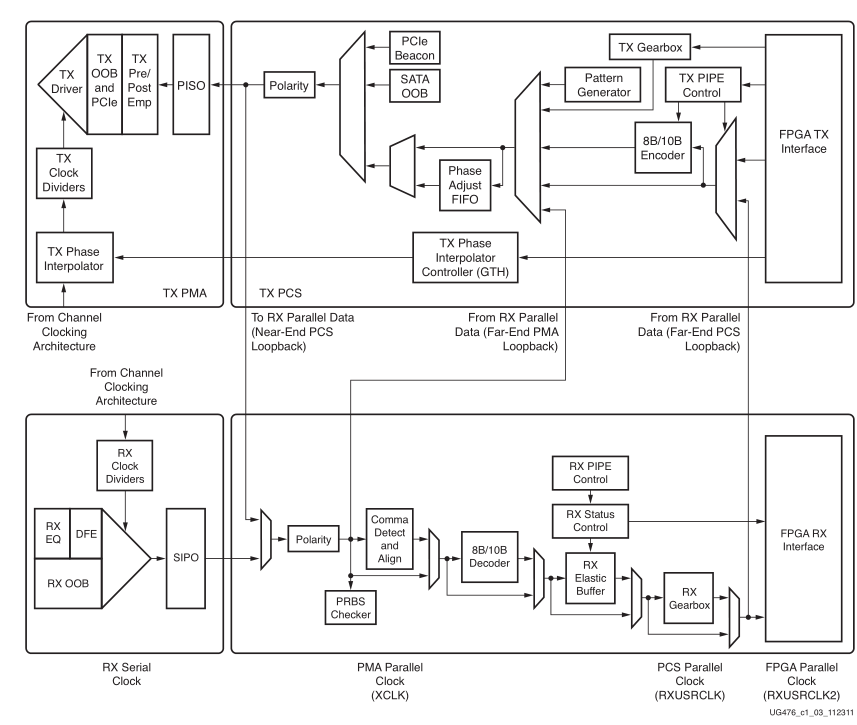

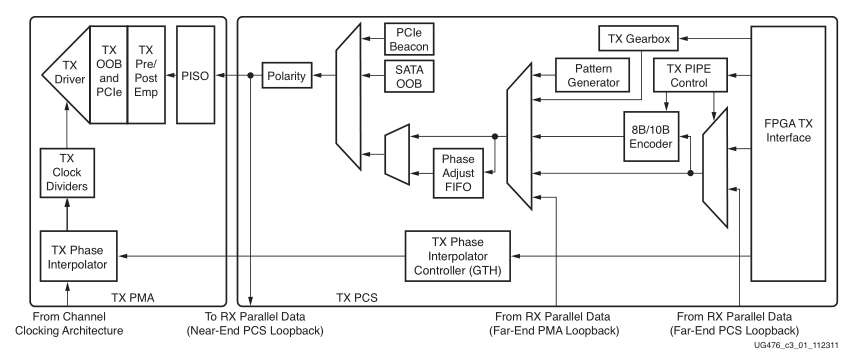

如下图为GTXE2_CHANNEL原语的拓扑结构:

注意:图中仅画出了Transmitter以及Receiver的结构,并未给出CPLL。

图中上半部分为Transmitter的结构,可见其由:

- PCS

- PMA

组成。

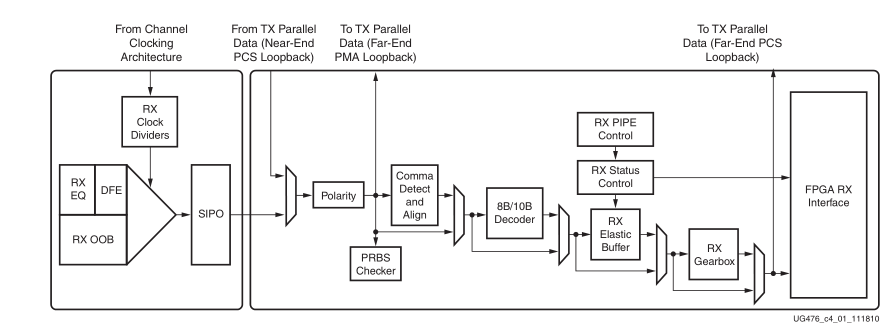

同理,Receiver也是由:

- PCS

- PMA

构成。

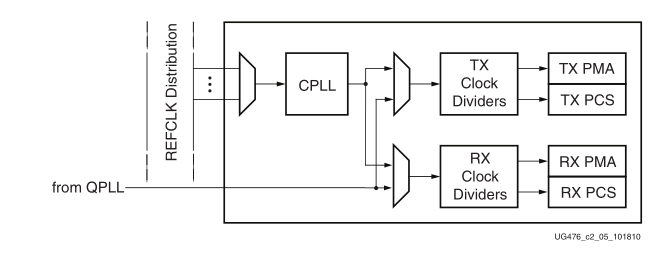

PCS以及PMA使用的使用来源于CPLL或者QPLL,经过分频提供给PCS以及PMA,如下图:

Transmitter的数据流大致为:

FPGA用户逻辑的数据,进入FPGA TX接口,进入PCS,再经过PMA,转换为高速串行数据输出。

Receiver的数据流大致为:

数据由PMA部分结构,转换为并行数据进入PCS,再经过RX接口输出给FPGA用户逻辑处理。

如下图示:

好了,本文系大致梳理总体结构,细节不易过多,更多内容见下集剖解。

参考文献

https://www.xilinx.com/support/documentation/user_guides/ug476_7Series_Transceivers.pdf

https://www.xilinx.com/support/documentation/user_guides/ug482_7Series_GTP_Transceivers.pdf

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/120662183

- 点赞

- 收藏

- 关注作者

评论(0)