智能卡接口芯片解决方案

一、基本概述

HCM8035是一款简洁且低成本的智能IC卡模拟接口芯片。内嵌升压模块,支持5V,3V,1.8V全电压读写。具有全面的安全保护机制,包括ESD保护,端口短路保护,电源上掉电保护。外围元件数目少,采用QFN32L封装。

今天开始介绍自己最近在调试和应用的产品,智能卡接口芯片,主要应用于一些需要智能卡的场合,通常处于控制器和卡端设备之间,起一个桥梁的作用。IC 银行卡支付、电子支付、银行卡、身份证、电视机支付、SIM卡接口等等。

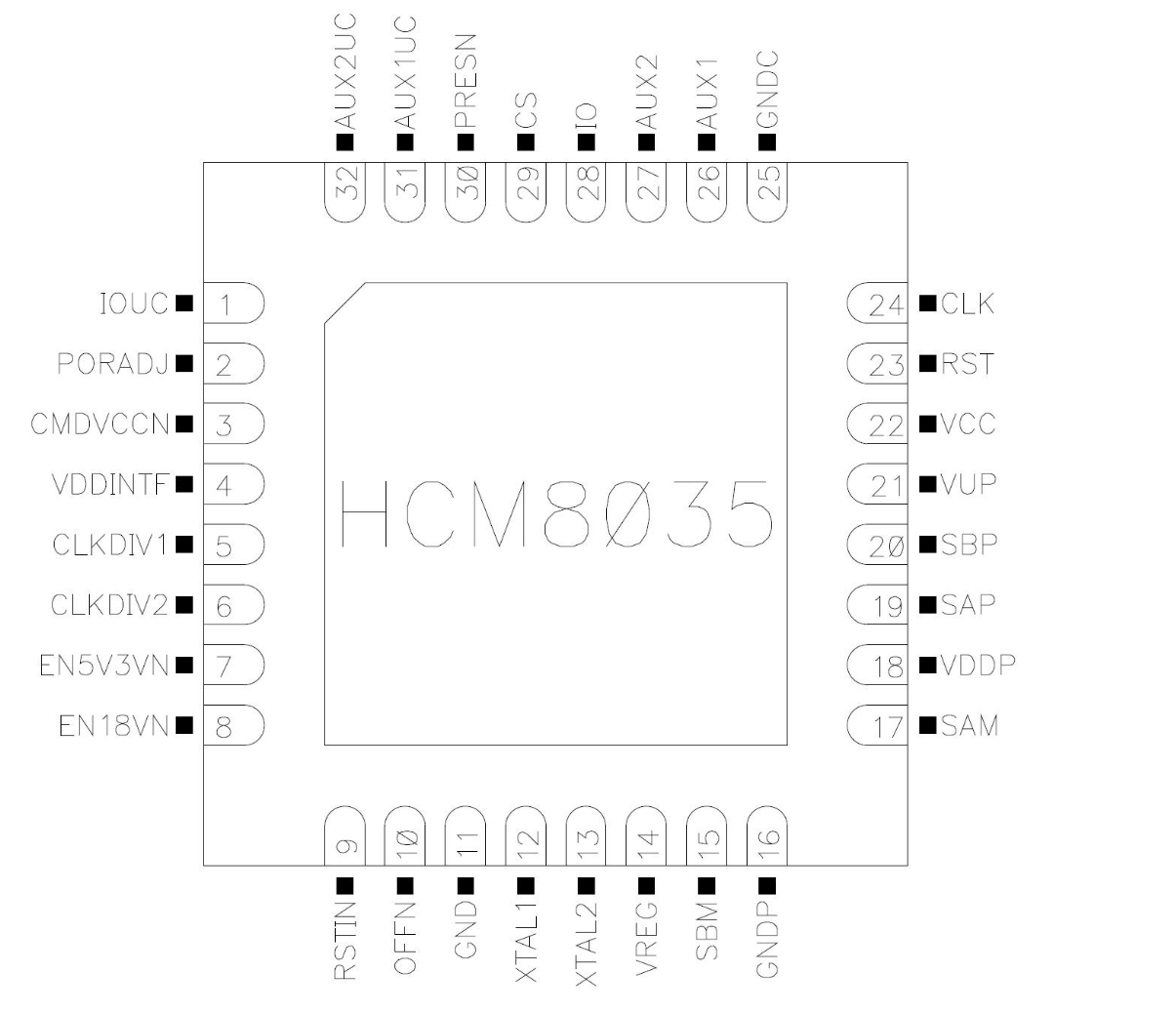

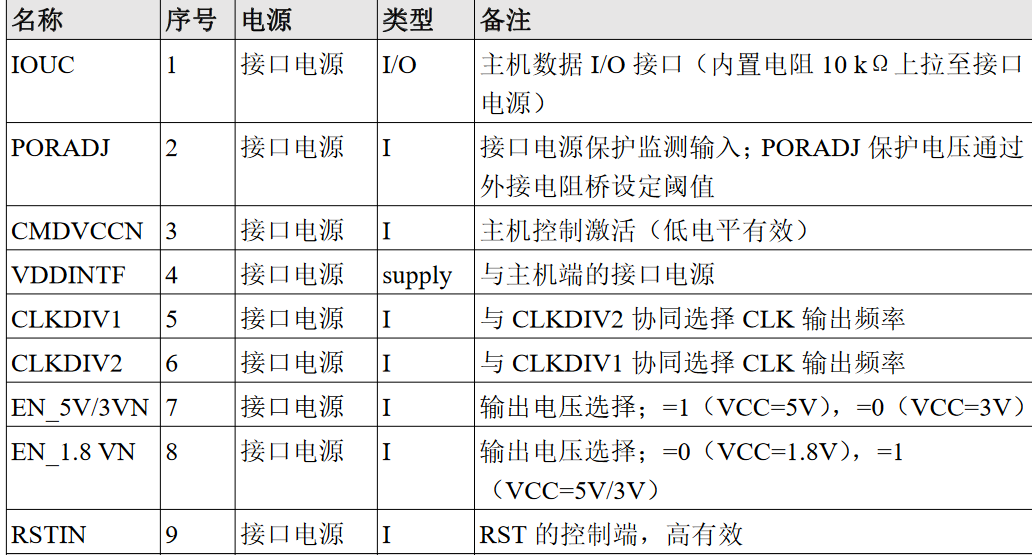

二、引脚定义

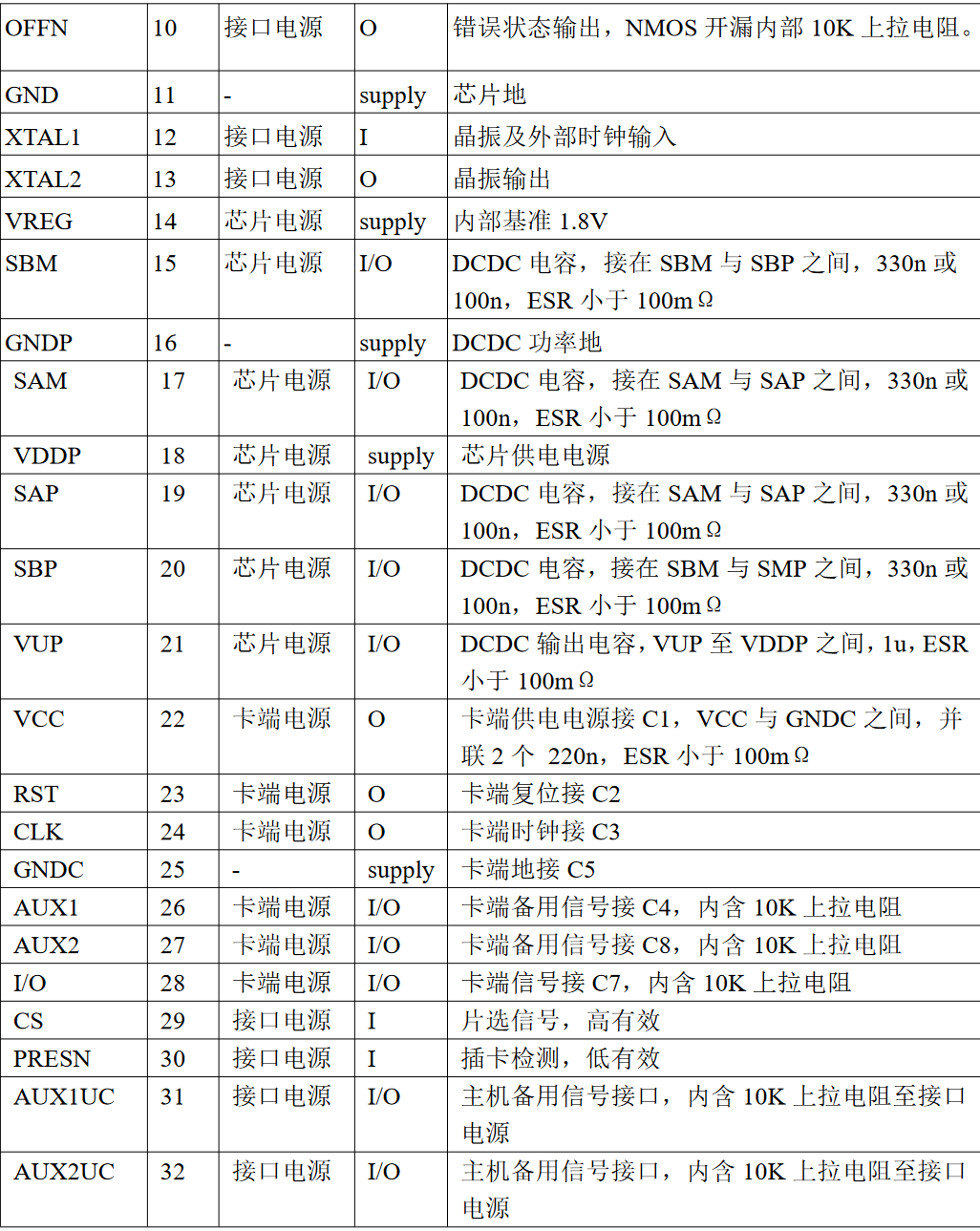

三、典型应用电路

四、功能模块

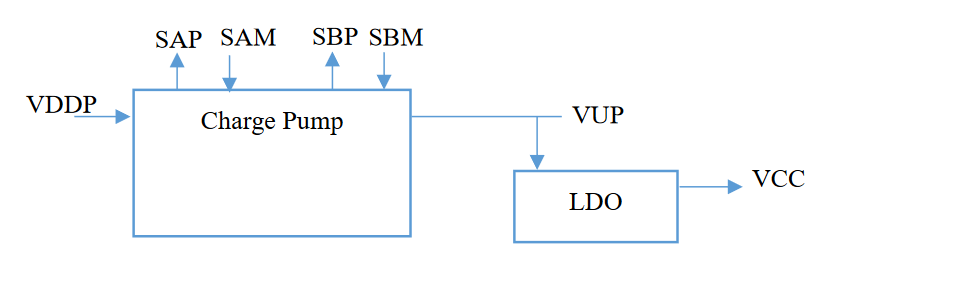

供电模块

VDDP 为芯片供电电源(2.7~5V)

控制接口电源 VDD(INTF)所有控制端的 I/O 电源均上拉至 VDD(INTF)

内部产生参考电压 VREG(1.8)

上电时,OFFN 保持低电平,直到 CMDVCCN 变高且 PRESN 变低为止。

掉电时,OFFN 会在 VDDP 跌过阈值电压后才变低。

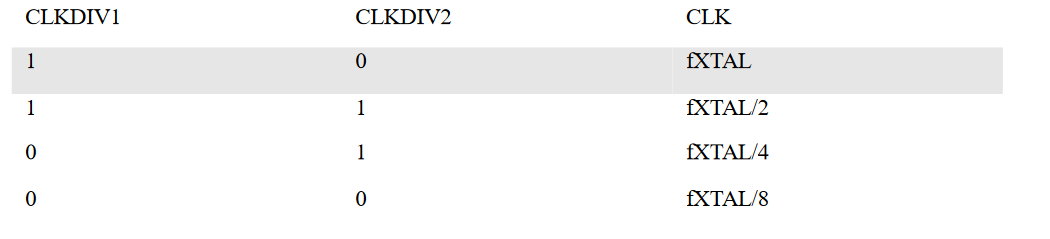

智能卡未激活时,CMDVCCN 拉高,将使用内部振荡器,工作在低频模式省电。

电源部分包含 DCDC 电压转换器用于给智能卡提供电源 VCC(5、3、1.8)

电压监控模块

电压监控模块用于电源上电复位以及读卡器件电源掉电。监管芯片内部 VDDP 与 VREG,

接口电源电压 VDD(INTF)通过 PORADJ 引脚分压来检测。

VDDP、VREG、VDD(INTF)电压监控信号会发送给逻辑控制部分参与控制芯片复位

时钟电路模块

智能卡时钟 CLK,可以使用外部时钟通过 XTAL1 送入,也可以使用晶振通过 XTAL1 和

XTAL2 送入,如果 XTAL1 有外部时钟会优先采用,无需控制。

有 CMDVCCN 下降沿启动时钟自动选择机制,在内部时钟运行的状态下,首先判断是否有

外部时钟,如果有外部时钟则采用外部时钟,如没有则启动晶振。使用外部时钟时,应当在

CMDVCCN 下降沿前启动外部时钟。

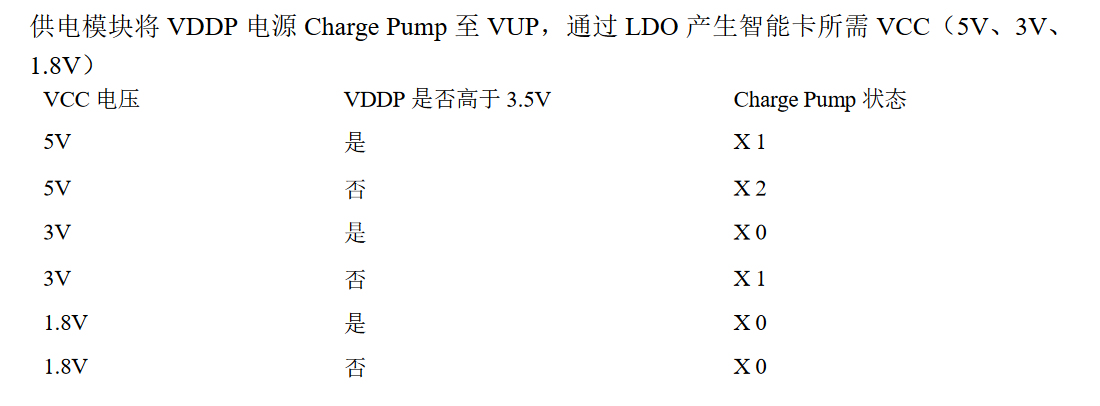

通过 CLKDIV1 与 CLKDIV2 选择使用频率为 fXTAL、fXTAL/2、fXTAL/4、fXTAL/8

时钟操作为同步的,不会有小于 45%最小时钟周期的脉冲出现,这样可以确保开始和最后

一个时钟的正确性。

CLK 时钟占空比在 45%~55%之间

I/O电路模块

三条数据接口 I/O、AUX1、AUX2 是相同的

内置上拉电阻 10KΩ上拉至各自的电源

允许两边电源不相同

最先收到下降沿的那边为主端

经过 200ns 延迟后主端将 0 信号传送至从端

当主端回到逻辑 1,从端传送逻辑 1 等待 200ns 后,两端再次进入对等状态

80pF 负载拉高到 0.9 VCC 电压时将提供大于 1mA 的电流,保证上拉信号在传输过程中足够

快速。

I/O 引脚电流限制为 15mA

最大频率 1.5MHz

片选控制模块

CS 为片选控制信号,当 CS 为高,芯片响应控制;当 CS 为低,CMDVCCN、RSTIN、CLKDIV1、

CLKDIV2、EN_5V/3VN、EN_1.8VN 锁定

I/OUC、AUX1UC、AUX2UC 设置为弱上拉模式停止信号从卡端传送。OFFN 三态输出。

休眠及深度休眠模式

上电后如果 CMDVCCN 拉高 则进入休眠模式,只有少量逻辑来激活唤醒。

1、所有与卡的连接失效(约与地呈 200 欧电阻)

2、I/OUC、AUX1UC、AUX2UC 呈弱上拉(10KΩ上拉至 VDD(INTF))

3、电压产生器不工作

4、电压监管模块仍生效

5、内部时钟处于低频工作模式

深度休眠模式启动需要 CMDVCCN 拉高同时

EN5V3VN 与 EN18VN 拉低时生效。深度休眠模式必须在读卡不需要进行是才可进入。在深度

休眠模式中所有的电路单元都将关闭。OFFN 将跟随 PRESN 的状态。变更三个控制信号的状

态将退出深度休眠模式

VCC电压源

VCC 电压源可以提供 65mA/35mA 缓冲电流(5V&3V/1.8V)

VCC 电源 125mA 过流保护

在上电过程中在 4ms 内(打开 IO 之前)允许 200mA

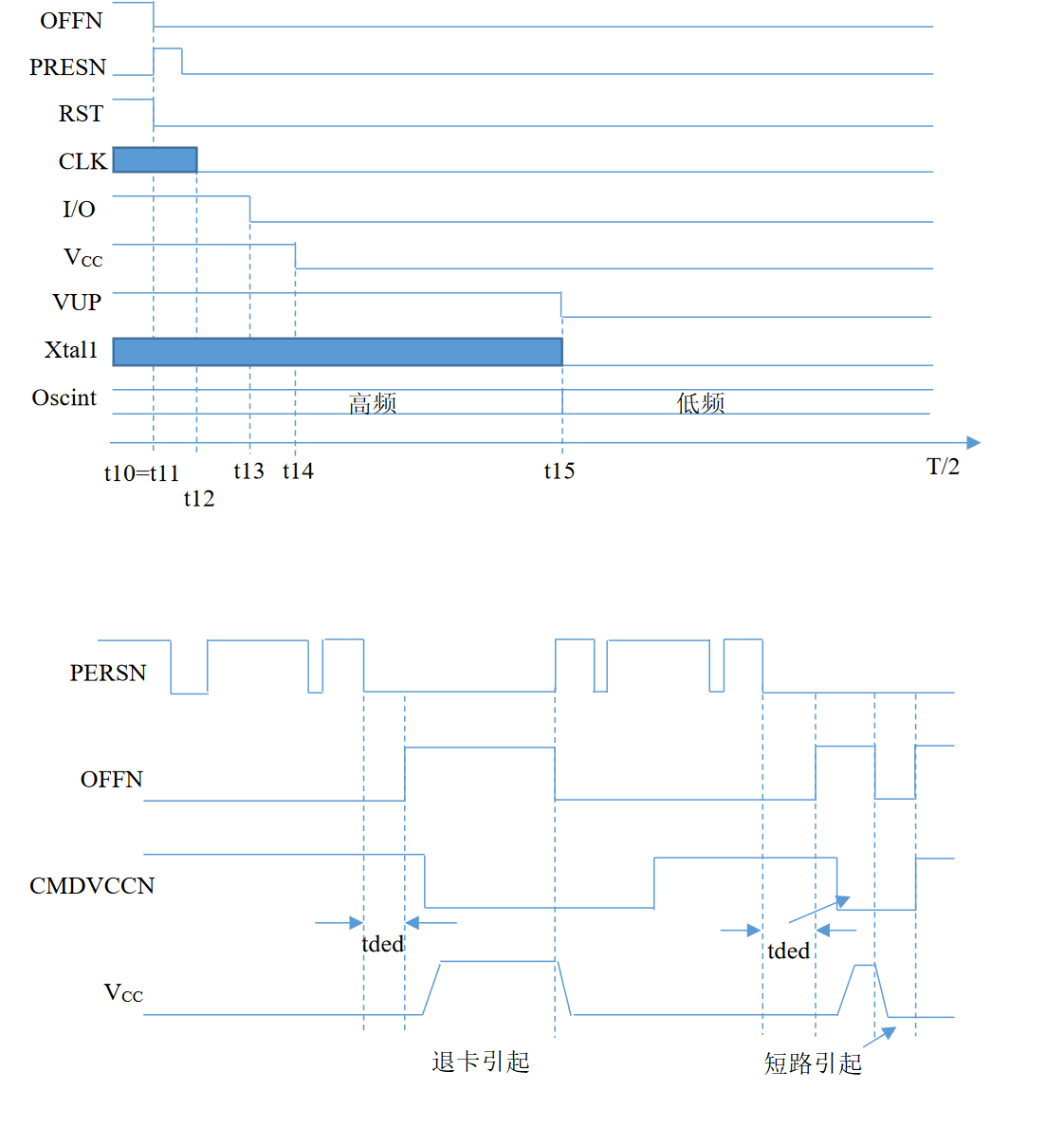

错误机制

发生以下错误则保护:

VCC 发生短路或过流

读取过程中卡被拔出

VDDP、VDD(INTF)或 Vreg 发生拉低

过热

有两种情况:

1、 CMDVCCN 处于高的状态(未在读卡周期):OFFN 在读卡时为高,不在读卡时为低,

电源监控模块会拉低 VDDP 重新进入复位,但是不会对 OFFN 进行上拉操作。未开启卡

供电,接口无短路,无过热。

2、 CMDVCCN 处于低的状态(正在读卡周期):OFFN 立即拉低,退出激活,直到 CMDVCCN

返回高。当没有错误发生后,OFFN 返回高。

- 点赞

- 收藏

- 关注作者

评论(0)