SR锁存器与D锁存器设计与建模

⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。

🔥文章和代码已归档至【Github仓库:hardware-tutorial】,需要的朋友们自取。或者关注公众号【AIShareLab】,回复 FPGA 也可获取。

锁存器和触发器的基本特性

锁存器和触发器是构成时序逻辑电路的基本逻辑单元,它们具有存储数据的功能。

每个锁存器或触发器都能存储1位二值信息,所以又称为存储单元或记忆单元。

若输入信号不发生变化,锁存器和触发器必然处于其中一种状态,且一旦状态被确定,就能自行保持不变,即长期存储1位二进制数。

电路在输入信号的作用下,会从一种稳定状态转换成为另一种稳定状态。

锁存器(Latch)与触发器(Flip Flop)的区别

锁存器(Latch)—— 没有时钟输入端,对脉冲电平敏感的存储电路,在特定输入脉冲电平作用下改变状态。

触发器(Flip Flop)——每一个触发器有一个时钟输入端。对脉冲边沿敏感的存储电路,在时钟脉冲的上升沿或下降沿的变化瞬间改变状态。

基本SR锁存器

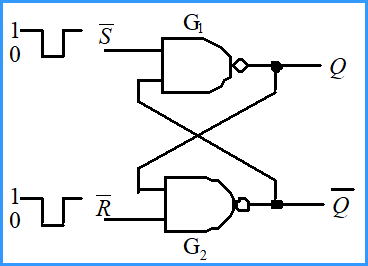

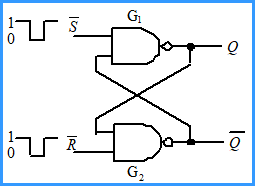

用与非门构成的基本SR锁存器

方框外侧输入端的小圆圈和信号名称上面的小横线均表示输入信号是低电平有效的,同时为了区别,这种锁存器有时也称为基本 SR 锁存器。

现态: , 信号作用前Q端的状态, 现态用 表示。

次态: $ \bar{R}$ 、 信号作用后Q端的状态, 次态用 表示。

a.电路图

b.功能表

约束条件:

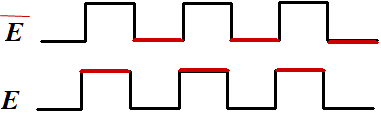

例 当S、R的波形如下图虚线上边所示,试画出Q和 Q对应的波形(假设原始状态Q=0 )。

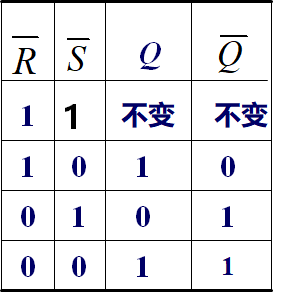

门控D锁存器

1.电路结构

国标逻辑符号

当

时,

,无论 D 取什么值, Q 保持不变。

当

时,使能信号有效

- 时, , , Q 被置 1 ;

- 时, , , Q 被置 0 。

在 期间, D 值将被传输到输出端 Q ,而当 E 由 1 跳变为 0 时,锁存器将保持跳变之前瞬间 D 的值。因此, 锁存器常 被称为透明锁存器 (Transparent Latch)。

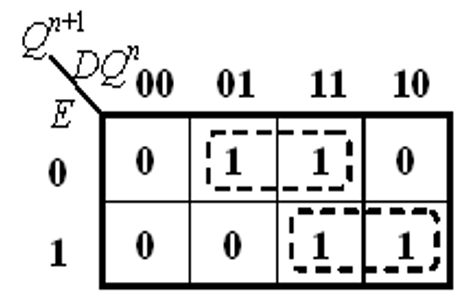

门控D锁存器特性表和特性方程

D锁存器的特性表

卡诺图

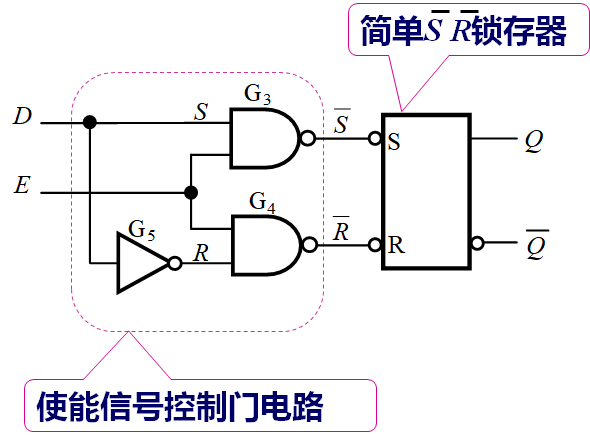

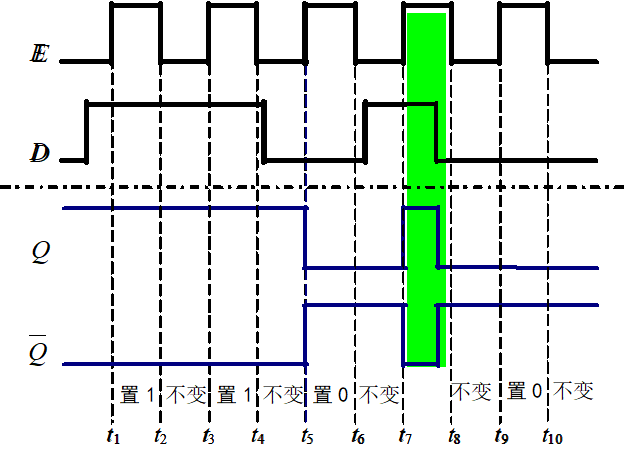

门控D锁存器波形图

初始状态为Q =1

门控D 锁存器的Verilog HDL建模

试对图所示的D锁存器进行建模。

//版本1: Structural description of a D latch

module Dlatch_Structural (E, D, Q, Q_);

input E, D ;

output Q, Q_;

wire R_, S_;

nand N1(S_, D, E);

nand N2(R_,~D, E);

SRlatch_1 N3(S_, R_, Q, Q_);

endmodule

//Structural description of a SR-latch

module SRlatch_1 (S_, R_, Q, Q_);

input S_,R_;

output Q, Q_;

nand N1(Q, S_,Q_);

nand N2(Q_,R_,Q );

endmodule

版本1的特点:

第一个版本根据图4.1.3使用基本的逻辑门元件,采用结构描述风格,编写了两个模块,这两个模块可以放在一个文件中,文件名为Dlatch_Structural.v。

在一个文件中可以写多个模块,其中有一个是主模块(或者称为顶层模块)。

文件名必须使用顶层模块名。本例中Dlatch_Structural是主模块,它调用SRlatch_1模块。

//版本2: Behavioral description of a D latch

module Dlatch_bh (E, D, Q, Q_);

input E, D;

output Q, Q_;

reg Q;

assign Q_ = ~Q;

always @(E or D)

if (E)

Q <= D; //当使能有效E=1时,输出跟随输入变化

else

Q <= Q; //当E=0时, Q保持不变

endmodule

版本2的特点:

第二个版本采用功能描述风格的代码,不涉及到实现电路的具体结构,靠“算法”实现电路操作。对于不太喜欢低层次硬件逻辑图的人来说,功能描述风格的Verilog HDL是一种最佳选择。其中“<=”为非阻塞赋值符,将在下一节介绍。

注意:

- always内部不能使用assign。

- 在写可综合的代码时,建议明确地定义if-else中所有可能的条件分支,否则,就会在电路的输出部分增加一个电平敏感型锁存器。

参考文献:

- Verilog HDL与FPGA数字系统设计,罗杰,机械工业出版社,2015年04月

- Verilog HDL与CPLD/FPGA项目开发教程(第2版), 聂章龙, 机械工业出版社, 2015年12月

- Verilog HDL数字设计与综合(第2版), Samir Palnitkar著,夏宇闻等译, 电子工业出版社, 2015年08月

- Verilog HDL入门(第3版), J. BHASKER 著 夏宇闻甘伟 译, 北京航空航天大学出版社, 2019年03月

欢迎关注公众号【AIShareLab】,一起交流更多相关知识,前沿算法,Paper解读,项目源码,面经总结。

- 点赞

- 收藏

- 关注作者

评论(0)