FPGA:逻辑功能的仿真与验证

【摘要】 ⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。🔥文章和代码已归档至【Github仓库:hardware-tutorial】,需要的朋友们自取。或者关注公众号【AIShareLab】,回复 FPGA 也可获取。HDL产生的最初动因就是为了能够模拟硬件系统,可...

⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。

🔥文章和代码已归档至【Github仓库:hardware-tutorial】,需要的朋友们自取。或者关注公众号【AIShareLab】,回复 FPGA 也可获取。

HDL产生的最初动因就是为了能够模拟硬件系统,可以分析系统的性能,验证其功能是否正确。

要测试一个设计块是否正确,就要用Verilog再写一个测试模块(Test Bench)。这个测试模块应包括以下三个方面的内容:

- 测试模块中要调用到设计块,只有这样才能对它进行测试;

- 测试模块中应包含测试的激励信号源;

- 测试模块能够实施对输出信号的检测,并报告检测结果;

写出测试模块的过程又称为搭建测试平台(Test Bench)

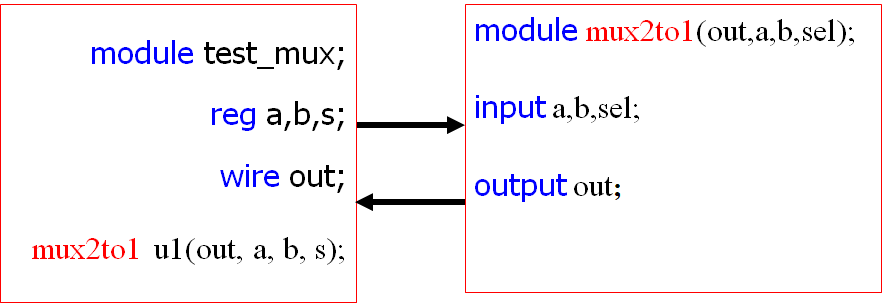

例:2选1数据选择器的测试模块

module test_mux;

reg a,b,s;

wire out;

mux2to1 u1(out, a, b, s);

initial

begin

a=0; b=1; s=0;

#10 a=1; b=1; s=0;

#10 a=1; b=0; s=0;

#10 a=1; b=0; s=1;

#10 a=1; b=1; s=1;

#10 a=0; b=1; s=1;

#10 $finish;

end

initial

$monitor($time, “a=%b b=%b s=%b out=%b”, a,b,s,out);

endmodule

module mux2to1(out,a,b,sel);

output out;

input a,b,sel;

wire selnot,a1,b1;

not (selnot, sel);

and (a1, a, selnot);

and (b1, b, sel);

or (out1, a1, b1);

endmodule

0 a=0 b=1 s=0 out=0

10 a=1 b=1 s=0 out=1

20 a=1 b=0 s=0 out=1

30 a=1 b=0 s=1 out=0

40 a=1 b=1 s=1 out=1

50 a=0 b=1 s=1 out=1

测试激励块(TB)与设计块(Design Block)之间的关系

仿真时,信号线a、b、s上要加一组测试激励信号,这组激励信号的产生,是通过initial内部的过程语句产生的,而过程语句只能给reg型变量赋值。

仿真时,信号线a、b、s上的激励信号是不能消失的,需要有“寄存”效应,能够描述这种“寄存”行为的,只能是reg型。

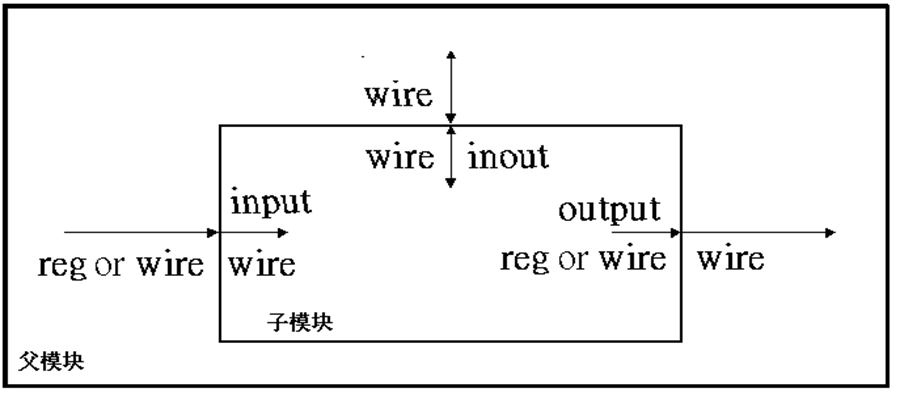

端口连接时有关变量数据类型的一些规定

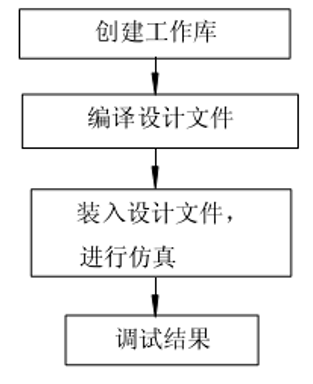

仿真过程简介

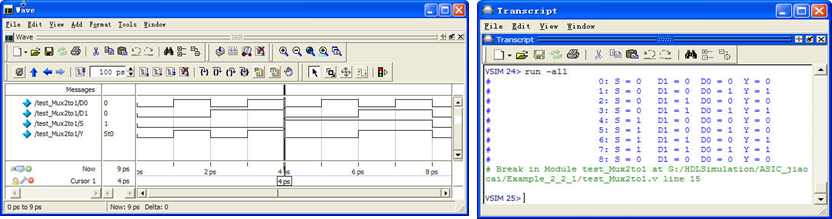

使用软件ModelSim-Altera 6.5b Starter Edition 进行仿真验证的大致过程

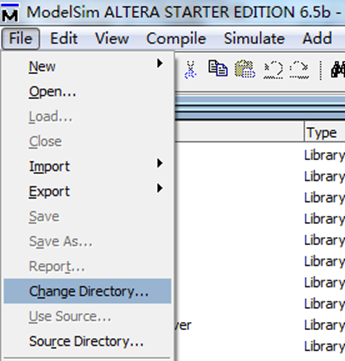

ModelSim仿真软件的使用

- 创建一个工作目录

- 输入源文件

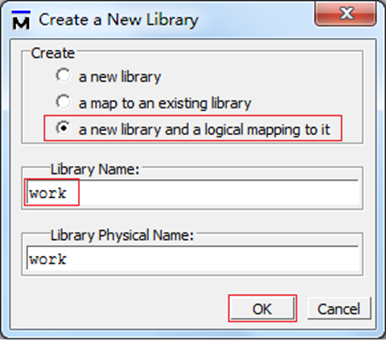

- 建立工作库

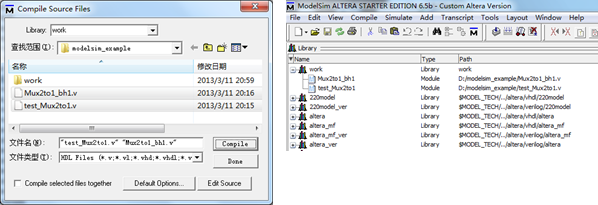

编译设计文件

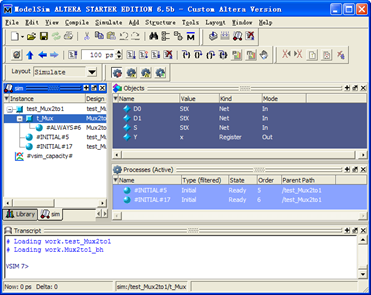

装入设计文件到仿真器

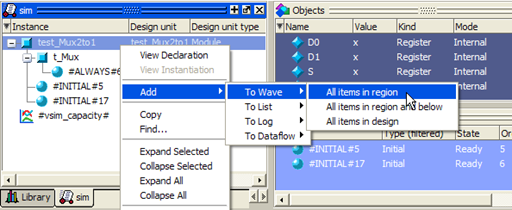

运行仿真器

欢迎关注个人公众号【AIShareLab】,一起交流更多相关知识,前沿算法,Paper解读,项目源码,面经总结。

【版权声明】本文为华为云社区用户原创内容,未经允许不得转载,如需转载请自行联系原作者进行授权。如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)