嵌入式:ARM的流水线技术

【摘要】 三级流水线ARM的组织 ARM的3级流水线介绍到ARM7为止的ARM处理器使用的简单3级流水线分别为取指级 :读取指令。译码级 :对指令进行译码。占有“译码逻辑”,不占有“数据路径”。执行级 :指令占有“数据路径”,寄存器堆栈被读取,操作数在桶式移位器中被移位,ALU产生相应的运算结果,并写回目的寄存器中。并根据需求更改状态寄存器的条件位。 ARM3级流水线下PC的行为在3级流水线的执行过...

三级流水线ARM的组织

ARM的3级流水线介绍

到ARM7为止的ARM处理器使用的简单3级流水线分别为

- 取指级 :读取指令。

- 译码级 :对指令进行译码。占有“译码逻辑”,不占有“数据路径”。

- 执行级 :指令占有“数据路径”,寄存器堆栈被读取,操作数在桶式移位器中被移位,ALU产生相应的运算结果,并写回目的寄存器中。并根据需求更改状态寄存器的条件位。

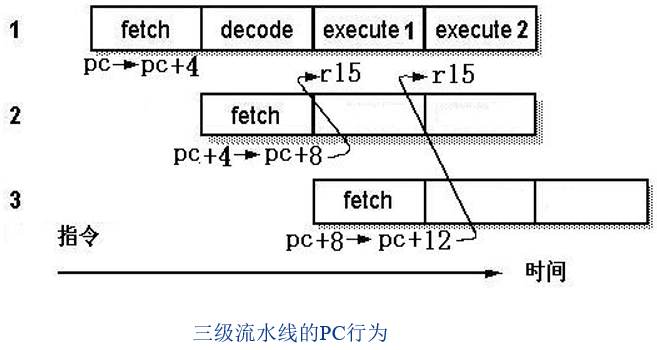

ARM3级流水线下PC的行为

在3级流水线的执行过程中,当通过R15寄存器直接访问PC时,必须考虑到此时流水线的执行过程的真实情况

程序执行时间计算公式

- :指令数 (固定)。

- CPI : 每条指令的平均时钟周期数。

- : 时钟频率。

减少Tprog的方法:

-

- 减少CPI: 将程序和数据分开

-

- 提高 : 增加流水数,简化每一级的逻辑。

五级流水线ARM的组织

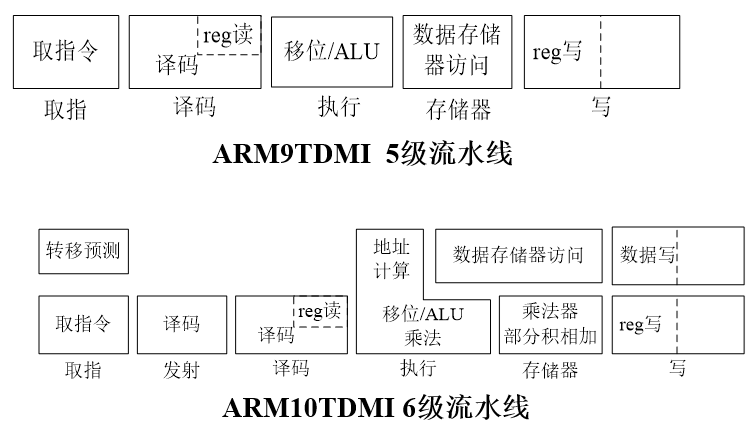

使用5级流水线的ARM处理器包含下面5个流水线级:

- 取指:取指令。

- 译码 :读取寄存器操作数,寄存器堆中有3个操作数读端口,大多数ARM指令能在一个周期内读取其操作数。

- 执行 :把一个操作数移位,并产生ALU结果,如果是Load/Store指令,在ALU中计算存储器地址。

- 缓冲\数据 :如果需要,则访问数据存储器,否则ALU的结果只是简单地缓冲一个时钟周期,以便使得所有指令都有相同的流水线流程。

- 回写 :将指令产生的结果写回到寄存器堆,包括任何从存储器读取的数据。

进一步减少CPI

要改进CPI,必须增加指令存储器的带宽,ARM10TDMI采用64位存储器结构来解决存储器的瓶颈问题。

- 采用转移预测逻辑。可以把时钟频率提高,达到每一时钟周期取2条指令。转移预测单元在流水线的发射阶段之前(在流水线的取指阶段),能识别转移指令,并把它从指令流中移去,从而,尽可能地把转移所引起的周期损失降至零。

- 采用非阻塞(Non-blocking)存取执行。一般的存储器存储加载指令,不能在单一存储器周期中完成。采用非阻塞存取措施,就不会在流水线的执行阶段产生停顿。

- 采用64位数据存储器。这样,允许在每个时钟周期传送2个寄存器的指令存取。ARM10TDMI的寄存器组具有4个读端口和3个写端口。

参考文献:

孟祥莲.嵌入式系统原理及应用教程(第2版)[M].北京:清华大学出版社,2017.

【版权声明】本文为华为云社区用户原创内容,未经允许不得转载,如需转载请自行联系原作者进行授权。如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)