复杂时序逻辑电路

1. 时序逻辑电路的基本结构和分类

1-1. 基本结构

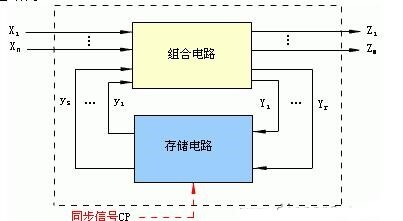

时序逻辑电路由组合电路和存储电路两部分组成,通过反馈回路将两部分连成一个整体。时序逻辑电路的一般结构如下图所示。

图中,X~1~,…,X~n~为时序逻辑电路的输入信号;Z~1~,…,Z~m~为时序逻辑电路的输出信号;y~1~,…,y~s~为时序逻辑电路的状态信号,又称为组合电路的状态变量;Y~1~,…,Y~r~为时序逻辑电路中的激励信号,它决定电路下一时刻的状态;CP为时钟脉冲信号,它是同步时序逻辑电路中的定时信号。

若记输入信号为$\vec{X}$,输出信号为$\vec{Z}$,激励信号为$\vec{Y}$,状态信号为$\vec{y}$,于是上述的4个向量之间的转换关系可以由下面的三个公式表示:

其中,式1-1.1表达了输出信号与输入信号和状态信号之间的关系,被称为输出方程组;式1-1.2表示了激励信号与状态信号和输入信号之间的关系,称为时序电路的激励方程;式1-1.3表示了电路从现态到次态的转换过程,被称作状态转换方程。

在这里大家可以看到,上面的时序电路又是状态($\vec{y}$)依赖的,我们常把这样的电路叫做状态机。

1-2. 时序逻辑电路的分类

1-2-1. 异步时序电路与同步时序电路

关于这个问题在上一章有过讨论。这里还要再啰嗦两句。

可以这样理解:如果时序电路中个存储单元的状态更新不是同时发生的,则这种电路称为异步时序电路;如果个存储电路状态是在同一信号的同一边沿更新的,就可以称作同步时序电路。

导致这种更新不同步的原因可能是:电路的触发器的时钟输入端没有连接在相同的时钟脉冲上,或者这个电路里根本就没有时钟脉冲。

1-2-2. 米利型和摩尔型电路

关于这个问题的详细描述将在下一章出现。

2. 几个典型的时序逻辑电路

多个触发器在同一时钟下组合在一起,来保存相关信息的电路称为寄存器。就像触发器一样, 寄存器也可以有其它的控制信号。你将了解具有附加控制信号的寄存器的行为。

计数器是广泛使用的时序电路。在本次实验中,你将用几种方法设计寄存器和计数器。 请参考Vivado 教程上关于如何使用Vivado创建工程和验证电路。

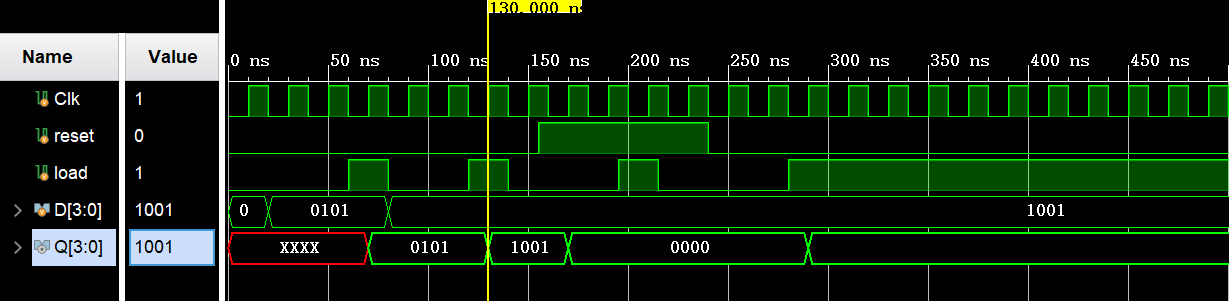

2-1. 可同步重置、载入信号的寄存器

在计算机系统中,相关信息常常在同时被存储。 寄存器(register )以这样的方式存储信息比特,即系统可以在同一时间写入或读出所有的比特。寄存器的例子包含数据、地址、控制和状态。简单的寄存器数据的输入引脚和输出引脚分开,但它们用相同的时钟源。一个简单寄存器的设计如下。

module Register (input [3:0] D, input Clk, output reg [3:0] Q);

always @(posedge Clk)

Q <= D;

endmodule这个简单的寄存器会在每个时钟周期工作,保存需要的信息。然而,在有的情况下,需要只有在特定条件发生时,寄存器内容才被更新。比如,在计算机系统中的状态寄存器只在特定的指令执行时才更新。在这种情况下,寄存器的时钟需要用一个控制信号控制。这样的寄存器需要包含一个时钟使能引脚。下面是这种寄存器的设计。

module Register_with_synch_load_behavior(input [3:0] D, input Clk,

input load, output reg [3:0] Q);

always @(posedge Clk)

if (load)

Q <= D;

endmodule

-

添加开发板相对应的XDC文件,编辑XDC文件,加入相关的引脚,将 Clk 赋给 SW15,D input 给SW3-SW0,reset 给 SW4, load 给 SW5,Q 给 LED3- LED0。

-

把下面这行代码加入XDC文件,使SW15 允许被当作时钟使用。 set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets { clk }];

-

综合你的设计。

-

实现你的设计,查看Project Summary和Utilization table,注意到1个BUFG和 11 个IO被使用了。

-

生成比特流文件,将其下载到Nexys4 DDR开发板,并验证功能。

- 点赞

- 收藏

- 关注作者

评论(0)