简单时序逻辑电路

1. 时序逻辑电路概念

在前述的组合逻辑中,任意时刻的输出只与该时刻的输入信号所决定;而在接下来要讲的时序电路中,任意时刻的输出信号不仅与当时刻的输入有关,而且与电路原来的状态有关。这需要电路要能记住历史输入,所以要引入时序概念。用时钟信号保障时序电路按照时序来运行。

2. 锁存器和触发器

锁存器和触发器是时序电路中常用的存储器设备。

2-1. 锁存器

锁存器是一种具有两种稳定状态的器件:高输出和低输出。 锁存器具有反馈路径,因此设备可以保留信息。 锁存器是易失性存储器设备,并且只要设备通电就可以存储一位数据。 顾名思义,锁存器用于“锁定”信息并保持信息。

2-1-1. SR锁存器

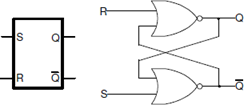

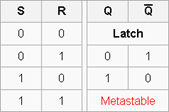

SR锁存器(置位/复位)是一个异步器件:它不依赖于控制信号工作,仅依赖于S和R输入的状态。它的符号表示、使用异或门级电路实现和真值表如下所示:

虽然Xilinx FPGA可以使用一个LUT(查找表)电路实现这种锁存器,但以下Verilog代码显示了如何使用门级电路和数据流建模对这种电路进行建模。

门级:

module SR_latch_gate (input R, input S, output Q, output Qbar);

nor (Q, R, Qbar);

nor (Qbar, S, Q);

endmodule

数据流:

module SR_latch_dataflow (input R, input S, output Q, output Qbar);

assign #2 Q = ~ (R | Qbar);

assign #2 Qbar = ~ (S | Q);

endmodule使用上面显示的代码设计SR锁存器。 合成设计并查看合成设计的原理图。 设计一个Testbench进行测试并验证设计。

该实验中将S输入分配给SW0,将R输入分配给SW1。将Q分配给LED0,将Qbar分配给LED1。实现该设计并进行仿真验证以及下载。

实验步骤:

1. 打开Vivado并创建一个名为lab5_1_1的空白项目。

2. 使用SR_latch_dataflow代码创建和添加Verilog模块。

3. 设计一个Testbench进行测试(也可以使用参考代码中的Testbench),执行100ns的行为仿真,并验证设计。

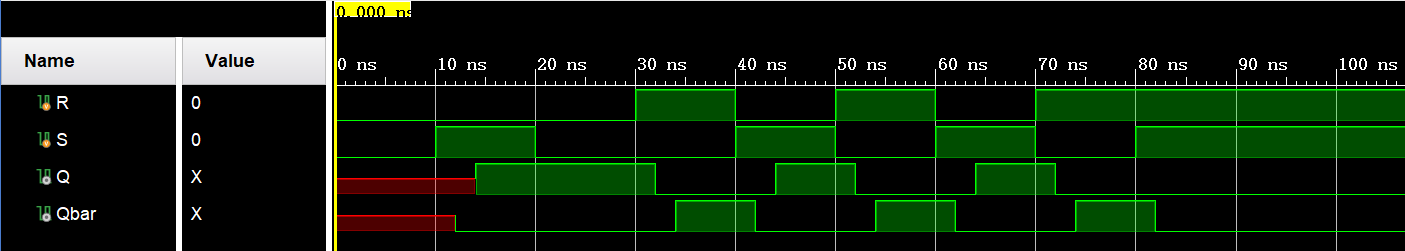

若使用供参考的Testbench,波形应该如下:

4. 将适当的板相关主XDC文件添加到项目中并编辑它以包括相关引脚,将S输入分配给SW0,将R输入分配给SW1,将Q分配给LED0,将Qbar分配给LED1。

5. 在“Bitstream Settings”中设置tcl.pre选项以指向提供的lab5_prehook.tcl文件。 此文件允许将组合循环上载到电路板。

6. 合成设计并在Synthesized Design过程组下查看原理图。验证它使用2个LUT和4个IO(2个IBUF和2个OBUF)。

7. 实现设计并查看项目摘要。 它应该显示2个LUT和4个IO。

8. 生成比特流,将其下载到Nexys4 DDR板,并验证功能。

参考代码:

module RS_latch_tb();

reg R,S;

wire Q,Qbar;

RS_latch TB (.R(R),.S(S),.Q(Q),.Qbar(Qbar));

initial begin

R = 0;

S = 0;

#10 S = 1;

#10 S = 0;

#10 R = 1;

#10 R = 0; S = 1;

#10 R = 1; S = 0;

#10 R = 0; S = 1;

#10 R = 1; S = 0;

#10 S = 1;

end

endmodule- 点赞

- 收藏

- 关注作者

评论(0)