复杂组合逻辑电路

设计实现一个流行IC 74138,使用数据流建模和你在1-1中使用的译码器

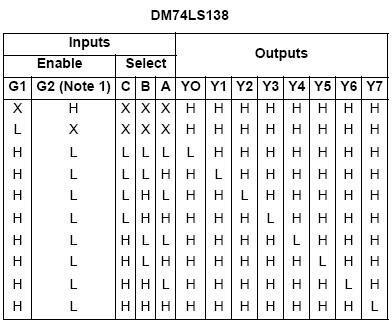

集成三线—八线译码器74138除了3线到8线的基本译码输入输出端外,为便于扩展成更多位的译码电路和实现数据分配功能,74138还有三个输入使能端 EN1, EN2A和EN2B 。74138真值表和内部逻辑图如下图:

所示符号图中,输入输出低电平有效用极性指示符表示,同时极性指示符又标明了信号方向。74138的三个输入使能(又称选通ST)信号之间是与逻辑关系, EN1高电平有效,EN2A和EN2B低电平有效。只有在所有使能端都为有效电平(EN1EN2AEN2B=100)时,74138才对输入进行译码,相应输出端为低电平,即输出信号为低电平有效。在EN1EN2AEN2B ≠100时,译码器停止译码,输出无效电平(高电平)。这和你在1中创建的非常相似,它只是增加了控制(使能)信号G1,/G2A,/G2B。这使得在有些系统中的解码更加简单。

实验步骤

-

打开Vivado创建一个空工程,命名为lab3_2.

创建并添加Verilog模块,命名为decoder_74138_dataflow,实例化你在1-1中开发的模块。添加额外的逻辑,使用数据流建模结构建模所设计的功能。

编写仿真文件来验证代码的正确

将你在1中使用的XDC文件添加到工程。修改XDC文件,将g1分配给SW7,g2a_n分配给SW6,g2b_n分配给SW5。

综合实现你的设计。

生成比特流文件,下载到Nexys4开发板上,验证功能。

首先,修改lab1的decoder_3to8_dataflow模块,在其中加入enable信号

module

decoder_3to8_dataflow( input enable, input [2:0]x, output reg [7:0]y );

always@(*) if(enable) case(x) 3’b000: y=8’b0000_0001;

3’b001: y=8’b0000_0010;

3’b010: y=8’b0000_0100;

3’b011: y=8’b0000_1000;

3’b100: y=8’b0001_0000;

3’b101: y=8’b0010_0000;

3’b110: y=8’b0100_0000;

3’b111: y=8’b1000_0000;

endcase else y=8’b0000_0000;

endmodule之后,decoder_74138_dataflow模块的具体实现:

module decoder_74138_dataflow(

input g1,

input g2a_n,

input g2b_n,

input [2:0]x,

output [7:0]y

);

reg enable;

always@(*)

begin

if(g1==1&&g2a_n==0&&g2b_n==0)

enable=1;

else enable=0;

end

decoder_3to8_dataflow A(enable,x,y);

endmodule

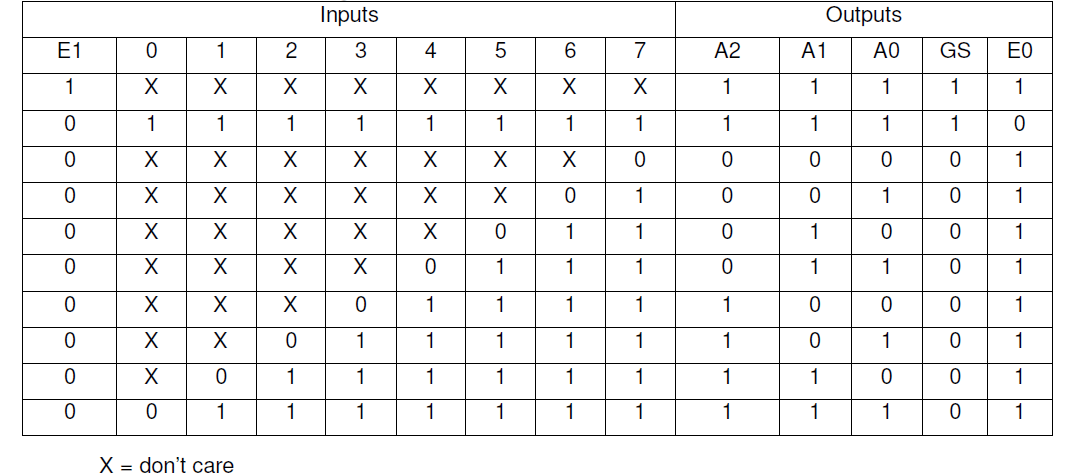

## 设计一个8-3编码器 ### 多输出编码电路 编码器电路是出于对标准化,速度,保密性,安全性或者通过缩小尺寸来节省空间的考虑,将信息从一种形式(编码)转换为另一种形式(编码)的电路。在数字电路中,编码信息可以减小信息存储所用的空间,确定功能的优先级。广泛使用的编码电路的例子有,优先编码器,哈弗曼编码器等 ### 8-3编码器真值表

- 点赞

- 收藏

- 关注作者

评论(0)