简单组合逻辑电路

verilog中的数字表示

在 Verilog HDL 中一个信号可能有如下四种基本的值:i.0:逻辑 0 或假ii.1:逻辑 1 或真iii.x:未知iv.z:高阻态(三态)在门电路的输入端或是表达式中的 z 值通常会被译为一个 x 值(待确定)。通常情况下, Verilog HDL 是区分大小写的,但是作为值来表示时是不区分大小写的。

在 Verilog HDL 中有三种常量类型:(i)整型,(ii)实型,和(iii)字符串。在整型常量和实型常量中可以使用下划线(_)来增加可读性。但它不能出现在第一个和最后一个字符的位置上。

整数可以写成 (i) 简单的十进制数或者是 (ii) 带进制格式。一个写成简单十进制形式的整数由一个可省略的+或是一个-和一串数字组成。比如,15-32其中 15 可以被写成 5 比特格 式的二进制数 01111,-32 可以写成 6 比特格式的 100000。简单的十进制数在硬件中最终会占用 32 比特。

一个数也可以被表示为进制格式,语法格式如下: [size]’base value其中size 代表数的比特数,base(基)是 o 或者O(代表八进制 octal),b 或者 B(代表二进制 Binary),d 或者 D(代表十进制Decimal),h 或者 H(代表十六进制hexadecimal)中的一个。Value 是一个在该进制下有效的数字的序列。Value 必须是无符号的。比如, wire [4:0] 5’O37 //5 比特八进制表示reg [3:0] 4’B1x_01 //4 比特二进制wire [3:0] 4’d-4 //不合法,value 不能是负数wire [11:0] 7’Hx //7 比特 x 扩展到 xxxxxxx如果 size 设定得比设定的常数的值的大小要大,这个数会被用 0 扩展到左边,除非最左边的比特是x 或 z,此时也会相应地用x 或 z 扩展。如果 size 设定得更小,那左边的多余的位会被忽略。如果size 未设定,那么就会使用 32 比特。

设计一个BCD码到7段数码管的译码器

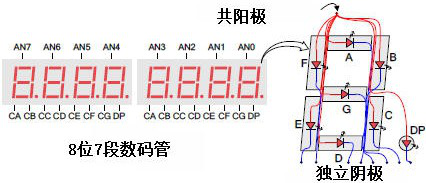

数码管原理

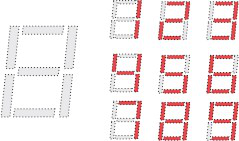

7段数码管显示器包含7段,编号从a到g,可以用来显示一个字符。根据不同的输入类型,可能需要做类型转换。如果需要显示4bit的BCD码,则需要一个BCD码到7段数码管的译码器。下表展示了你要显示一个数字的bit图样。(需要注意的是,你如果需要点亮某一段,则要输出逻辑0到这一段,并且这个显示器的阳极需要用板上的逻辑0驱动)。

Nexys4 DDR开发板包含两个4位7段数码管LED显示器。每个模块中4位的每1位都由7段组成,每一段都嵌入了一颗LED,顺序如下图。每段的LED可以被单独点亮。因而通过点亮特定的段,熄灭其他段,全部128种图样都可以在1位上实现。在这128种图样中,10种数字的图样最有用。

组成每一位的7颗LED的阳极被连接在一起,称为“共阳极”的电路节点,但LED的阴极是独立的。共阳极节点的信号可以被获取作为4位显示器的使能信号。不同位,相同段的阴极信号分别接到7个电路节点,从CA 到CG (比如上图中4位的 “D” 笔画的阴极被连接到一起,连接到 “CD”这个电路节点)。这7个阴极节点信号可以被获取作为4位显示器的输入信号。这种信号连接的方案支持了多路复用的显示,虽然每个笔 画的阴极信号是4位共用的,但它们只能点亮阳极信号生效的位上的笔画。

扫描显示控制器电路可以用来控制这个显示器显示一个4位数。这个电路根据阴极图样,以高于人眼可分辨地频率,对每一位的阳极信号进行重复地、持续地、接连地驱动。如果它的更新或“刷新”率降到大约45 Hz时,大多数人能看出显示在闪烁。从Lab 8(体系结构向导和知识产权目录)开始你将设计和使用一个扫描电路。

参考代码

module lab2_1(

input [3:0]x,

output reg [7:0]seg,

output [7:0]an

);

assign an=8'b1111_1110;

always@(*)

case(x)

0: seg= 8'b 1100_0000;

1: seg= 8'b 1111_1001;

2:seg= 8'b 1010_0100;

3: seg= 8'b 1011_0000;

4: seg= 8'b 1001_1001;

5: seg= 8'b 1001_0010;

6: seg= 8'b 1000_0010;

7: seg= 8'b 1111_1000;

8: seg= 8'b 1000_0000;

9:seg= 8'b 1001_0000;

default seg=8'bxxxx_xxxx;

endcase

endmodule- 点赞

- 收藏

- 关注作者

评论(0)