Verilog语法之测试文件

要测试我们设计的模块功能是否正常,最直接的办法就是烧写到FPGA芯片中进行验证,但是这种方式往往结果并不直观,且出现问题后也不容易定位。为提高工作效率,我们可通过电脑仿真的方式进行功能验证,待仿真通过后,再烧写到FPGA中,这样可以快速排除电路中存在的绝大多数bug。在电脑上进行仿真,除了我们设计的功能模块之外,还需要另一模块——testbench,用于产生被测模块所需的激励信号。由于testbench只是用于电脑端的仿真,而不需要最终综合成电路,因此其写法更加灵活,可以使用verilog语法中的一些不可综合的语句,如initial、#、$display、$readmemb、forever等。

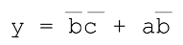

假设我们的被测模块完成以下功能

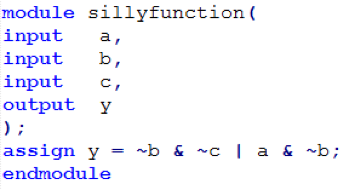

其verilog代码为:

1. 简单测试文件

最简单的测试文件可以写成如下形式:

语法说明:

testbench文件一般不包含任何输入输出信号

将被测模块实例化,被测模块的输入信号定义成reg类型,输出信号定义成wire类型。

initia l:通过initial块构造输入信号的波形,同一initial块内部的语句是串行执行的,多个initial块之间并发执行。

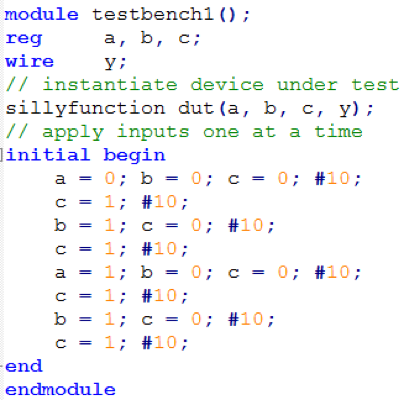

2. 自检测试文件

带自检功能的测试文件如下所示,可以对输出结果进行判断,并打印错误信息。

模块的输入信号给定之后,就有有结果输出,将实际输出结果于预期结果做比较,如果不同,则打印出错误信息。

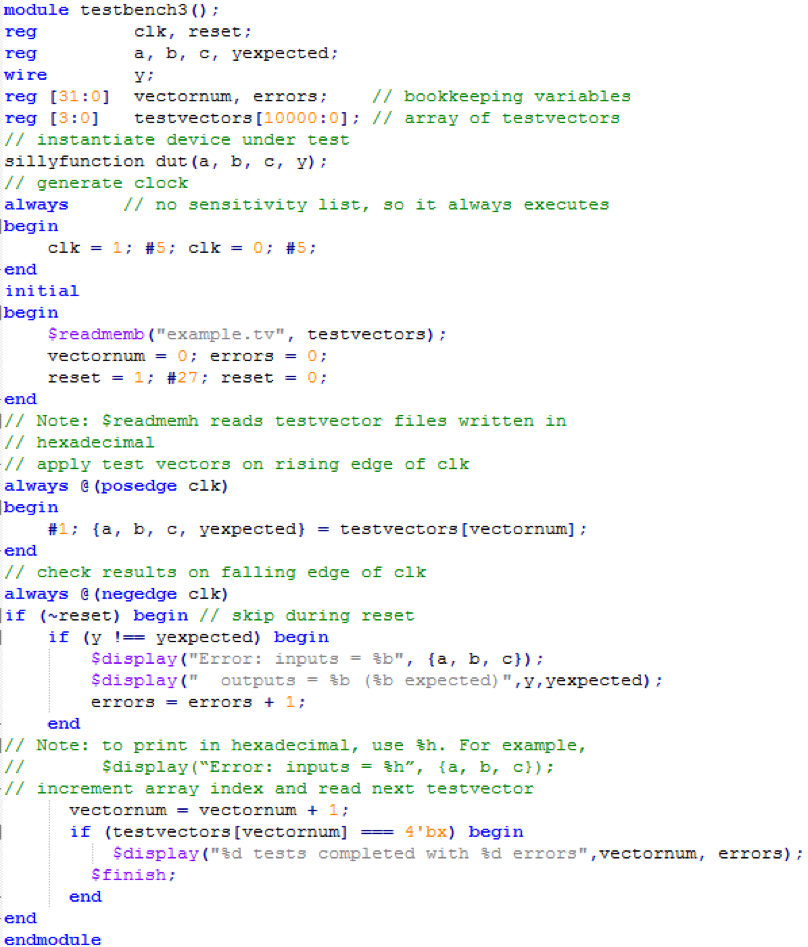

3. 测试向量

通过测试向量进行仿真

将输入信号的各种组合以及对应的输出结果构成一测试向量,则每个向量中都包含了一种输入状态,以及该状态下的期望输出结果

将该向量导入一内存数组

构造一时钟信号

在时钟的上升沿,将一个向量赋值给被测模块输入端,并在时钟的下降沿对被测模块输出与期望输出结果进行对比,如果不相同,则记录下该向量,至此向量全部测试完毕。

向量测试文件(example.tv):包含a、b、c以及y_expected

000_1

001_0

010_0

011_0

100_1

101_1

110_0

111_0

测试文件

前面介绍了三种测试方法,三种方法各有其优缺点。

简单测试文件编写简单,容易上手,但需要人工判断仿真结果的正确性;

带自检的测试文件可以将错误信息打印出来,但编写稍微复杂一些,且激励波形仍需通过人工输入代码来完成;

测试向量法测试文件编写最为复杂,还需要编写一个用于跟被测模块结果进行比较的黄金模型,但此种方法测试最为充分,且后续维护起来也最容易。

- 点赞

- 收藏

- 关注作者

评论(0)