【实验要求】

- 实验内容与原理说明(包括框图、逻辑表达式和真值表)。

- 实验模块程序代码(设计模块Design Block)和激励代码(激励模块Test Bench)。

- 仿真波形图。

- 综合得到的门级电路图,所用器件的型号以及设计模块所占用该型器件的资源情况。

- 实验结果分析及思考。

- 每一次报告用Word文档提交,文件名:姓名_班级_第几次实验_学号。

【实验软件工具】

- QuartusII;

- ModelSim SE.

【一】设计一个交通红绿灯控制器模块,实现主干道和支路之间红绿黄灯的信号转换

1. 实验内容与原理说明

本实验实现一个交通信号灯的控制模块,实现主干道和支路之间的红绿黄灯的信号转换。假设LIGHT1为主路信号灯,LIGHT2为支路信号灯,每一个信号灯循环周期为50s。20s,H为绿灯,F为红灯。5s,H为黄灯,F为红灯。20s,H为红灯,F为绿灯。5s,H为红灯,F为黄灯。

通过分析交通灯控制电路的要求可知,系统主要由传感器、时钟脉冲产生器

定时器、控制器及译码器构成,传感器S在有车辆通过时发出一个高电平信号。

可知交通灯的系统框图如下:

编辑

编辑

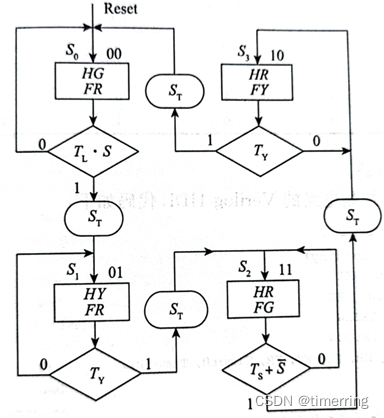

可以得到其ASM图如下:

编辑

编辑

根据交通灯控制单元的ASM图, ASM图中的状态框与状态图中的状态相对应,判断框中的条件是状态转换的输入条件,条件输出框与控制单元状态转换的输出相对应。状态图是描述状态之间的转换,例如在S,状态,如果条件TL·S=1时,系统状态转移到ST,同时输出状态转换信号S1。如果TL·S=0,则系统保持在S0状态。

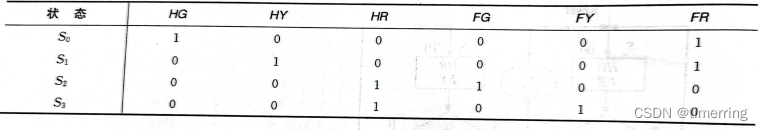

当交通灯控制电路处于不同工作状态时,交通信号灯按一定的规律与之对应,各状态与信号灯的关系如表5.4.2所示。表中用1表示灯亮,用0表示灯灭。

可以得到信号灯与控制器状态编码表如下:

编辑

编辑

2. 实验模块程序代码和激励代码

(1)设计模块代码

//定义状态

`define S0 2'b00//主绿支红

`define S1 2'b01//主黄支红

`define S2 2'b11//主红支绿

`define S3 2'b10//主红支黄

//定义trafficLight控制程序

module trafficLight(CLK,S,rst,HR,HG,HY,FR,FG,FY,timeH,timeL);

input CLK,S,rst;

output[3:0] timeH;

output[3:0] timeL;

reg[3:0] timeH;

reg[3:0] timeL;

output reg HR,HG,HY,FR,FG,FY;

wire TL,TS,TY;

reg ST;

reg[1:0] CState,NState;

//时序模块的描述

always@(posedge CLK or negedge rst) begin

if(~rst)

{timeH,timeL}<=8'h00;

else if(ST)

{timeH,timeL}<=8'h00;

else if((timeH==5)&(timeL==9)) begin

{timeH,timeL}<={timeH,timeL};

end

else if(timeL==9) begin

timeH<=timeH+1;

timeL<=0;

end

else begin

timeH<=timeH;

timeL<=timeL+1;

end

end

assign TY=(timeH==0)&(timeL==4);

assign TS=(timeH==2)&(timeL==9);

assign TL=(timeH==5)&(timeL==9);

//定义三种输出时间输出标志

//描述状态机状态转换

always@(posedge CLK or negedge rst) begin

if(~rst)

CState<=`S0;

else

CState<=NState;

end

//分别对四种状态进行描述

always@(S or CState or TL or TS or TY) begin

case(CState)

`S0:begin

NState=(TL&&S)?`S1:`S0;

ST=(TL&&S)?1:0;

end

`S1:begin

NState=(TY)?`S2:`S1;

ST=(TY)?1:0;

end

`S2:begin

NState=(TS||~S)?`S3:`S2;

ST=(TS||~S)?1:0;

end

`S3:begin

NState=(TY)?`S0:`S3;

ST=(TY)?1:0;

end

endcase

end

//将状态转换译码

always@(CState) begin

case(CState)

`S0:begin

{HG,HY,HR}=3'b100;

{FG,FY,FR}=3'b001;

end

`S1:begin

{HG,HY,HR}=3'b010;

{FG,FY,FR}=3'b001;

end

`S2:begin

{HG,HY,HR}=3'b001;

{FG,FY,FR}=3'b100;

end

`S3:begin

{HG,HY,HR}=3'b001;

{FG,FY,FR}=3'b010;

end

endcase

end

endmodule

(2)激励模块代码

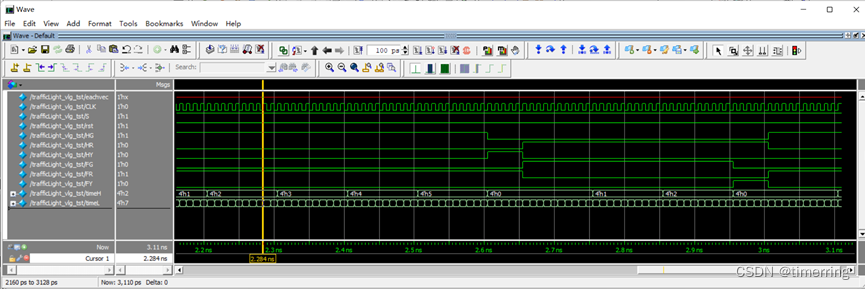

3. 波形仿真图

编辑

编辑

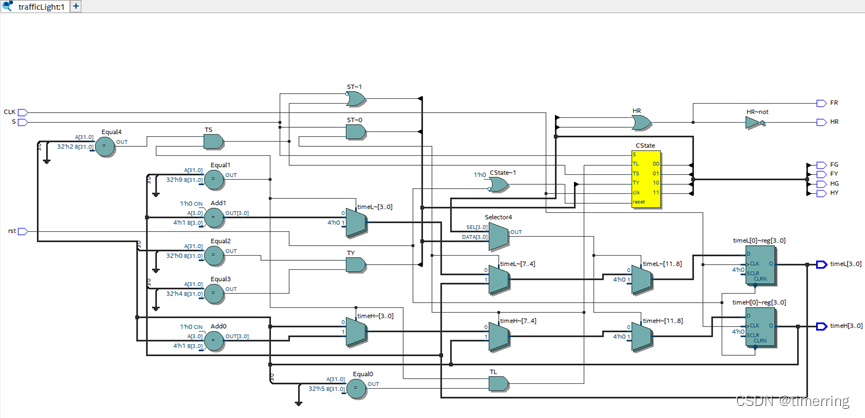

4.门级电路图

编辑

编辑

设计模块所占用器件的资源情况如下所示:

编辑

编辑

【二】设计一个小轿车尾灯控制器模块(以书中的例子)

1. 实验内容与原理说明

汽车尾灯发出的信号主要是给后面行驶汽车的司机看的,通常汽车驾驶室有刹车开关(HAZ)、左转弯开关(LEFT)和右转弯开关(RIGHT),司机通过操作这

3个开关给出车辆的行驶状态。假设在汽车尾部左、右两侧各有3个指示灯,分别用LA、LB、LC、RA、RB、RC表示,如图5.4.1所示。这些灯的亮、灭规律如下:

1)汽车正常行驶时,尾部两侧的6个灯全部熄灭。

2)刹车时,汽车尾灯工作在告警状态,6个灯按一定频率闪烁。

3)左转弯时,左侧3个灯轮流顺序点亮,其规律如图5.4.2a所示,右侧灯全灭。

4)右转弯时,右侧3个灯轮流顺序点亮,其规律如图5.4.2b所示,左侧灯全灭。

假设电路的输入时钟信号为CP,CP的频率对应于汽车尾灯所要求的闪烁频率。试根据上述要求设计出一个时钟同步的状态机来控制汽车的尾灯。

选择Moore状态机设计该电路,则尾灯的亮、灭直接由状态译码就可以得到。由设计要求可知:汽车左转弯时,右边的灯不亮而左边的灯依次循环点亮,即0个、1个、2个或3个灯亮,分别用L、L、L、L表示,状态机在4个状态中循环。同理,汽车右转弯时,状态机也会在4个状态中循环,即左边灯不亮而右边的灯有0个、1个、2个或3个灯亮,分别用R、R、R、R,表示。由于L和R,都表示6个灯不亮,所以合起来用IDLE表示。

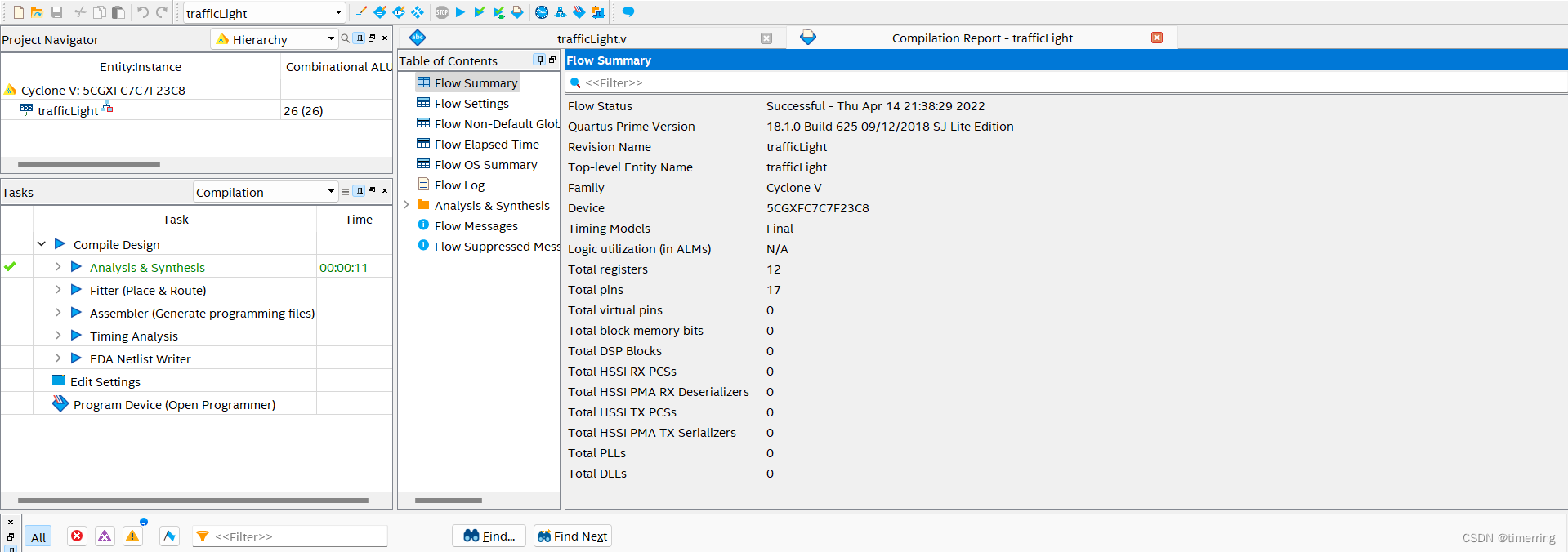

状态机一旦左循环或者右循环开始后,如果刹车信号HAZ有效,状态机不会立即响应,而是必须等到左(或右)循环完成后才会进入告警状态。经过改进且具有这一特性的状态图如下图所示。

编辑

编辑

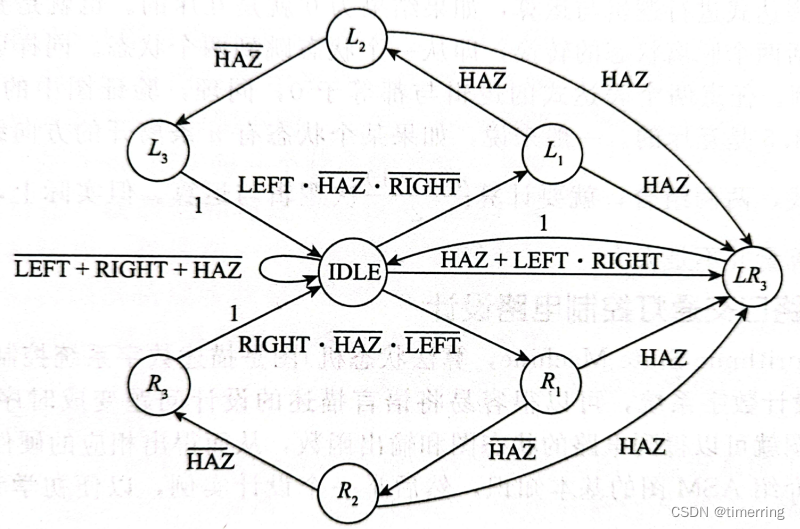

由于电路的输出信号较多,不便于写在状态图中,所以单独列出输出逻辑真值表,如下表所示。

编辑

编辑

2. 实验模块程序代码和激励代码

(1)设计模块代码

`define IDEL 3'b001//均不亮

`define LR3 3'b100//均亮

`define L1 3'b011//左侧亮一个灯

`define L2 3'b010//左侧亮两个灯

`define L3 3'b000//左侧亮三个灯

`define L1 3'b011//左侧亮一个灯

`define R1 3'b101//右侧亮一个灯

`define R3 3'b110//右侧亮两个灯

`define R2 3'b111//右侧亮三个灯

module carLight(RST,CLK,LEFT,RIGHT,HAZ,RA,RB,RC,LA,LB,LC);

input RST,CLK,LEFT,RIGHT,HAZ;

output reg RA,RB,RC,LA,LB,LC;

reg[2:0] CState,NState;

always@(posedge CLK or negedge RST) begin

if(~RST)

CState<=`IDEL;

else

CState<=NState;

end

always@(CState or LEFT or RIGHT or HAZ) begin

case(CState)

`IDEL:begin

if(LEFT&RIGHT|HAZ)

NState=`LR3;

else if(LEFT&(~HAZ)&(~RIGHT))

NState=`L1;

else if((~LEFT)&(~HAZ)&RIGHT)

NState=`R1;

else

NState=`IDEL;

end

`L1:begin

if(~(LEFT|HAZ))

NState=`IDEL;

else if(LEFT&(~HAZ)&(~RIGHT))

NState=`L2;

else

NState=`LR3;

end

`L2:begin

if(~(LEFT|HAZ))

NState=`IDEL;

else if(LEFT&(~HAZ)&(~RIGHT))

NState=`L3;

else

NState=`LR3;

end

`L3:begin

if((~LEFT)&(~HAZ)|(~RIGHT)&(~HAZ))

NState=`IDEL;

else

NState=`LR3;

end

`R1:begin

if(~(RIGHT|HAZ))

NState=`IDEL;

else if(RIGHT&(~HAZ)&(~LEFT))

NState=`R2;

else

NState=`LR3;

end

`R2:begin

if(~(RIGHT|HAZ))

NState=`IDEL;

else if(RIGHT&(~HAZ)&(~LEFT))

NState=`R3;

else

NState=`LR3;

end

`R3:begin

if((~LEFT)&(~HAZ)|(~RIGHT)&(~HAZ))

NState=`IDEL;

else

NState=`LR3;

end

`LR3:begin

if((~LEFT)&(~HAZ)|(~RIGHT)&(~HAZ))

NState=`IDEL;

else

NState=`LR3;

end

endcase

end

//状态译码过程

always@(CState) begin

case(CState)

`IDEL:begin

{LC,LB,LA,RA,RB,RC}=6'b000_000;

end

`L1:begin

{LC,LB,LA,RA,RB,RC}=6'b001_000;

end

`L2:begin

{LC,LB,LA,RA,RB,RC}=6'b011_000;

end

`L3:begin

{LC,LB,LA,RA,RB,RC}=6'b111_000;

end

`R1:begin

{LC,LB,LA,RA,RB,RC}=6'b000_100;

end

`R2:begin

{LC,LB,LA,RA,RB,RC}=6'b000_110;

end

`R3:begin

{LC,LB,LA,RA,RB,RC}=6'b000_111;

end

`LR3:begin

{LC,LB,LA,RA,RB,RC}=6'b111_111;

end

endcase

end

endmodule

(2)激励模块代码

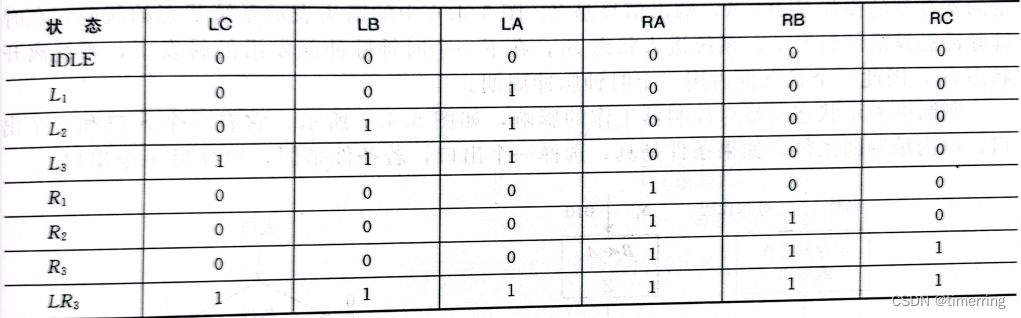

3. 波形仿真图

编辑

编辑

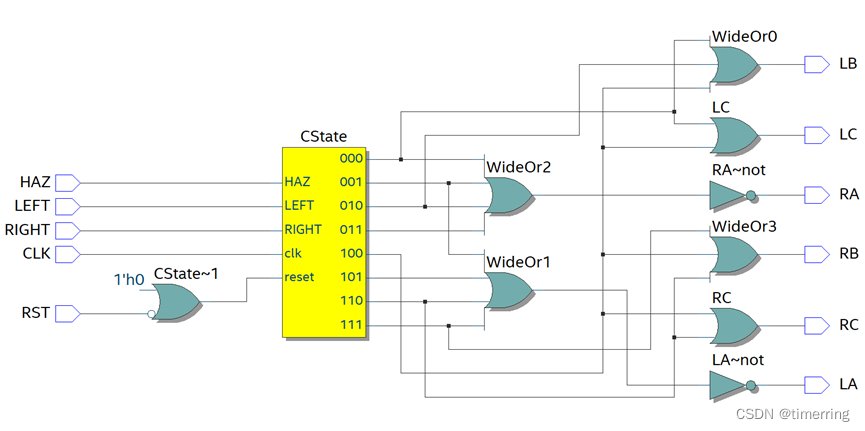

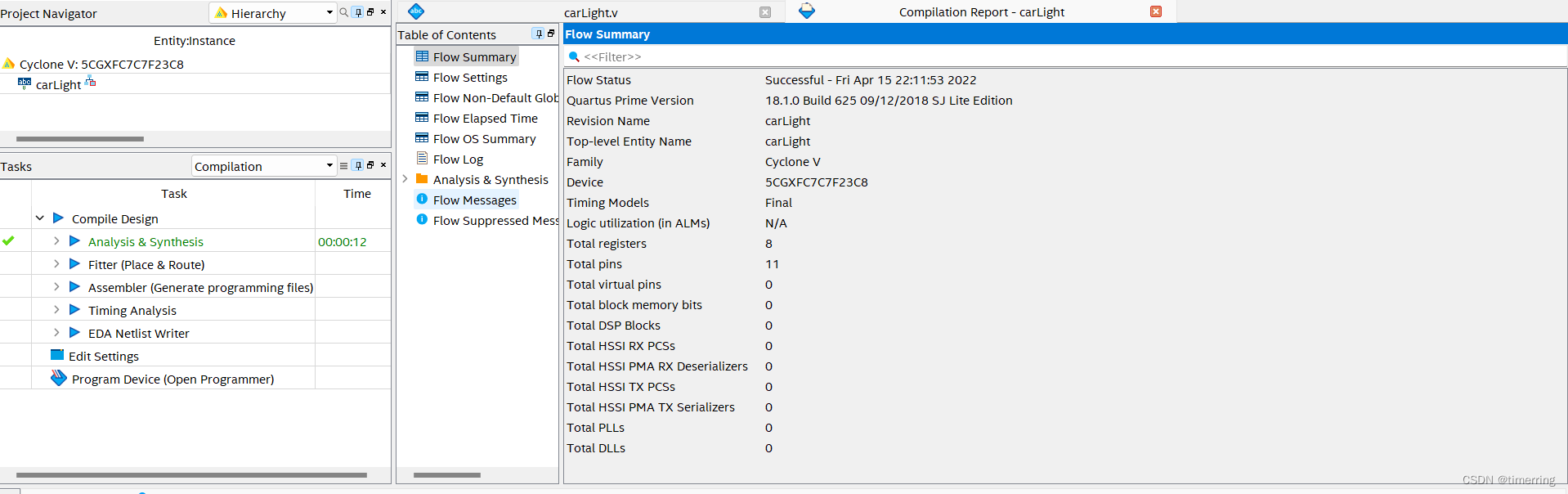

4.门级电路图

编辑

编辑

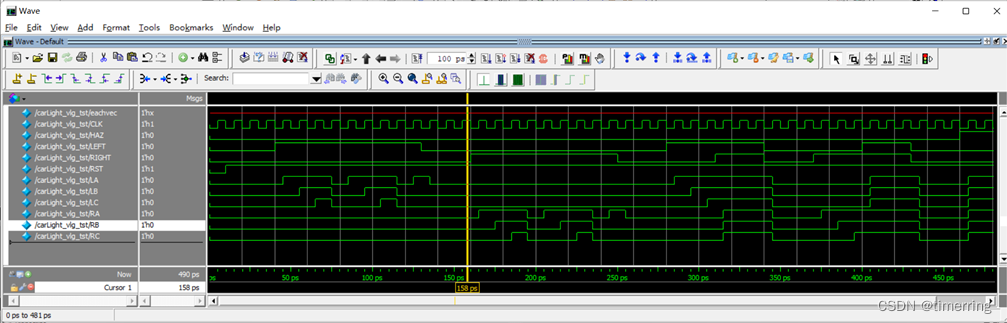

设计模块所占用器件的资源情况如下所示:

编辑

编辑

评论(0)