FPGA设计8位异步、同步二进制计数器

【实验要求】

- 实验内容与原理说明(包括框图、逻辑表达式和真值表)。

- 实验模块程序代码(设计模块Design Block)和激励代码(激励模块Test Bench)。

- 仿真波形图。

- 综合得到的门级电路图。

- 实验结果分析及思考。

- 每一次报告用Word文档提交,文件名:姓名_班级_第几次实验_学号。

【实验软件工具】

- QuartusII;

- ModelSim SE.

【一】设计一个8位异步二进制计数器模块

1. 实验内容与原理说明

构成计数器的低位计数器触发器的输出作为相邻计数触发器的时钟,这样逐步串行连接起来的一类计数器称为异步计数器。时钟信号的这种连接方法称为行波计数。这种异步计数器的计数延迟增加影响它的应用范围。异步清零程序的实现:通过判断最后一个状态,当为下一个状态时,就将输出清零,回到循环起点。

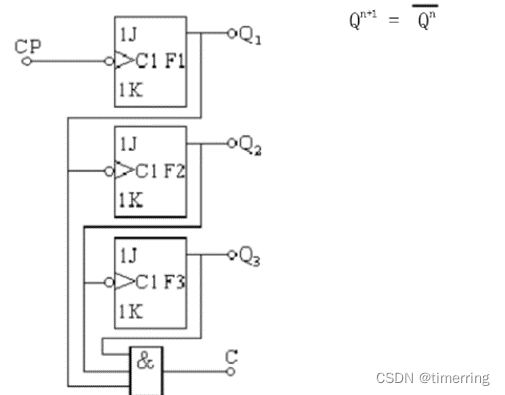

由于八位异步二进制计数器不便形象地展示,这里以三位二进制计数器作以描述,计数器工作前,一般都需要把所有的触发器置“0”,即计数器状态为000。这一过程称清零或复位。清零之后,计数器就可以开始计数了。第一个计数脉冲输入时,在该脉冲的下降沿到来时刻,F1翻转,Q由0变1。Q的正跳变加到F2的CP端,因为触发器都是负跳变触发,所以F2不翻转,计数器的状态为001。第二个计数脉冲输入时,F1又翻转,Q由1变0。Q的负跳变送到F2的CP端,F2翻转,Q= 1。Q的正跳变送到F3的CP端,F3不翻转,计数器状态为010。

按照上述规律,当第七个脉冲输入时,计数器状态为111。如输入第八个脉冲,计数器状态变成000,并产生一个向高位的进位信号。

由上述可知,每向触发器CP端输入一个脉冲,触发器状态就翻转一次,即其原理框图如下:

对应的真值表如下所示:

2. 实验模块程序代码和激励代码

(1)设计模块代码

(2)激励模块代码

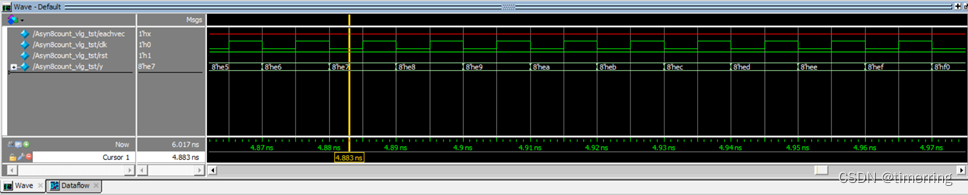

3. 波形仿真图

4.门级电路图

【二】设计一个8位同步二进制计数器模块

1. 实验内容与原理说明

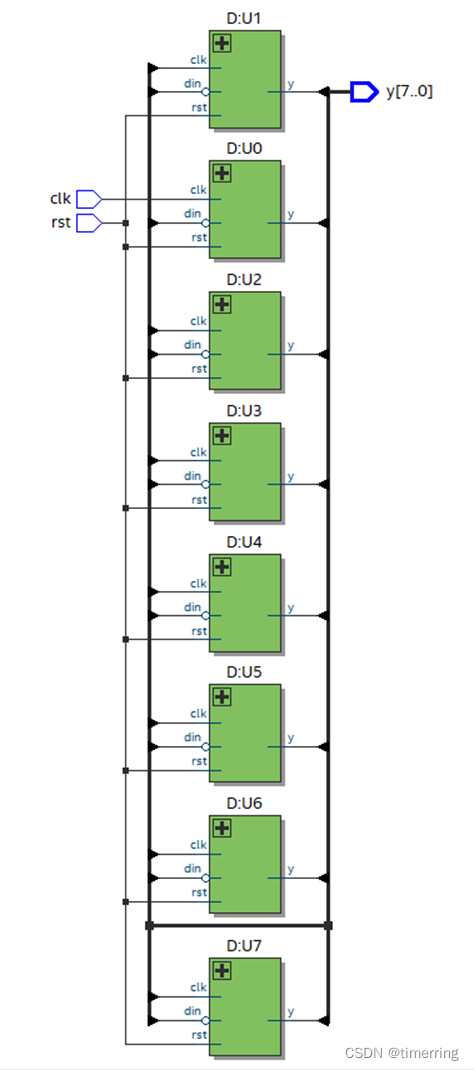

计数器的基本原理是将几个触发器按照一定的顺序连接起来,然后根据触发器的组合状态按照一定的计数规律随着时钟脉冲的变化记忆时钟脉冲的个数。按照计数器各个触发器的时钟是否同步分为同步计数器和异步计数器。同步二进制加法计数器的基本构成方法:将触发器接成 T 触发器;各触发器都用计数脉冲 CP 触发,最低位触发器 的T 输入为 1,其他触发器的 T 输入为其低位各触发器输出信号相与。在同步8位二进制计数器的电路符号中,clk为时钟信号输入端,DATA为预置初值使能端, rst为清零端,en为计数使能端,这些端口均为高电平有效,DOUT为预置计数器初值,Q为计数输出端,COUT为进位信号。

2. 实验模块程序代码和激励代码

(1)设计模块代码

(2)激励模块代码

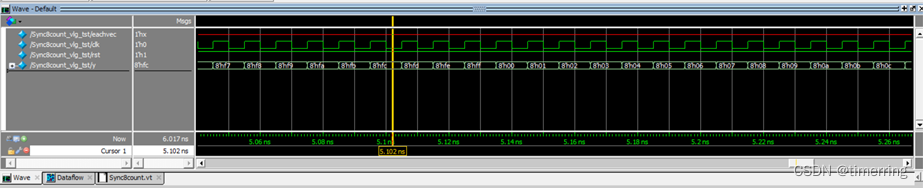

3. 波形仿真图

4.门级电路图

- 点赞

- 收藏

- 关注作者

评论(0)