FPGA设计超前进位与8421-BCD码全加器

设计一个16位二进制超前进位全加器模块

1. 实验内容与原理说明

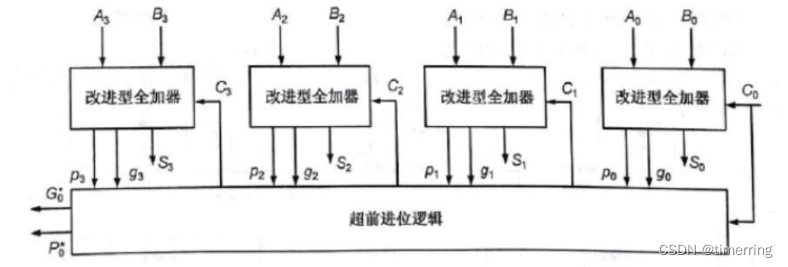

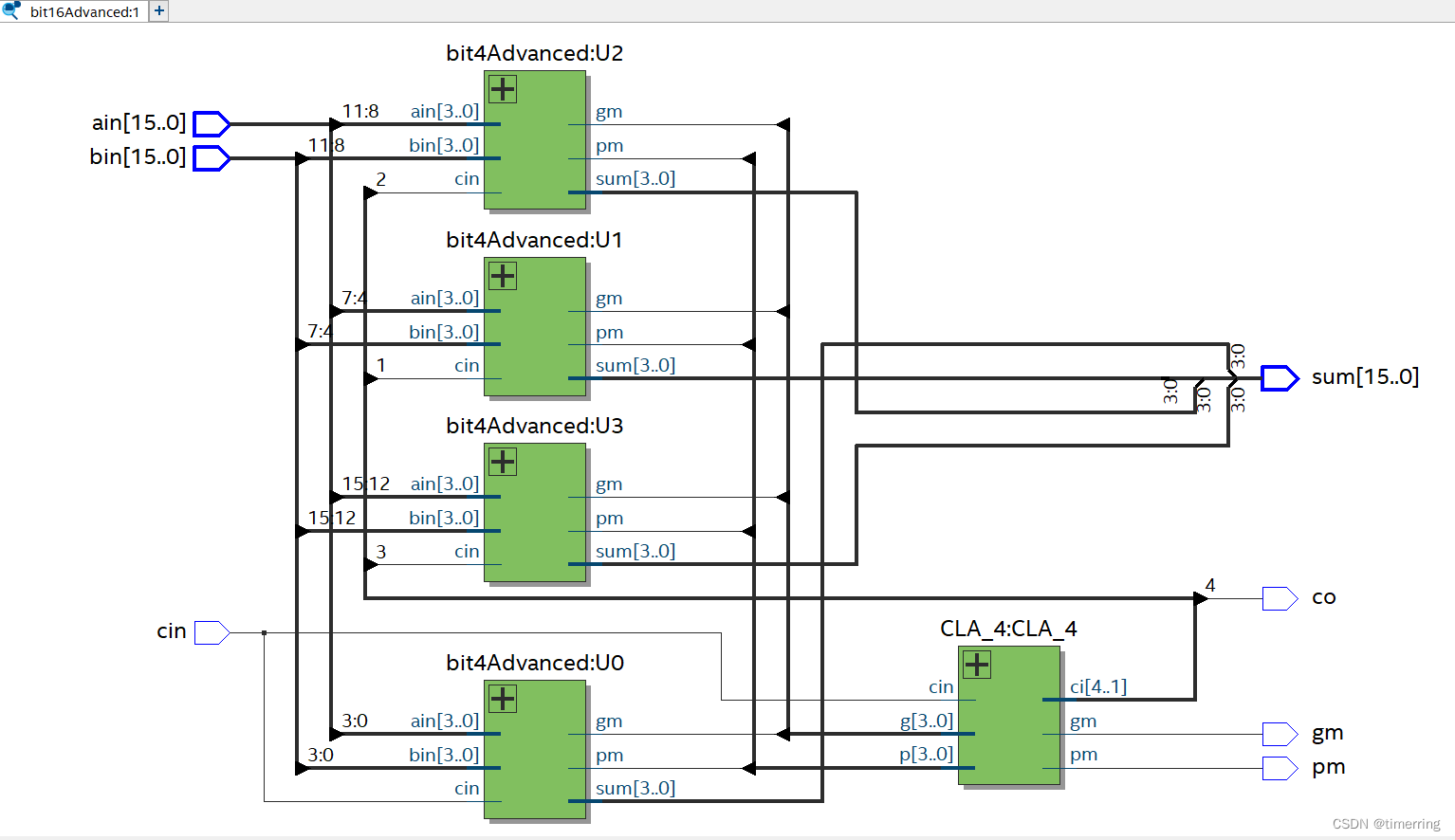

本实验设计一个16位二进制的超前进位全加器模块,用来实现16位二进制的加法,超前进位加法器的结构如下图。下图为一个四位超前进位加法器的结构图。信号经过pi和gi产生一级时延,经过计算C产生一级时延,则A,B输入一旦产生,首先经过两级时延算出第1轮进位值C’不过这个值是不正确的。C’再次送入加法器,进行第2轮2级时延的计算,算出第2轮进位值C,这一次是正确的进位值。这里的4个4位超前进位加法器仍是串行的,所以一次计算经过4级加法器,一级加法器有2级时延,因此1次计算一共经过8级时延,相比串行加法器里的16级时延,速度提高很多。

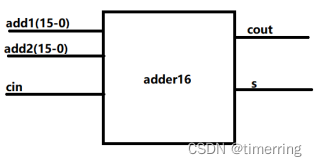

设计封装模块如下:

超前进位全加器的真值表如下:

| Ai |

Bi |

Ci |

Si |

Ci+1 |

| 0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

1 |

0 |

| 0 |

1 |

0 |

1 |

0 |

| 0 |

1 |

1 |

0 |

1 |

| 1 |

0 |

0 |

1 |

0 |

| 1 |

0 |

1 |

0 |

1 |

| 1 |

1 |

0 |

0 |

1 |

| 1 |

1 |

1 |

1 |

1 |

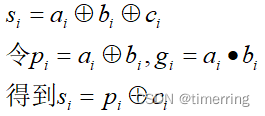

由上,可以求得两个输出的表达式为:

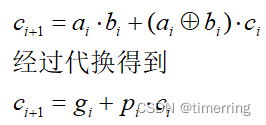

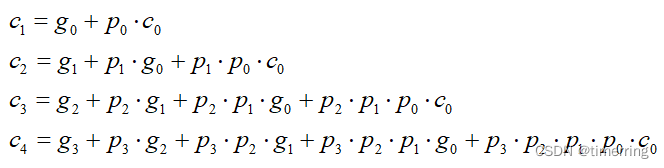

对于i=0~3的代入,得到每一级的进位输出表达式如下:

2. 实验模块程序代码和激励代码

(1)设计模块代码

(2)激励模块代码

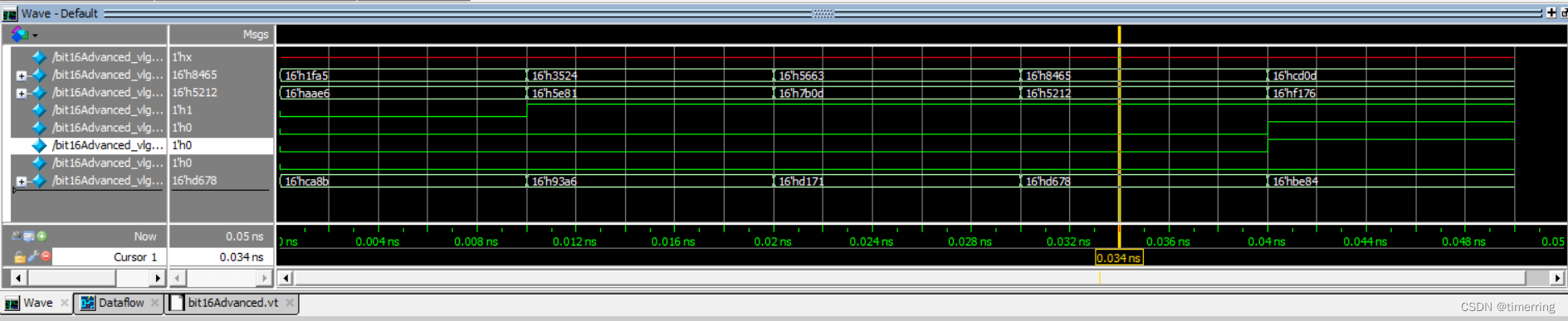

3.波形图

4.门级电路图

设计一个16-bit 8421-BCD码全加器模块

1.实验内容与原理说明

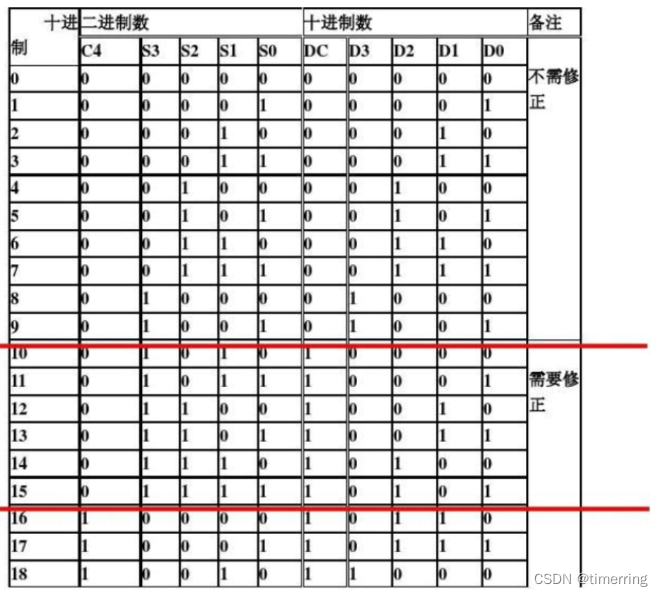

本实验实现一个16位二进制的BCD码全加器模块,用来实现16位二进制的加法,由于两个1位十进制数相加时,和的取值范围是0—18,将该范围内各数值对应的二进制数和8421BCD码列表,以便寻找何时应对结果修正以及如何修正。

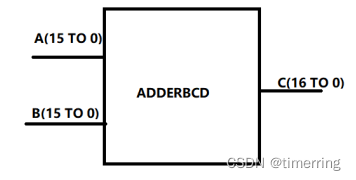

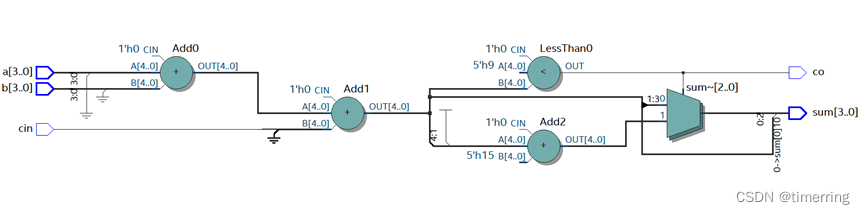

实验封装设计框图如下:

同时,我们知道当两个BCD码相加时,如果得到的结果为10以内,则显示的BCD码即为相加得到的结果,比如0001+0010=0011即3;但是当两个BCD码相加结果大于10,则应当加上6,即为显示的BCD码,即1001+0001 =9+1=1010=10,但应当显示0,于是将1010+0110=10000=0000,即显示为0。

下面详细地列出了真值表:

2. 实验模块程序代码和激励代码

(1)设计模块代码

()激励模块代码

3.波形图

4.门级电路图

【结果分析及思考】

本次实验分别对16位二进制全加器模块,16位超前进位二进制全加器模块,16-bit 8421-BCD码全加器模块进行了设计与实现。其中在设计16位二进制全加器模块的过程中,分别使用了按照行为描述的方式以及按照数据流的方式建模,让我从实践的角度理解了建模方式的不同,掌握了包括门级电路,数据流以及行为描述这三种建模方法。

全加器是常用的组合逻辑模块中的一种,对全加器的分析和对组合逻辑电路的分析一样。组合逻辑电路的分析,就是找出给定电路输入和输出之间的逻辑关系,从而了解给定逻辑电路的逻辑功能。组合逻辑电路的分析方法通常采用代数法,我的设计过程按照老师所给出的步骤进行:先根据所需要的功能,列出真值表。然后根据真值表,写出相应的逻辑函数表达式。再根据真值表或逻辑函数表达式,画出相应的组合逻辑电路的逻辑图。之后用编写程序在QuartusⅡ上进行仿真并在Modelsim上测试,分析结果的正确性。

印象较深的是在数据流描述中,通过层次化设计方法实现的结构,这个加法器是使用了16个全加器进行连接和信号传递组成的,而一位全加器是由两个半加器以及一个或门所构成,这个全加器的组成和描述频繁使用了元件例化语句,就是为了能够完整的描述这16个全加器在结构上的关系以及和所对应输入输出之间的关系。

全加器是组合逻辑电路中最常见也最实用的一种,考虑低位进位的加法运算就是全加运算,实现全加运算的电路称为全加器。它主要实现加法的运算,其中分为并行全加器和串行全加器,所谓并行就是指向高位进位时是并行执行的,而串行就是从低位到高位按顺序执行,为了提高运算,必须设法减小或消除由于进位信号逐级传递所消耗的时间,为了提高运算速度,制成了超前进位加法器,这是对全加器的一种创新。这也正是超前进位二进制全加器的思想。

在16位的BCD码加法器的设计中,用4个数与4个数进行加和,通过BCD码输出结果。但是实验中需要注意很多细节,例如BCD码的最大范围就是1001也就是9,因此需要将二进制改为10进制,判断得到的结果是否需要进位,如果不需要进位的话,显示的结果就为真实结果,如果需要进位,则应当将得到的结果加上6,即对数字进行修正,以此实现显示信号的输出。

通过此次设计对全加器的设计和实现,积累和总结了不少的经验,锻炼了我的独立工作和实际动手能力,加深了对计算机中的全加器工作原理的认识,提高了对复杂的综合性实践环节具有分析问题、解决问题、概括总结的实际工作能力,对涉及全加器项目的开发、设计过程有初步认识。

- 点赞

- 收藏

- 关注作者

评论(0)