FPGA设计16位二进制全加器模块

【摘要】 【实验要求】 实验内容与原理说明(包括框图、逻辑表达式和真值表)。实验模块程序代码(设计模块Design Block)和激励代码(激励模块Test Bench)。仿真波形图。综合得到的门级电路图。实验结果分析及思考。每一次报告用Word文档提交,文件名:姓名_班级_第几次实验_学号。【实验软件工具】QuartusII;ModelSim SE.【一】设计一个16位二进制全加器模块1. 实...

【实验要求】

- 实验内容与原理说明(包括框图、逻辑表达式和真值表)。

- 实验模块程序代码(设计模块Design Block)和激励代码(激励模块Test Bench)。

- 仿真波形图。

- 综合得到的门级电路图。

- 实验结果分析及思考。

- 每一次报告用Word文档提交,文件名:姓名_班级_第几次实验_学号。

【实验软件工具】

- QuartusII;

- ModelSim SE.

【一】设计一个16位二进制全加器模块

1. 实验内容与原理说明

此次实验为设计一个16位全加器模块并对其进行测试,本实验是以数据流的方式描述全加器模块,其中16位全加器有一个进位输入端和一个进位输出端,以及16位的数据输入和输出端,实现16位数据的计算,具体的实验如下。

由分析可知,该实验的逻辑表达式如下所示:

s+cout=cin+A+B

cout=A+B+cin

s=A+B+cin

该设计模块的实验框图如下:

2. 实验模块程序代码和激励代码

(1) 设计模块Design Block

(2) 激励模块Test Bench

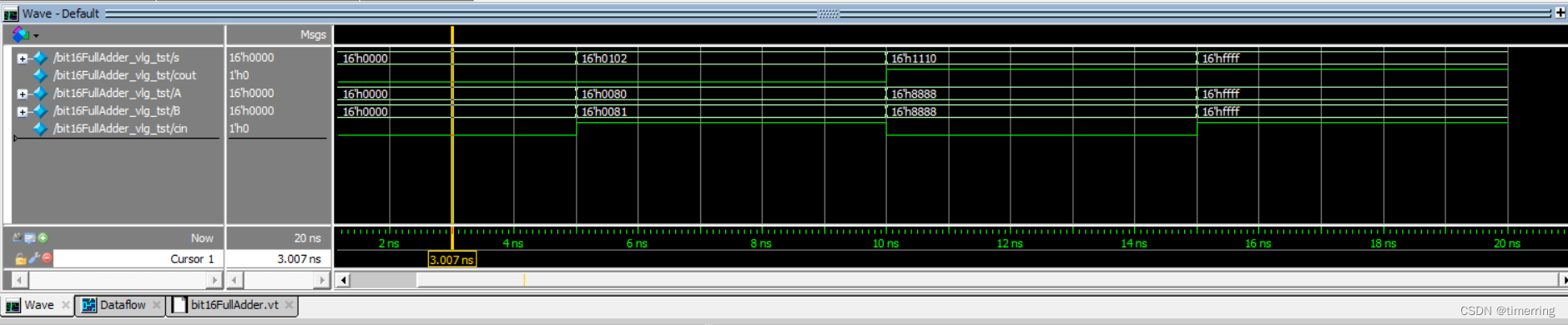

3.仿真波形图

4.门级电路图

【二】用层次化设计方法,设计一个16位二进制全加器模块

【实验具体内容】

1. 实验内容与原理说明

本实验实现一个16位全加器的设计和调试,在这个实验中实现的是从元件例化的方面进行说明和描述,所谓16位全加器就是需要有一个进位输入端和一个进位输出端,以及16位的数据输入和输出端,实现16位数据的计算。所实现的数据计算如下:

s+cout = cin+a+b

s=a+b+cin

cout = a+b +cin

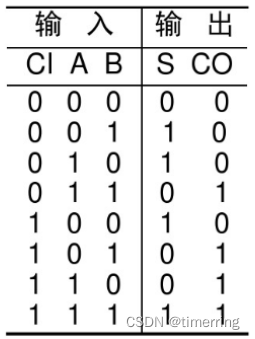

其中,全加器的真值表如下所示:

其逻辑表达式为:

S = A⊕B⊕CI

CO=AB+CI(A+B)

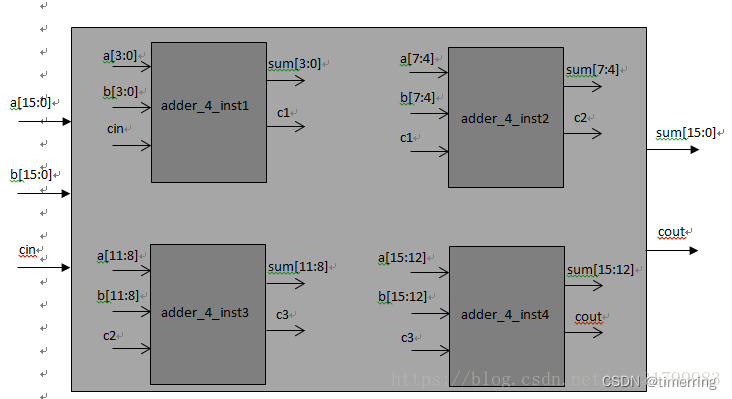

按照自底向上的逻辑逐级设计,四位全加器可对两个多位二进制数进行加法运算,同时产生进位。当两个二进制数相加时,较高位相加时必须加入较低位的进位项(CI),以得到输出为和(S)和进位(C0)。其中CIN表示输入进位位,COUT表示输出进位位,输入A和B分别表示加数和被加数。输出SUM=A+B+CIN,当SUM大于255时,COUT置‘1’。四位加法器原理图如下:

再由四位加法器按层次封装即可形成十六位加法器。

2. 实验模块程序代码和激励代码

(1)设计模块代码

(2)激励模块代码

3.仿真波形图

4.门级电路图

【版权声明】本文为华为云社区用户原创内容,未经允许不得转载,如需转载请自行联系原作者进行授权。如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)