GT Transceiver中的重要时钟及其关系(4)CPLL的工作原理介绍

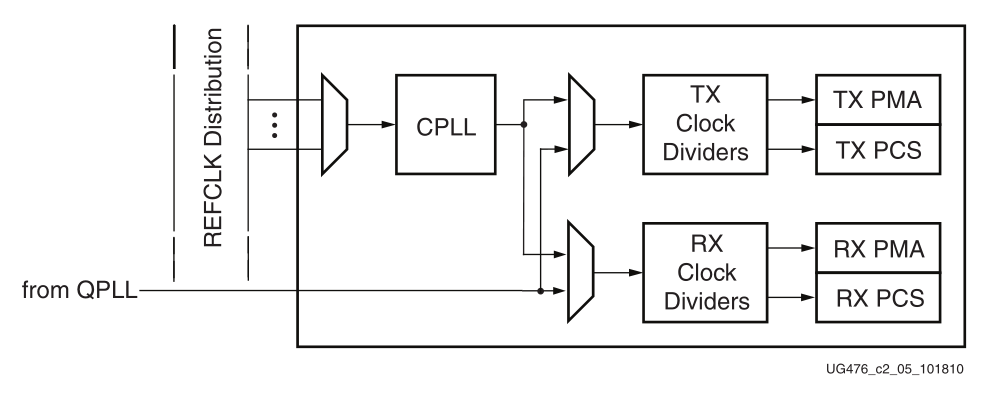

Transceiver内部时钟架构如下:

Transceiver内部时钟来源可以是QPLL也可以是自己的CPLL。

其内部TX 和 RX 时钟分频器可以单独从 QPLL 或 CPLL 中选择时钟,允许 TX和 RX 数据通道使用不同的参考时钟输入在异步频率工作。

这个单独二字表明了TX和RX可以独立的选择时钟分频器的时钟来源。

CPLL的 输出输入到 TX 和 RX 时钟分频器模块,控制 PMA 和 PCS 模块使用的串行和并行时钟的生成。如果 TX和 RX 数据通道的运行速率是相同 VCO (压控振荡器)频率的整数倍,则可以在它们之间共享 CPLL。

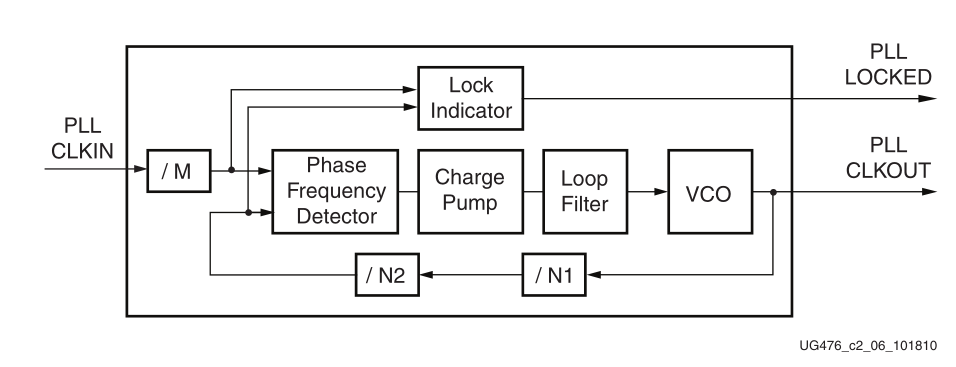

下图显示了CPLL架构的概念视图:

其工作原理是:

输入时钟在进入相位频率检测器之前可以被除以M的系数。 反馈分频器N1和N2决定了VCO的 乘法比率 和CPLL的输出频率。锁定指示块比较参考时钟和VCO反馈时钟的频率,以确定是否已实现频率锁定。(建议这段话配合下面的公式一起理解)

GTX收发器中的CPLL的额定工作范围在1.6 GHz至 3.3 GHz。GTH收发器中的CPLL的标称工作范围为 1.6 GHz至5.16 GHz。7系列FPGAs Transceiver Wizard根据应用要求选择适当的CPLL设置。

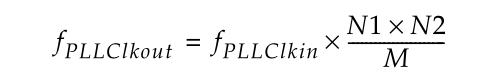

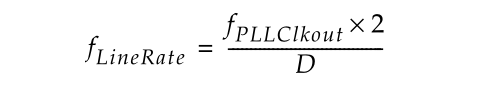

下面两个公式决定了PLL时钟输出频率以及transceiver的线速率:

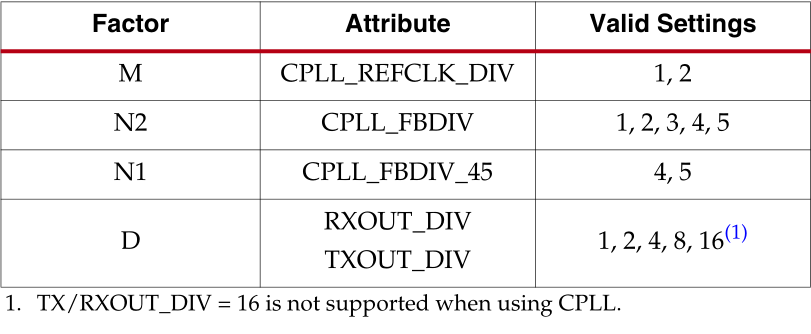

其中M,N1,N2和D都是CPLL的一些属性,可以配置。

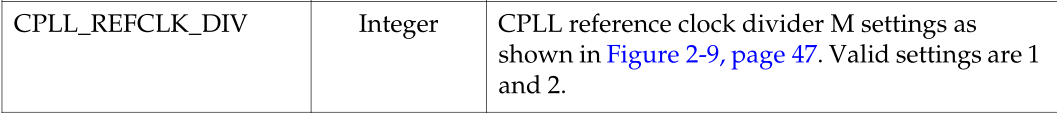

例如,M对应的属性为CPLL_REFCLK_DIV:

举例说明:

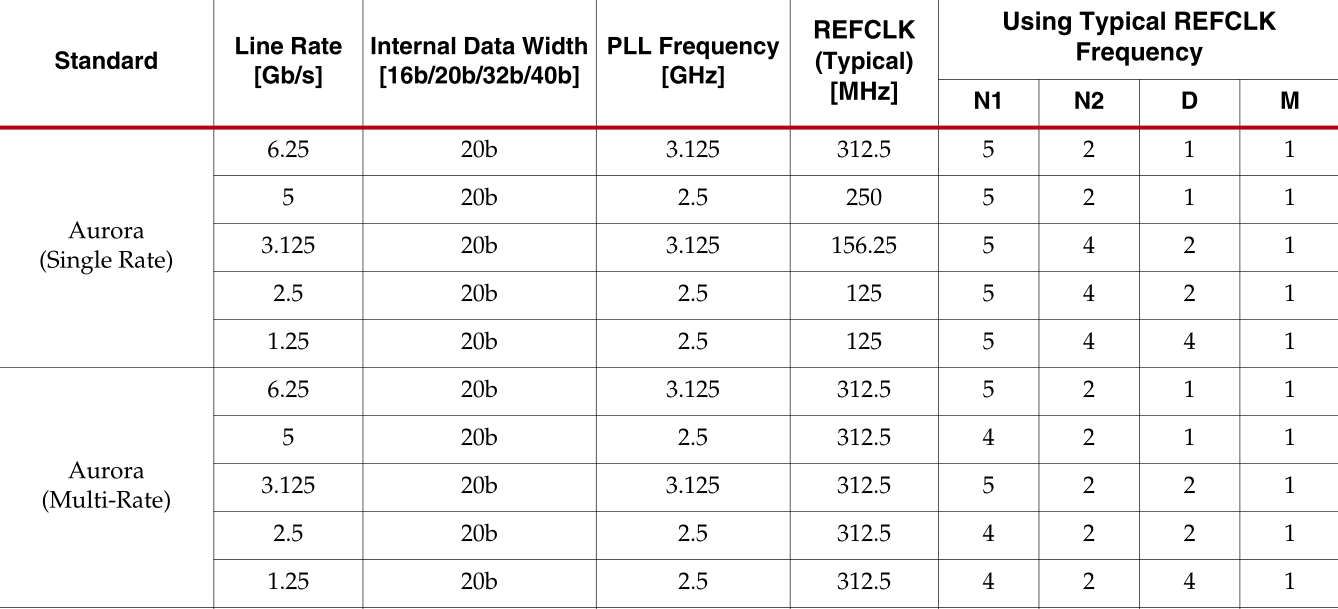

如下Aurora标准协议的线速率与外部参考时钟之间的关系:

以第一行为例:

line rate = REFCLKN1 N2 * 2/(M D ) = 312.5 * 52*2/1=6.25Gbps.

一些协议被显示为单速率配置和多速率配置两次。在单速率配置中,只需要一个线速,参考时钟为该特定线速进行了优化。在多速率配置中,为最高的线路速率选择参考时钟,并选择适当的分频器来支持较低的线路速率。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/120774820

- 点赞

- 收藏

- 关注作者

评论(0)