宽带接收机中的非均匀采样技术研究之非均匀采样平台的硬件设计(2018/8/20)(第八篇)

给出上篇博文的地址:宽带接收机中的非均匀采样技术研究之OMP算法(2018/8/20)(第七篇)

给出原论文的地址:宽带接收机中的非均匀采样技术研究

从功能上划分,非均匀采样平台的实现可以分为两个方面:

1) 完成对频域稀疏信号的压缩采样;

2) 对采样数据进行重构。

第一个问题是硬件实现问题,也即是如何设计硬件电路完成对频域稀疏信号的压缩采样,而第二个问题则是选择合适的重构算法对采样数据进行处理。

本章以 2.3 节介绍的非均匀采样器采样模型为框架,介绍非均匀采样平台的具体组成结构,并对具体的硬件器件选择进行简要介绍。

宽带接收机中的非均匀采样技术研究之非均匀采样器(NUS) 采样模型(2018/8/19)(第六篇)

下面结合非均匀采样器采样模型,具体介绍非均匀平台的具体硬件实现方法。

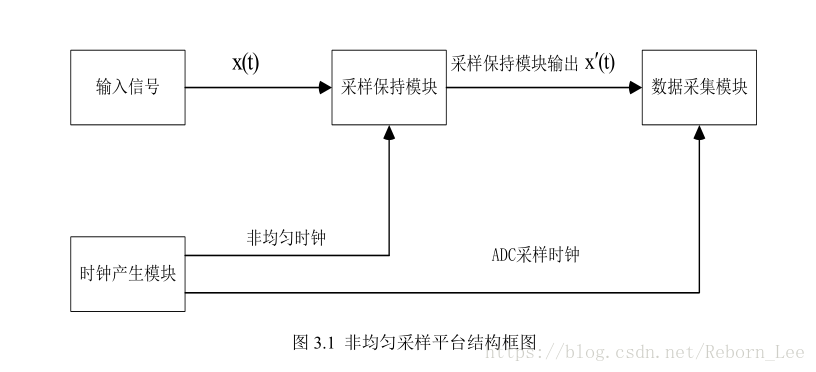

非均匀采样平台组成

由于当前主流的 ADC 芯片都是工作在均匀采样模式下,想要直接利用 ADC芯片进行非均匀采样是不适用的。所以在设计实际的硬件平台时,我们让采样保持器在非均匀时钟的控制下,对输入信号进行非均匀采样,而且采样保持器在ADC 采样时刻输出幅度等于最近一次采样值的信号,最终利用 ADC 芯片对采样保持器的输出信号进行均匀采样实现对非均匀采样数据的提取。具体的硬件实现框图如图 3.1 所示:

如图 3.1 所示,可将非均匀采样平台分为三个功能模块:时钟产生模块,采样保持模块以及数据采集模块。

其中时钟产生模块是整个平台的时序控制核心,它为整个平台提供所需要的时钟信号,主要包括 ADC 采样时钟,非均匀时钟等;

采样保持模块与 2.3 节中所述的采样保持器具有相同的工作特性,该模块主要完成对输入信号进行非均匀采样保持,为 ADC 提供所需要的输入信号。该模块在非均匀时钟的控制下,对输入信号进行非均匀采样,并使其输出信号的幅度在ADC 的采样时刻保持为非均匀采样值。

数据采集模块的主要功能是利用低速ADC 以低于奈奎斯特速率的采样率完成最终的数据采集。

主要使用到的器件包括电源芯片,时钟芯片,FPGA,DSP 以及 ADC 芯片等。

有话要说:整个非均匀采样平台采样最后的输出是一个采样点数远远低于奈奎斯特采样点数的离散信号,该离散信号包含了恢复原始信号所需要的全部信息。

也就是说非均匀采样得到的离散信号 y[n] 就是压缩感知里面的观测向量。

为什么呢?需要反复阅读论文。等我能说明白了再说。

这里我们还需要留下一个问题:上面所说的主要用到的器件包括电源芯片,时钟芯片,FPGA,DSP 以及 ADC 芯片等:那么这些器件在这个非均匀采样平台中的具体作用在哪里?

非均匀时钟设计

非均匀采样平台可以看作是实现了输入信号与随机观测矩阵相乘,而观测矩阵的好坏则由非均匀采样时钟决定。该平台最终的采样样本数由 ADC 的采样率 决定,则所设计的非均匀采样平台对奈奎斯特速率的压缩比

决定,则所设计的非均匀采样平台对奈奎斯特速率的压缩比  可表示为:

可表示为:

我们设计的非均匀采样平台能对频率在 4GHz 范围内的频域稀疏信号进行采样,所以该平台的潜在奈奎斯特速率  =8GHz而最终的 ADC 采样率

=8GHz而最终的 ADC 采样率 =800MHz,所以

=800MHz,所以 =10 ,即实现了对奈奎斯特速率的十倍压缩。且 ADC 采样间隔

=10 ,即实现了对奈奎斯特速率的十倍压缩。且 ADC 采样间隔 。

。

为了能得到较好的非均匀采样数据以及保证 ADC最终的采样数据是非均匀采样的数据,则采样保持模块在非均匀时钟的控制下需要满足如下条件:采样保持模块的非均匀采样时刻都随机出现在 ADC 相邻两次采样时刻的间隔内并且保证采样保持模块的输出信号在 ADC 采样时刻为最近一次非均匀采样的采样值,这样便可以利用 ADC 提取出非均匀采样的数据,即实现对信号的非均匀采样。

不得不说,上面最后一段话,说的真蹩脚,把明白的人都看得不明白了,这大概就是论文“写作手法”,为了避免重复以及其他原因,把描述写的生涩难懂。

上面的那段话的意思不就是ADC的采样时刻采样的值必须是非均匀采样保持器采样保持的那个值。

还真的不是很好表达,见博文:宽带接收机中的非均匀采样技术研究之非均匀采样器(NUS) 采样模型(2018/8/19)(第六篇),这篇博文的最后就讲到了非均匀采样保持器的原理,我们只需要ADC采样时刻与非均匀时钟的低电平时刻对齐,采样非均匀保持的值就好了。

假设用  来构建采样函数,则采样保持模块进行非均匀采样的采样函数

来构建采样函数,则采样保持模块进行非均匀采样的采样函数  ,奈奎斯特采样函数

,奈奎斯特采样函数 以及 ADC 的采样函数

以及 ADC 的采样函数 的关系如图 3.2 所示:

的关系如图 3.2 所示:

如图 3.2 所示, 是一组随机变量,其取值范围是

是一组随机变量,其取值范围是 ,

, 是潜在的奈奎斯特采样间隔, 从图中可以看出,

是潜在的奈奎斯特采样间隔, 从图中可以看出,  可看作是从

可看作是从 中随机抽取得到的,而

中随机抽取得到的,而 可看作是从

可看作是从  中以 10 为间隔均匀抽取得到的。

中以 10 为间隔均匀抽取得到的。

且 和

和 具有如下关系:

具有如下关系:

为了准确控制非均匀时钟的采样时刻和 ADC 采样时刻具有上述关系,我们通过对伪随机二进制码做电平转换来产生非均匀时钟,本文利用 GTH 来实现电平转换从而产生非均匀时钟。注意到 2.3 节对采样保持器的描述可知,采样保持器在时钟下降沿对信号进行采样,并在时钟低电平的间隔内输出幅度为采样值的信号。对于下降沿,可以利用“10”序列实现,低电平让码元为‘0’获得,从而将非均匀时钟的设计转换为对伪随机二进制序列的设计。

在设计伪随机二进制序列时,我们令码元宽度  ,由于 ADC 的采样时钟

,由于 ADC 的采样时钟 是固定不变的,所以可以利用和 ADC 采样时钟

是固定不变的,所以可以利用和 ADC 采样时钟  同频同源的时钟驱动伪随机二进制码元产生器,使得第 10N+1 个码元的开始时刻和 ADC 时钟的采样时刻相同。则随机控制“10”序列在 10N+1 到 10(N+1)+1 区间内出现的位置,便可以使得非均匀时钟的采样函数

同频同源的时钟驱动伪随机二进制码元产生器,使得第 10N+1 个码元的开始时刻和 ADC 时钟的采样时刻相同。则随机控制“10”序列在 10N+1 到 10(N+1)+1 区间内出现的位置,便可以使得非均匀时钟的采样函数 满足式公式(3-2)。考虑到 GTH 在正负电平转换时存在均衡补偿且 ADC 采样会有延时,所以实际产生伪随机二进序列的公式如下所示:

满足式公式(3-2)。考虑到 GTH 在正负电平转换时存在均衡补偿且 ADC 采样会有延时,所以实际产生伪随机二进序列的公式如下所示:

其中,m=1,2,3,4...  是一组随机变量,取值范围为 0~6的整数。此时,可以算出非均匀时钟的采样间隔范围是

是一组随机变量,取值范围为 0~6的整数。此时,可以算出非均匀时钟的采样间隔范围是 .

.

从这个项目的过程来看,这里算是一个理解的难点了,也是本非均匀采样平台中最重要的一部分。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/81872228

- 点赞

- 收藏

- 关注作者

评论(0)