Verilog HDL 使用规范(一)

本博文参考:《大规模逻辑设计指导书》,对于写出规范的代码,培养良好的代码风格颇有裨益。

wire and register

- 一个reg变量只能在一个always语句中赋值;

这个说明至关重要啊,如果不满足这个,也许仿真的时候没问题,但是综合时候绝对出现,不可以综合。我就犯过多次这个错误。

曾经写过一篇博客,专门说过:Modelsim下进行功能仿真没问题,可是在ISE综合报错,如何解决?

- 向量的有效位定义一般是从大到小。

尽管,标准并没有强制这样,但是这样更规范,读代码更加容易。

表达式(Expressions)

- 用括号表示执行的优先级;

这个比较好理解,尽管Verilog HDL语言有自己的优先级,但是使用括号来表示优先级对读者来说更加清晰,更有意义。

例如:if( (a>b) && (c>d) )......

就比下面这种表达要好:

if( a>b && c>d ),尽管二者的作用一致。

- 用一个函数(function)来代替表达式的多次重复,经常使用的一组描述可以写到一个任务中。

If语句

- 向量比较时,比较的向量要相等;

当比较向量时,Verilog将对 位数小的向量做0扩展以使它们的长度相匹配,它的自动扩展是隐式的。建议采用显示扩展,这个规律同样适用于向量同常量的比较。

例如:

reg [7:0] a;

reg [3:0] b;

...

if( a == {4'b0, b} ) begin

...

end

if( a == 8'b0 ) begin

...

end

- 每一个if都有一个else与之对应;

在做硬件设计时,常要求条件为真时执行一种动作,而条件为假时,执行另一个动作,即使认为条件为假不可能发生,也要有一个else语句,该语句可以为一个空语句。

如果没有else语句可能会使综合出来的逻辑和RTL级的逻辑不同。(这句话什么意思呢?就是如果没有else语句,综合工具可能会综合出来一些你不希望出现的东西,例如会综合出锁存器。本可以不用锁存器的,可偏偏因为没有加else语句,而综合出了锁存器,这不仅对电路的整体性能产生影响,同时也会导致资源浪费。)

例如:

以上语句DataOut会综合成锁存器。

- 应注意if... else if...else 的优先级

上面的语句是有优先级的,if的优先级最高,else if其次,else最后。

- 如果变量在if...else或case 语句中做非完全赋值,则应给变量一个缺省值,即:

-

V1 = 2'b00; //default

-

V2 = 2'b00;

-

v3 = 2'b00;

-

-

if(a == b) begin

-

V1 = 2'b01;

-

V2 = 2'b10; //V3 is not assigned

-

-

end

-

-

else if(a == c) begin

-

V2 = 2'b10;

-

V3 = 2'b11; //V1 is not assigned

-

end

-

-

else ;

-

上面的意思就是如果变量在语句中未全部赋值,那么在开始应该给变量一个缺省值,要不然它的值就不可预测了。

case语句

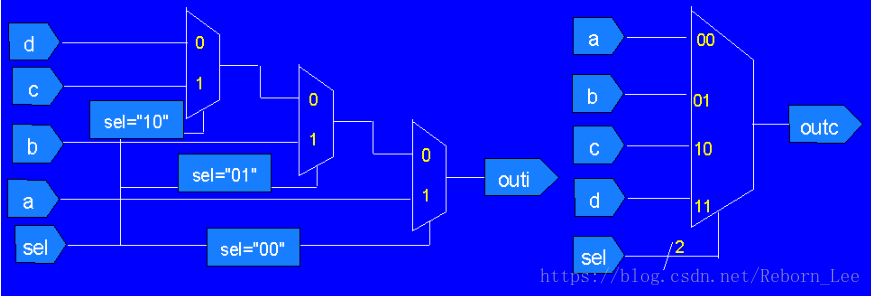

- case通常会综合成一级多路复用器(图的右边部分),而 if...else...则综合成优先编码的串接的多个多路复用器,如图的左边部分。通常使用case语句要比if语句快,优先编码器的结构仅在信号的到达有先后时使用。条件赋值语句也能综合成多路复用器,而case语句仿真要比条件赋值语句快。

- 所有的case 应该有一个default,允许空语句,即:

case

...

default: ;

endcase

这篇博文暂时就到这里,当然需要注意的地方还有很多,我们以后继续更新。更新包括对本博客的修改以及添加,根据实际检验而解释。

例如:下面这句话我就没有说太多的话,因为我还不太清楚。在以往的电路设计中很少使用函数和任务,所以得先学习学习然后实践下。

用一个函数(function)来代替表达式的多次重复,经常使用的一组描述可以写到一个任务中。

【Verilog HDL】函数(function)与任务(task)简单介绍

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/82193464

- 点赞

- 收藏

- 关注作者

评论(0)