Spartan-6的时钟资源、全局时钟缓冲器/多路复用器

时钟资源

时钟布线资源具有高速、低SKEW的特点,它对系统设计非常重要,即使系统速率不高,也应该关注时钟设计,以消除潜在的时钟危险。Spartan-6器件包含16个全局时钟资源和40个I/O区域时钟资源。全局时钟用于系统时钟,而I/O区域时钟专用于I/O串行/解串(ISERDES和OSERDES)设计。

Spartan-6时钟资源包含以下4种。

包括由BUFGMUX驱动的全局时钟网络和由I/O时钟缓冲器(BUFIO2)、PLL时钟缓冲器(BUFPLL)驱动的I/O区域时钟网络。

一、 时钟输入

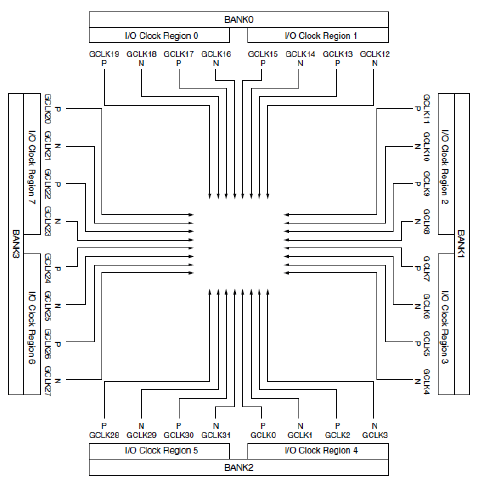

每个Spartan-6有32个全局时钟输入引脚,分布在FPGA的四周。时钟输入引脚在片上的分布图如图2-5所示。时钟输入引脚接收外部时钟信号,直接连接片内的DCM/PLL/BUFGMUX/BUFIO2。时钟输入引脚不连接时钟时,用作普通I/O。

一个差分时钟输入需要两个全局时钟输入。成对的时钟输入在标号上是连续的,例如,GCLK0和GCLK1是差分对,GCLK20和GCLK21是差分对。每个全局时钟缓冲器有两个时钟输入,Spartan-6支持最多16对的差分全局时钟输入。

设计中的时钟输入引脚连接IBUFG原语,通常综合工具会分析设计,自动将顶层时钟引脚推演为与IBUFG相连。如果需要更多IBUFG的控制功能,可以通过例化IBUFG的方式,将IBUFG的I端口连到顶层端口,将O端口连接到DCM、BUFG或通用逻辑。

HDL代码中例化全局输入缓冲器(IBUFG)的原语参见表2-6。

原文地址:点击打开链接

全局时钟缓冲器/多路复用器

Spartan-6的时钟缓冲器/多路复用器(BUFG或BUFPLL)可以直接驱动时钟输入信号到时钟线上,或者通过多路复用器在两个不相关的信号甚至异步时钟信号中切换。

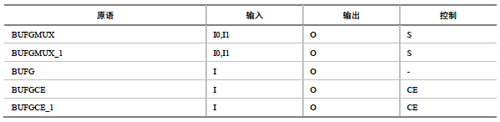

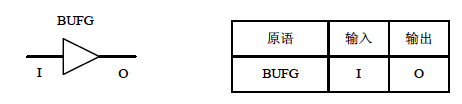

全局时钟缓冲器的原语如表2-7所示。

(1) BUFGMUX。

BUFGMUX可以作为一个BUFG,或者作为两个全局时钟源的多路选择器在两个时钟源之间切换。BUFGMUX只驱动全局时钟布线资源。通用布线资源也能驱动FPGA逻辑触发器上的时钟输入,但是通常不推荐使用,因为通用布线资源有较高的SKEW。

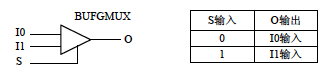

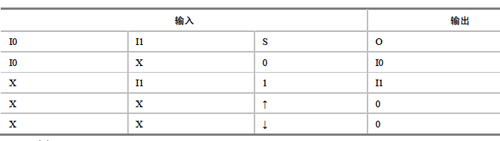

如图2-6所示,BUFGMUX是具有两个时钟输入I1 和I0、一个时钟输出O和一条选择线S的时钟缓冲器,可以消除两个时钟源之间切换时产生毛刺信号。选择线S必须满足建立时间要求,违反这一建立时间可能导致毛刺信号。

选择线S翻转选择另一个时钟源输出时,输出保持在一个非活动态直到下一个有效时钟沿到来。当两个时钟切换时,输出电平可以为高电平或低电平,缺省为低电平。交叉解耦寄存器确保了BUFGMUX 输出不会产生一个时钟脉冲边沿。

当S输入改变时,输出保持为Low,直到另一(待选)时钟从High 转为Low。然后,新的时钟开始驱动输出,如表2-8 所示,由于输入第一个低到高的跳变输出不翻转,所以,输出不会比最短输入时钟脉冲短。

S输入为低,选择时钟输入I0;S输入为高,选择时钟输入I1。BUFGMUX还具有内置可编程极性,等效于交换I0和I1。每个触发器可以对时钟信号进行极性设置,确定上升沿或下降沿触发,避免产生两个不同的时钟信号。

(2) BUFGMUX_1。

BUFGMUX_1和BUFGMUX功能相同,区别在于BUFGMUX_1对上升沿敏感,并且在输入切换之前保持为High。

(3) BUFG。

如图2-7所示,BUFG其实就是具有一个时钟输入和一个时钟输出的时钟缓冲器,它也是Virtex 和Spartan器件中时钟缓冲器的通用原语。

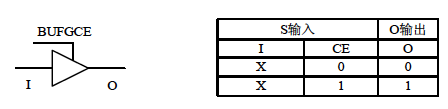

(4) BUFGCE 和BUFGCE_1。

BUFGCE是具有一个时钟输入、一个时钟输出和一条时钟使能线的时钟缓冲器。当时钟使能CE为高,输入I 经缓冲器输出;当CE为低(非激活状态),输出O为低。其原语如图2-8所示。

BUFGCE_1与BUFGCE功能相同,不同的是,当时钟使能CE为低时,输入I 经缓冲器输出;当CE为高(非激活状态),输出O为高。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/80351143

- 点赞

- 收藏

- 关注作者

评论(0)