Virtex中的ILA属性、VIO属性

ILA属性

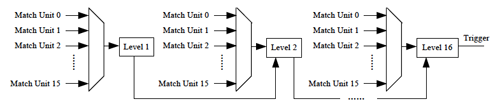

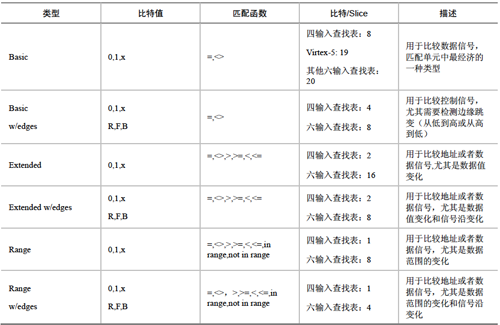

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者创建一个新的IP核工程。【View by function】→【Debug & Verification】→【ChipScope Pro】,双击ILA。弹出ILA触发和配置界面,如图9-7所示。

(1) 【Component Name】:输入组件名称。

(2) Trigger Port Settings选项组:触发端口设置。

(3) Storage Settings 选项组:存储选项设置。

设置好ILA核的触发和存储选项后,单击【Next】。进入ILA触发端口设置界面,如图9-9所示。

(4) Trigger Port 1选项组:触发端口1选项组。

配置完毕后,会在界面右侧的【Core Utilization】栏自动给出核所占用的资源。

说明:

(1) “0”表示“逻辑0”,“1”表示“逻辑1”,“X”表示“未知”,“R”表示“从0到1的跳转”,“F”表示“从1到0的跳转”,“B”表示“任何电平跳转”。

(2) 比特/Slice数值只是说明不同匹配单元的大致资源利用率,不能用精确的硬件资源消耗评估。

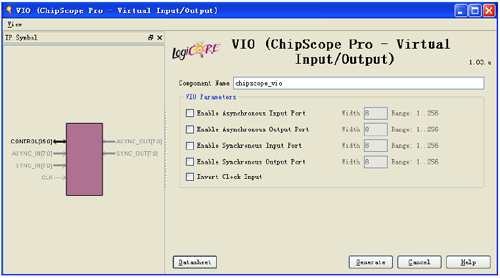

VIO属性

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者创建一个新的IP核工程。【View by function】→【Debug & Verification】→【ChipScope Pro】,双击VIO。弹出VIO配置界面,如图9-10所示。

(1) 【Component Name】:输入组件名称。

(2) VIO Parameters选项组:VIO参数选项组。

注意:只有使用同步输入和/或输出的时候,时钟信号翻转才有效。

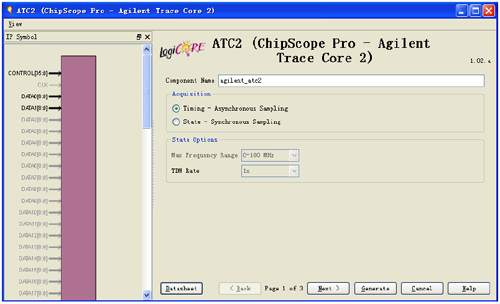

9.2.4 ATC2属性

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者创建一个新的IP核工程。【View by function】→【Debug & Verification】→【ChipScope Pro】。双击ATC2,弹出ATC2配置界面,如图9-11所示。

(1) 【Component Name】:输入组件名称。

(2) Acquisition选项组:

(3) State Options:状态选项组。

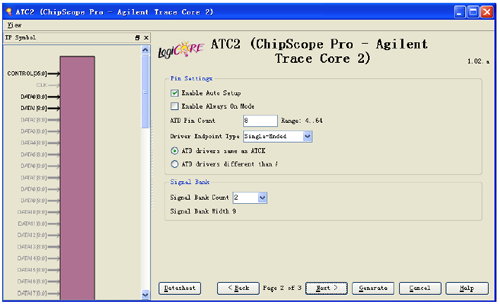

设置好后,单击【Next】,弹出引脚设置界面,如图9-12所示。

(4) Pin Settings选项组:引脚设置选项组。

(5) Signal Bank选项组:Signal Bank设置选项组。

单击【Next】,出现ATC2核ATCK和ATD引脚参数,如图9-13所示。

输出时钟(ATCK)和数据(ATD)引脚在ATC2核内例化,因此用户不用在顶层设计中手动设计,只需在内核产生器中指定这些引脚的位置和属性。这些引脚属性添加在ATC2核的*.NCF文件中。在引脚参数表中,可以设置ATCK和ATD引脚的位置、I/O标准、输出驱动和歪斜率。

(6) Pins选项组。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/80354534

- 点赞

- 收藏

- 关注作者

评论(0)