ChipScope Pro内核生成器应用实例

ChipScope Pro内核生成器应用实例

下面通过一个简单8位计数器的例子,了解如何在工程中添加ChipScope Pro内核生成器的各个IP核,对FPGA内部节点和逻辑进行观测。在该实例中,我们将调用一个ICON、一个ILA和一个VIO。

1. 新建项目工程和RTL程序。

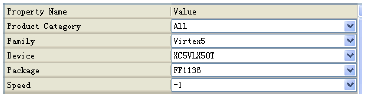

(1) 新建工程,选择器件型号、封装等项目信息,如图9-14所示。

(2) 编写或添加源程序count_top.v。

count_top.v

module count_top(clk, reset

);

input clk;

input reset;

reg [7:0] count_out;

always @(posedge clk) begin

if (reset == 0)

count_out <= 0;

else

count_out <= count_out + 1;

end

endmodule

2. 生成ICON核。

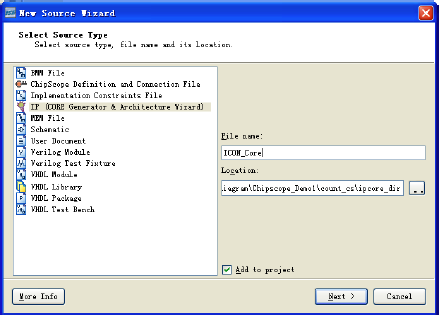

(1) 在ISE环境下,单击【Project】菜单→【New Source】,弹出源程序设置界面,选择源程序类型【IP (Core Generator & Architecture Wizard)】,输入将要生成的IP核名,如ICON_Core,如图9-15所示。

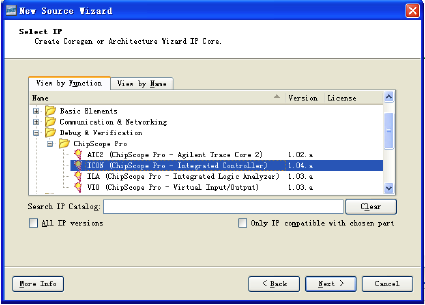

(2) 单击【Next】,弹出内核生成器的IP列表,选择【View By Function】→【Debug & Verifictation】→【Chipscope Pro】→【ICON(ChipScope Pro-Integrated Controller)】,如图9-16所示。

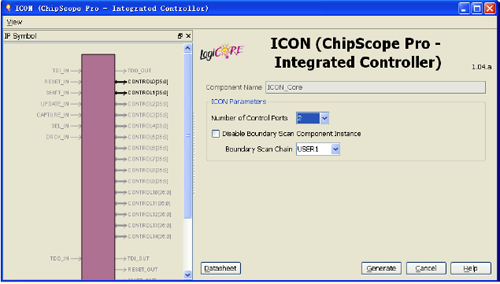

(3) 单击【Next】,进入ICON配置页面,由于本例要用两个调试内核ILA和VIO,因此ICON需要两个控制口,设置【Number of Control Ports】为2。如图9-17所示。

(4) 单击【Generate】,生成ICON核。

3. 生成ILA核。

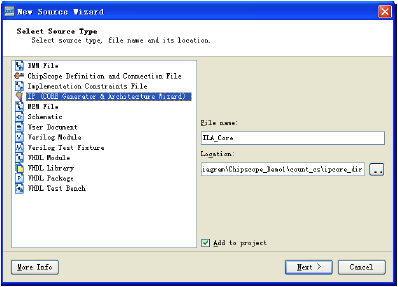

(1) 回到ISE界面,【Project】→【New Source】,弹出源程序设置界面,选择【IP (Core Generator & Architecture Wizard)】,输入将生成的IP核名,如ILA_Core,如图9-18所示。

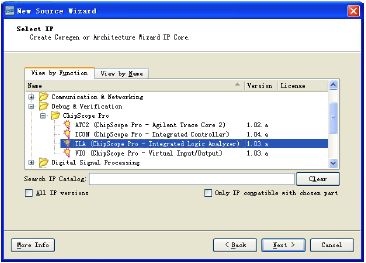

(2) 单击【Next】,进入内核生成器的IP列表,单击【View By Function】→【Debug & Verifictation】→【Chipscope Pro】→【ILA(ChipScope Pro-Integrated Logic Analyzer)】,如图9-19所示。

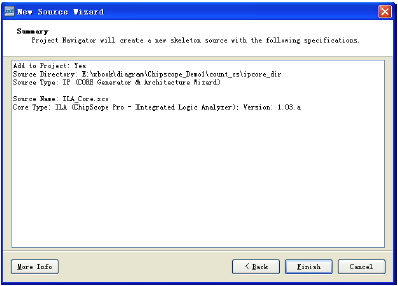

(3) 单击【Next】,弹出ILA Summary界面,如图9-20所示。

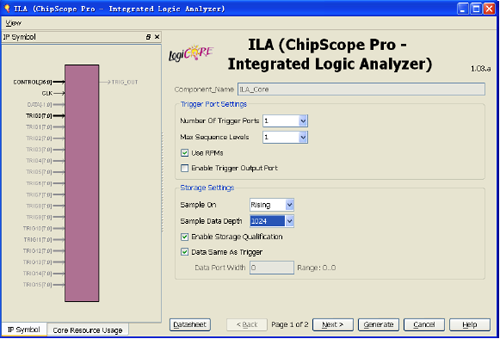

(4) 单击【Finish】,进入ILA配置页面一,配置触发端口和存储属性,如图9-21所示。

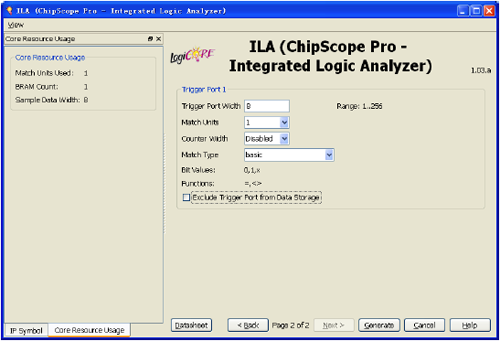

(5) 单击【Next】,进入ILA配置页面二,按图9-22所示配置触发条件。

(6) 单击【Generate】,生成ILA核。

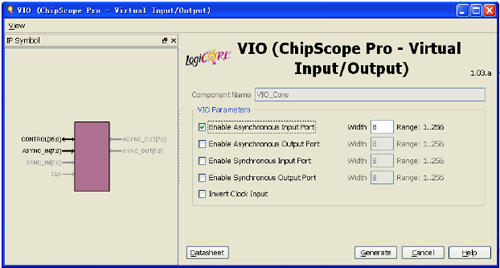

4. 生成VIO核。

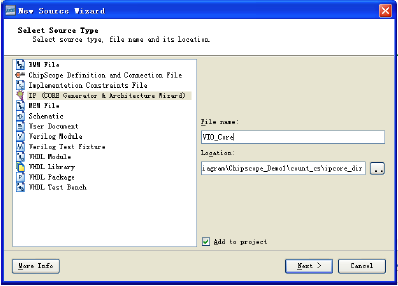

(1) ISE界面,【Project】→【New Source】,弹出源程序设置界面,选择【IP (Core Generator & Architecture Wizard)】,输入将生成的IP核名,如VIO_Core,如图9-23所示。

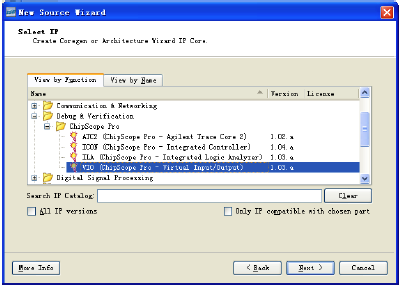

(2) 单击【Next】,进入内核生成器的IP列表,【View By Function】→【Debug & Verifictation】→【Chipscope Pro】→【VIO(ChipScope Pro-Virtual Input/Output)】,如图9-24所示。

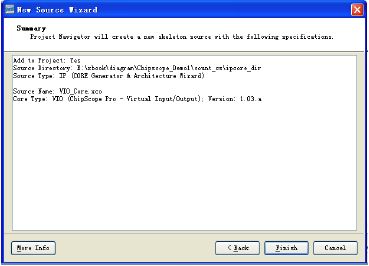

(3) 单击【Next】,弹出VIO Summary界面,如图9-25所示。

(4) 单击【Finish】,进入VIO配置页面,如图9-26所示,VIO参数。该例设置允许异步输入,宽度为8位。

(5) 单击【Generate】生成VIO核。

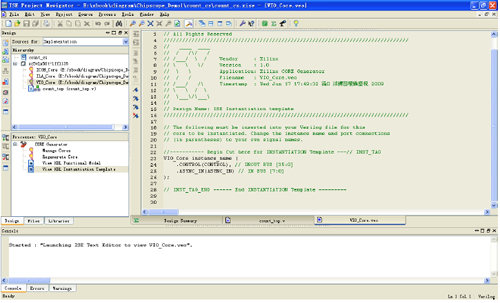

5. 例化ICON、VIO、ILA核。

(1) ISE环境下,生成ICON、VIO、ILA核的例化模板,如图9-27所示。

(2) 修改count.v代码,连接端口。

module count_top(clk, reset

);

input clk;

input reset;

reg [7:0] count_out;

wire [35:0] CONTROL0;

wire [35:0] CONTROL1;

always @(posedge clk) begin

if (reset == 0)

count_out <= 0;

else

count_out <= count_out + 1;

end

ICON_Core U1 (

.CONTROL0(CONTROL0), // INOUT BUS [35:0]

.CONTROL1(CONTROL1) // INOUT BUS [35:0]

);

VIO_Core U2(

.CONTROL(CONTROL0), // INOUT BUS [35:0]

.ASYNC_IN(count_out) // IN BUS [7:0]

);

ILA_Core U3(

.CONTROL(CONTROL1), // INOUT BUS [35:0]

.CLK(clk), // IN

.TRIG0(count_out) // IN BUS [7:0]

);

Endmodule

6. 生成比特流。在ISE的【Process】里,进行综合、实现、生成比特流。下载到FPGA里。

7. 打开ChipScope Analyzer,对采样数据进行分析。ChipScope Analyzer在后面小节中介绍。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/80354570

- 点赞

- 收藏

- 关注作者

评论(0)