ChipScope Pro内核插入器

ChipScope Pro内核插入器

ChipScope Pro内核插入器的文件后缀名为cdc。在ISE工程中可以创建一个新的cdc程序,也可以在实现流程中激活内核插入器。

注意:使用内核插入器之前,要注意一些工程项目的属性设臵。

(1) 如果采用XST综合工具,将【Keep Hierarchy】属性设置成【Yes】或【Soft】,禁止XST工具对设计的优化,保留原来设计层次,同时也保留了NET网络节点名称。设置方法如下。

(2) 正确设置比特流生成选项。

接下来,介绍如何在ISE的环境下调用ChipScope的内核插入器(Core Inserter),以及内核插入器的各种参数的含义及其配置方法。

1. 运行ISE 11.1,打开设计的工程项目。

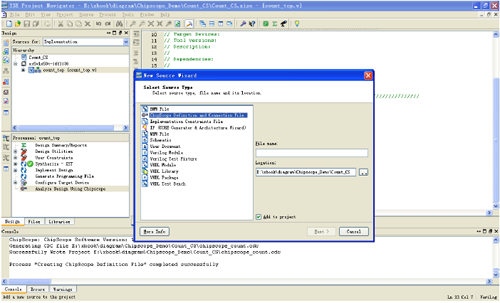

2. 创建CDC文件。在ISE11.1的界面下,有两个创建CDC文件的方法:

注意:只有安装了ChipScope Pro 11.1,才可以在ISE 11.1的【New Source】里出现【ChipScope Definition and Connection File】。

3. ChipScope内核插入器的属性和参数设置。

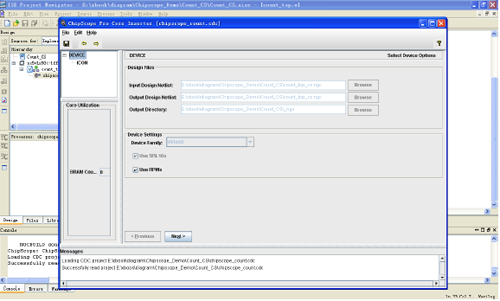

(1) 在【Sources in Project】窗口中,双击cdc文件。弹出的内核插入器界面如图9-29所示,设置Chipscope Pro的参数。

菜单栏中的菜单项及其功能有:

指定输入设计的网表

单击【Browse】,选择输入设计所在的目录

修改输出设计网表和输出目录(如果核插入器在ISE里激活,那么输入网表和输出网表、目录、器件型号等参数自动填入,在这钟情况下,这些参数只能在ISE工程属性中修改,不在核插入器里修改。)

工程参数

【Device Setting】器件设置选项组:

注意:只有Spartan-3、Spartan-3E、Spartan-3A、Spartan-3A DSP和Virtex-4器件家族显示ChipScope核资源利用特性。

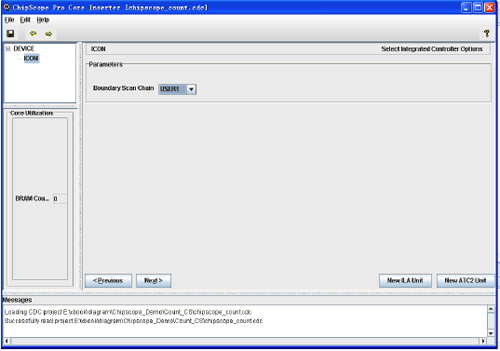

(2) ICON核配置选项设置。在图9-29中单击【Next】,弹出ICON核配置选项设置界面,如图9-30所示。

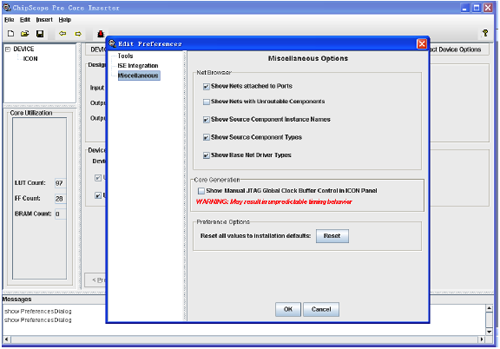

打开【Edit】菜单→【Preferences】属性,弹出【Edit Preferences】属性编辑对话窗,如图9-31所示。

使能JTAG全局时钟缓冲器控制:在【Miscellaneous】选项卡里,【Show Manual JTAG Global Clock Buffer Control in ICON Panel】复选框选中。

禁止JTAG时钟上的BUFG:【Put JTAG Clock on a Global Clock Buffer】复选框不选中。

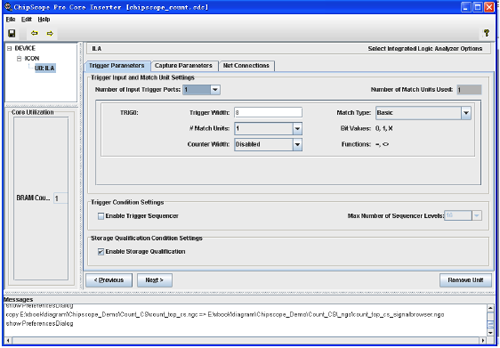

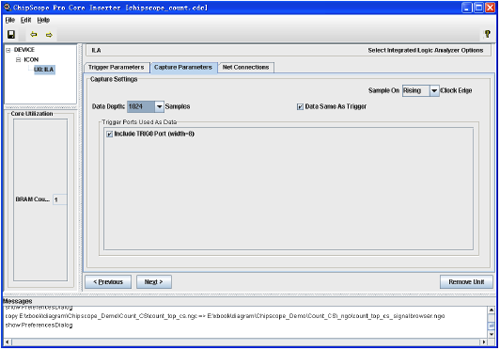

(3) 在图9-30中单击【New ILA Unit】,弹出ILA触发选项和参数设置界面,如图9-32所示。

Trigger Parameters选项卡:

【Number of Input Trigger Ports】下拉列表框:选择ILA核输入触发端口数目,ILA核最多支持16个输入触发端口。每个触发端口的参数在下方列出,包括触发宽度、触发匹配条件判断类型和数目。

TRIGn选项组:

【Trigger Width】编辑框:触发端口由一条或者多条信号线组成,信号线的总数成为触发宽度,最大为256。

【# Match Unit】下拉列表框:触发比较匹配单元是个比较器,和触发端口相连,用于检测触发端口是否满足设定的条件。每个触发端口可以有1~16个触发匹配单元。触发匹配设置单元设置的越多,触发事件就越灵活,但是要占用更多的内部资源。在满足条件的情况下,尽量减少触发匹配单元的数量。

【MatchType】下拉列表框:请参见表9-1。

【Count Width】下拉列表框:匹配单元计数器宽度,用于选择满足匹配条件的次数,最大32位。

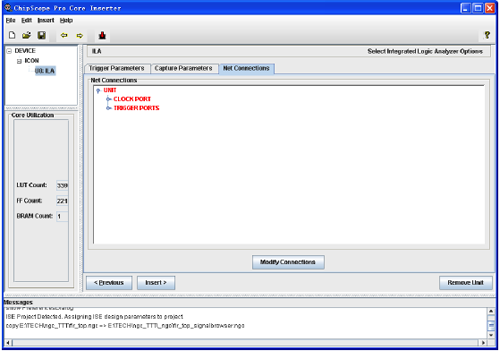

Net connections选项卡(参见图9-34)。

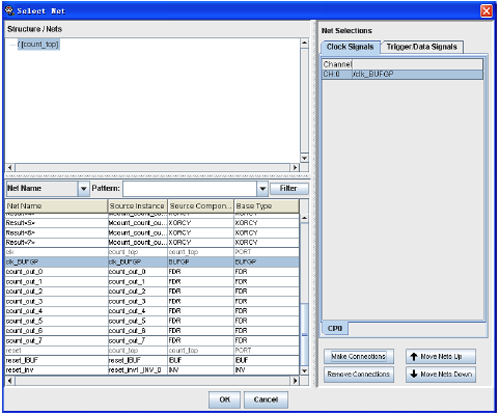

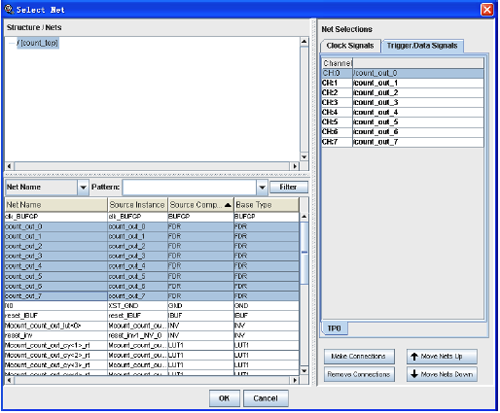

在【Structure/Nets】中,选择想要连接到ChipScope核的网络节点(可以配合Shift/Ctrl键,选择多个网线)。在【Net Selections】中选择【Clock Signals】、【Trigger Signals】或【Data Signals】选项卡,选择想用于连接网络节点的通道,例如CH0,单击【Make Connections】按钮建立网络节点与ChipScope内核的连接,如图9-36所示。

ChipScope Pro只能分析FPGA内部逻辑信号,不能直接连接到FPGA的输入,所以输入信号全部以灰色显示,如图9-35所示的clk、reset信号。如果要观察输入信号,可连接此输入信号的输入缓冲器的输出来实现,时钟信号选择相应的BUFGP,如图9-36所示的clk_BUFGP信号,普通信号选择相应的IBUF。

连接完成后,单击“OK”按钮返回连接显示界面,发现所有提示字符“UNIT”、【CLOCK PORT】以及【TRIGGER PORTS】没有红色,则单击【Return Project Navigator】,退出Chipscope,返回到ISE 中。

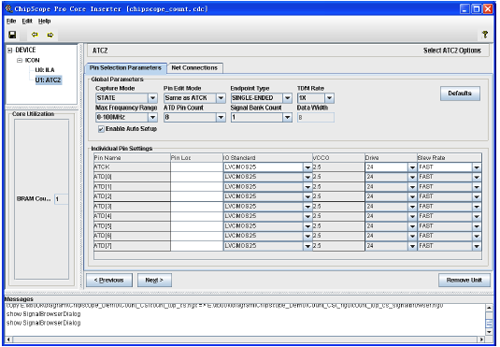

(4) 在图9-30中单击【New ATC2 Unit】,弹出ATC2的选项和参数设置界面,如图9-37所示。

Pin Selection Parameters选项卡。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/80354584

- 点赞

- 收藏

- 关注作者

评论(0)