FPGA从Xilinx的7系列学起(2)

1. 最基本的CLB

CLB是FPGA最最基本的单元,不能说是类似于质子和中子的概念,但也至少是原子和分子的概念了。如果是最根本的单元都无法能够很好的理解,那么其实很多FPGA的原理还是停留在一个写写代码,调调时序的小工程师的级别。我想,这应该不是我们所有年轻人的一个追求。

1.1 CLB的初探

首先CLB的最基本资源分为两种,一种是实现组合逻辑资源功能的,一般称为LUT。XILINX的LUT是6输入查找表。一种是Flip-flop,也就是经常听课大家听说的FF,我就觉得这个FF就是寄存器。

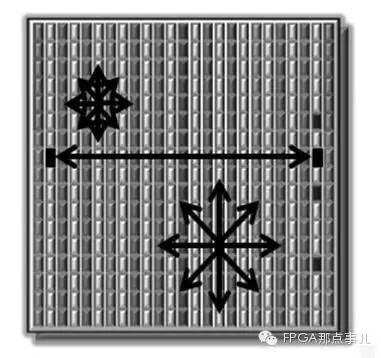

我上面的那个图很经典。大家可以看到,一个CLB就是分为两个Slice。Slice通过Matrix Switch(我很想给他起个中文名字,但是有时候我觉得这个中文名字怎么都不太好表达这个意思,就比方,“忽悠”这个中国词语,就很难找到英文和他对应)和其他的Slice链接到一起。

同时又有进位链通过垂直方向和它上面的Slice连接到了一起。如果这个进位链能够很好的使用,能够节省不少的资源。这个地方就记着有这么个概念就行。

又是一个很经典的图。既然我们知道了CLB的内部的一些东西,那么CLB又是怎么相连的呢?这个问题通过我们的经典图形,很清晰的表现出来。CLB是成对的对称的连接在了一起。这样布局的最大好处是什么呢?

首先是增加了芯片的资源数量,同时通过通过共享时钟走线节省了很多资源。这个一个增加一个减少都是帮助大家能够用FPGA的时候能够获得最大的资源享受。也算是花小钱办大事。(这个涉及到了硅片的概念,就不展开去描述了。和大家的设计需求无关。)

另外这种分布的好处和大家相关的好处,大家觉出来是什么了么?这个最大的好处是可以让大家共享一些资源,增加大家布局的时候的资源,这样更容易实现自己的设计。

1.2 CLB与其他资源的互联

CLB不仅仅是和其他资源相连,那么又如何和其他资源相连呢?一样,和CLB之间相连一样,通过Matrix Switch链接到一起。所有资源布线资源都是垂直,水平或者对角线的方向连在了一起。但是各个方向有不同的跨度。

水平方向上的跨度支持:1,2,4,12。

垂直方向上的跨度支持:1,2,16,18。

对角线方向上的跨度支持:1,2,16。

相比Virtex-6来说,垂直方向和对角线方向上的跨度已经做了很大的改进,跨度由原理Virtex-6的4变成了16,Long型有原来的12变成了18。长度的变化也有助于显着提高布通率。不过,布线资源的使用是由工具基于大家的时序约束自我进行的,也就是大家不用记住这些跨度的数量,因为到时候工具会根据你自己需要会自动进行相关布局布线的。

很多东西并不一定需要大家记住,只是大家再选择FPGA的时候做一个参考。因为我们肯定希望花最少的精力设计出一个最牛的设计。然后看着自己的设计,喝杯茶,笑到哭。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/80393380

- 点赞

- 收藏

- 关注作者

评论(0)