巴克码相关器的verilog HDL设计

【摘要】 巴克码相关器

巴克码相关器原理:巴克码相关器能够检测巴克码序列峰值,并且能够在1bits错误情况下检测巴克码序列峰值。

巴克码是20世纪50年代初R.H巴克提出的一种具有特殊规律的二进制码组。它是一个非周期序列,一个n位的巴克码(x1, x3, ... xn),每个码元只可能取值 +1或 -1 。而十一位的巴克码是11’b11100010010 。

巴克码检测器...

巴克码相关器

巴克码相关器原理:巴克码相关器能够检测巴克码序列峰值,并且能够在1bits错误情况下检测巴克码序列峰值。

巴克码是20世纪50年代初R.H巴克提出的一种具有特殊规律的二进制码组。它是一个非周期序列,一个n位的巴克码(x1, x3, ... xn),每个码元只可能取值 +1或 -1 。而十一位的巴克码是11’b11100010010 。

巴克码检测器输入是一位序列,需要先移至移位寄存器中,再将移位寄存器中的值与标准巴克码同或,通过判断同或值是否大于阈值来确定巴克码。

巴克码检测器的结构图如下:

其verilog HDL设计代码如下:

-

1. //2018/5/5

-

-

2. //巴克码相关器设计

-

-

3. //巴克码检测器输入是1位序列,需要先移至移位寄存器中,再将移位寄存器中的值与标准巴克码同或

-

-

4. //通过判断同或值是否大于阈值来确定巴克码。

-

-

5. module buc(clk, rst, din, valid, threshold);

-

-

6. input clk; //时钟

-

-

7. input rst; //异步复位信号

-

-

8. input din; //输入巴克码

-

-

9. input[3:0] threshold; //阈值信号

-

-

10. output valid; //当输入待检测信号满足阈值条件时,valid为1,否则为0.

-

-

11.

-

-

12. wire[10:0] data_buc;

-

-

13. wire[3:0] threshold;

-

-

14.

-

-

15. //巴克码检测器模块例化

-

-

16. buc_devider U1(.din_buc(data_buc), .threshold(threshold), .valid(valid));

-

-

17.

-

-

18. //数据接收模块例化

-

-

19. buc_recieve U2(.clk(clk), .rst(rst), .din(din), .dout_buc(data_buc));

-

-

20. endmodule

-

-

21.

-

-

22. //数据接收模块

-

-

23. module buc_recieve(clk, rst, din, dout_buc);

-

-

24. input clk;

-

-

25. input rst; //异步复位信号

-

-

26. input din; //待检测数据输入

-

-

27. output[10:0] dout_buc; //此模块输出,检测器模块的输入

-

-

28. reg[10:0] dout_buc;

-

-

29.

-

-

30. always@(posedge clk or negedge rst)

-

-

31. if(!rst) //异步复位信号有效

-

-

32. begin

-

-

33. dout_buc <= 11'b0;

-

-

34. end

-

-

35. else //每一个时钟上升沿到达时,接收一位数据到达移位寄存器

-

-

36. begin

-

-

37. dout_buc <= {dout_buc[9:0],din};

-

-

38. end

-

-

39.

-

-

40. endmodule

-

-

41.

-

-

42. //巴克码检测模块

-

-

43. module buc_devider(din_buc, threshold, valid);

-

-

44. parameter LENGTH = 11; //序列长度

-

-

45. parameter BUC = 11'b111_000_10010; //标准巴克码

-

-

46. input[10:0] din_buc; //输入的待检测序列

-

-

47. input[3:0] threshold; //阈值

-

-

48. output valid; //valid==1代表待检测序列满足检测要求

-

-

49. reg valid;

-

-

50.

-

-

51. reg[4:0] sum;

-

-

52. integer i;

-

-

53.

-

-

54. always@(din_buc) //每输入一位数据,din_buc变化一次,下面的语句也就执行一次

-

-

55. begin

-

-

56. sum = 0; //每次敏感元素变化时,sum清零

-

-

57. for(i = 0; i < LENGTH; i = i + 1)

-

-

58. if(din_buc[i]^~BUC[i] == 1) //逐位检测待检测序列,若与标准巴克码一致,则sum加1,否则减1

-

-

59. sum = sum + 1;

-

-

60. else

-

-

61. sum = sum - 1; //待检测数据11位,若有1位与标准巴克码不一样,则sum等于9,2位不一样,则sum等于7,全部

-

-

62. end //一致,sum等于11

-

-

63.

-

-

64. always@(sum or threshold) //sum和threshold成为敏感信号

-

-

65. begin

-

-

66. if(sum[4] == 0) //sum最大为11,用4位数据即可,此刻出现的第5位意思是若sum为负

-

-

67. begin

-

-

68. if(sum[3:0] >= threshold) //sum数值大于阈值,则满足要求,valid置为1

-

-

69. valid = 1;

-

-

70. else //否则valid清零

-

-

71. valid = 0;

-

-

72.

-

-

73. end

-

-

74. else

-

-

75. valid = 0;

-

-

76.

-

-

77. end

-

-

78.

-

-

79. endmodule

其测试文件如下:

-

1. //测试文件

-

-

2. `timescale 1ns/1ns;

-

-

3. module buc_tb;

-

-

4. reg clk, rst, din;

-

-

5. reg[3:0] threshold;

-

-

6. reg[32:0] data; //输入数据2为33位数据,即3个待检测序列

-

-

7.

-

-

8. initial //时钟生成,时钟周期为20ns

-

-

9. begin

-

-

10. clk = 1'b0;

-

-

11. forever

-

-

12. #10 clk = ~clk;

-

-

13. end

-

-

14.

-

-

15. initial

-

-

16. begin

-

-

17. rst = 1'b0; //异步复位信号

-

-

18. #5 rst = 1'b1;

-

-

19. end

-

-

20.

-

-

21. initial

-

-

22. begin

-

-

23. data = 33'b11100010011_11100010001_11100010010;

-

-

24. threshold = 4'b1001; //阈值为9,分析见buc.v

-

-

25. end

-

-

26.

-

-

27. integer i;

-

-

28. always@(posedge clk or negedge rst)

-

-

29. if(!rst) //复位信号有效

-

-

30. begin

-

-

31. din = 1'b0; //输入清零

-

-

32. i = 32; //i 赋值为32

-

-

33. end

-

-

34. else

-

-

35. begin

-

-

36. if(i == 0) //i == 0的意思是数据到最后一位,输入完成。

-

-

37. begin

-

-

38. din = data[i];

-

-

39. i = 32;

-

-

40. end

-

-

41. else

-

-

42. begin

-

-

43. din = data[i]; //输入正在进行中,每个时钟上升沿到达时,移入1位数据

-

-

44. i = i - 1;

-

-

45. end

-

-

46. end

-

-

47. //巴克码相关器的例化

-

-

48. buc v1(.clk(clk), .rst(rst), .din(din), .valid(valid), .threshold(threshold));

-

-

49.

-

-

50.

-

-

51. endmodule

-

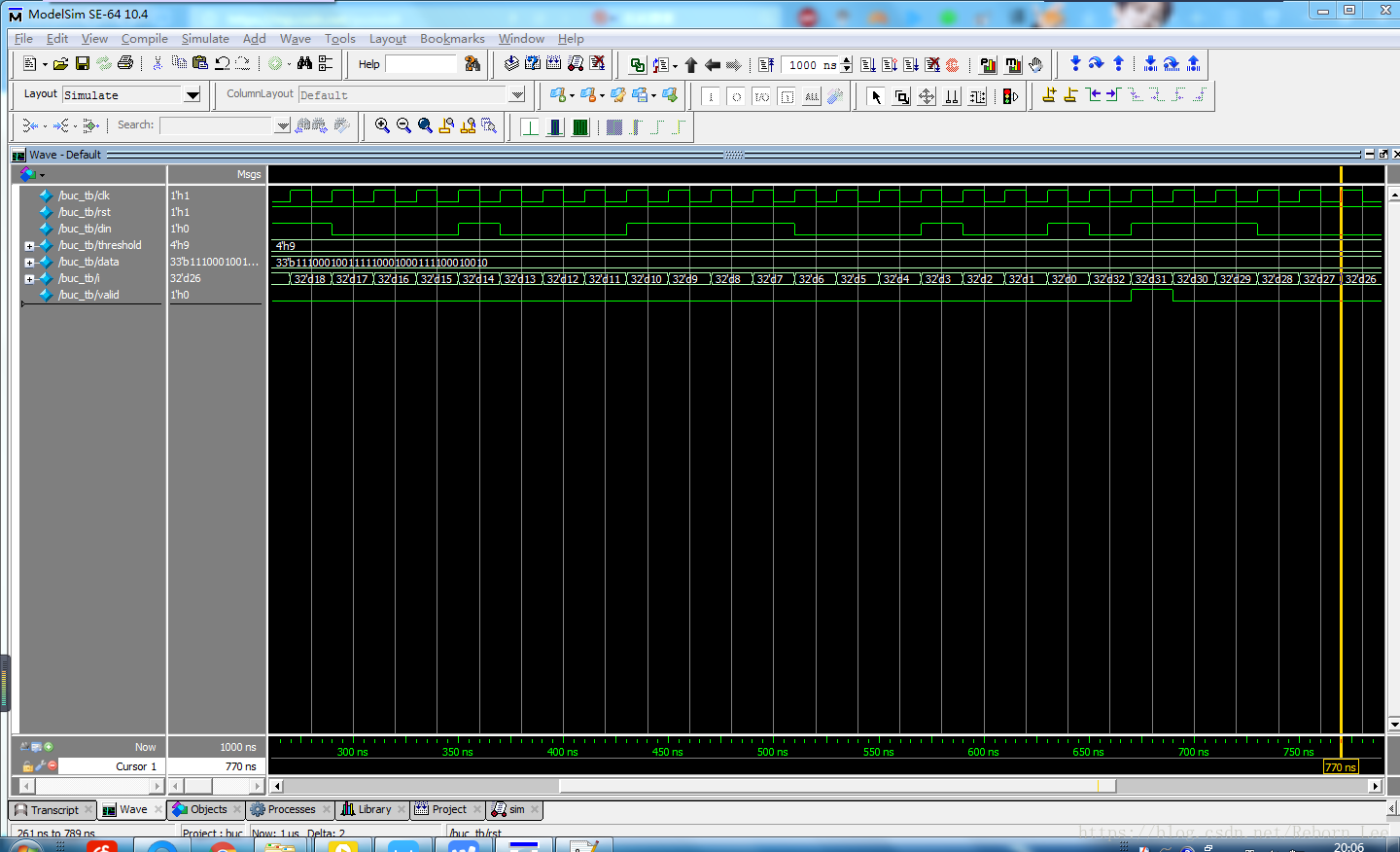

在Modelsim中仿真得到的波形图为:

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/80410951

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)