全过程实现一个最简单的FPGA项目之PWM蜂鸣器控制

目录

时间不饶人,我快速记录一下这个过程吧。

简单介绍:

蜂鸣器是一种最简单的发声元器件,它的应用也非常广泛,大都是作为报警或发声提醒装置。

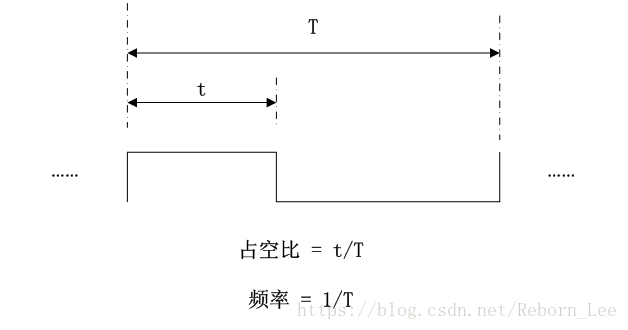

PWM即脉冲宽度调制,PWM的输出只有高电平1和低电平0。PWM不停的重复输出周期为T,其中高电平1时间为t的脉冲,t/T是它的占空比,1/T是它的频率。

如下图是PWM信号:

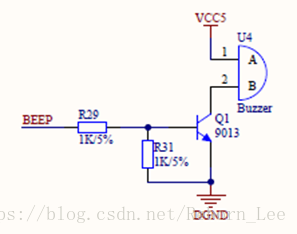

下面是蜂鸣器电路原理及结构:

如下图:

BEEP网络连接到FPGA的IO上,当BEEP = 1时,三极管Q1的BE导通,则CE也导通,那么U4的2端直接接地,因此在它两端有5V的电压,那么蜂鸣器就发声了。同理,BEEP = 0时,Q1截止,U4的2端相当于开路,则蜂鸣器不会发出声音。

如下图:

基于蜂鸣器在FPGA的IO输出1就发声、0则不发声的原理,我们给IO口一个占空比为50%的PWM的信号,让蜂鸣器间歇性的发声鸣叫。

如果它的频率高则发声就显得相对尖锐急促一些,如果它的发声频率低则发声就显得低沉平缓一些。

设计思路

我们期望产生一个输出频率为25Hz(40ms)、占空比为50%的PWM信号去驱动蜂鸣器的发声。

因此,我们使用系统时钟25MHz(40ns)进行计数,每计数1,000,000次,这个计数器就清零重新计算。此外,为了得到输出的PWM占空比为50%,那么我们只要判断计数值小于最大计数值的一半即500000时,输出高电平1,反之输出低电平0。

打开ISE,新建一个工程,然后添加一个源文件,用来设计该电路。

Xilinx虽然早已不更新ISE软件了,目前的主流是VIvado,但是这也不能否认ISE,也就是集成软件环境的强大与人性化,你把代码设计好,然后把各种约束设计好,整个过程,就只需要动动手指,就可以如行云流水般进行了。

Verilog HDL硬件语言描述:

-

`timescale 1ns / 1ps

-

//

-

// Company:

-

// Engineer:

-

//

-

// Create Date: 22:21:57 08/14/2018

-

// Design Name:

-

// Module Name: beep

-

// Project Name:

-

// Target Devices:

-

// Tool versions:

-

// Description:

-

//

-

// Dependencies:

-

//

-

// Revision:

-

// Revision 0.01 - File Created

-

// Additional Comments: get a 25Hz(40ms) signal to drive beep and system clock is 25MHz(40ns)

-

//

-

//

-

module beep(

-

input ext_clk_25m,

-

input ext_rst_n,

-

output beep

-

);

-

-

reg beep;

-

reg [19:0] cnt; //20 bit get the maximum number of 1048575;

-

-

//计数模块,计数达到1000 000次,计数器清零

-

always @ (posedge ext_clk_25m or negedge ext_rst_n)

-

begin

-

if(!ext_rst_n)

-

cnt <= 20'b0;

-

else if(cnt < 20'd999_999)

-

cnt <= cnt + 1'b1;

-

else

-

cnt <= 20'b0;

-

-

end

-

-

-

always @ (posedge ext_clk_25m or negedge ext_rst_n)

-

begin

-

if(!ext_rst_n)

-

beep <= 1'b0;

-

else if(cnt < 500_000)

-

beep <= 1'b1;

-

else

-

beep <= 1'b0;

-

-

end

-

-

-

endmodule

如果觉得这个代码的注释比较少,那我把特权同学的代码也贴出来:

-

module sp6(

-

input ext_clk_25m, //外部输入25MHz时钟信号

-

input ext_rst_n, //外部输入复位信号,低电平有效

-

output reg beep //蜂鸣器控制信号,1--响,0--不响

-

);

-

-

//-------------------------------------

-

reg[19:0] cnt; //20位计数器

-

-

//cnt计数器进行0-999999的循环计数,即ext_clk_25m时钟的1000000分频,对应cnt一个周期为25Hz

-

always @ (posedge ext_clk_25m or negedge ext_rst_n)

-

if(!ext_rst_n) cnt <= 20'd0;

-

else if(cnt < 20'd999_999) cnt <= cnt+1'b1;

-

else cnt <= 20'd0;

-

-

//-------------------------------------

-

-

//产生频率为25Hz,占空比为50%的蜂鸣器发声信号

-

always @ (posedge ext_clk_25m or negedge ext_rst_n)

-

if(!ext_rst_n) beep <= 1'b0;

-

else if(cnt < 20'd500_000) beep <= 1'b1; //蜂鸣器响

-

else beep <= 1'b0; //蜂鸣器不响

-

-

endmodule

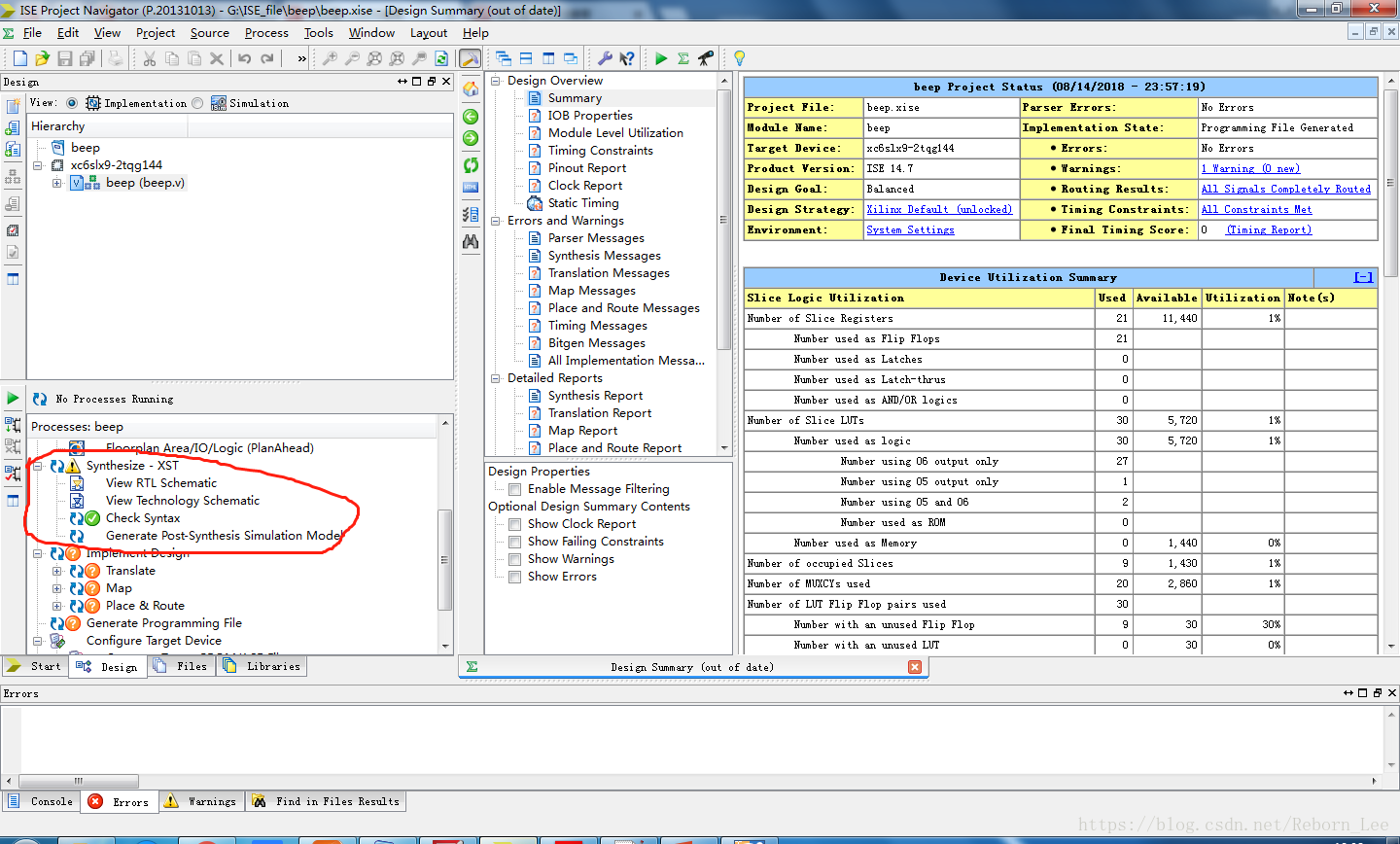

语言检测

代码输入进去之后,我们先测试一下代码是否正确,是否可以综合,需要先进行一下语法检测:

这里就省略了功能(行为)测试,因为我知道没问题。

由于这个小例子比较简单,用的FPGA资源也比较少,所以也没必须进行时序约束啦,时序约束省略。

引脚分配

之后在下图中的位置打开PlanAhead进行综合前的引脚分配:

引脚分配,就是要把硬件描述语言设计的电路的输入输出对应到你的FPGA开发板上,因此你需要知道自己的FPGA开发板的电路图,找到响应的引脚,对应下去:

我的练手的FPGA是Spartan-6,本实验要求的输入无非就是一个输入时钟,一个复位,输出就是一个beep,也就是蜂鸣器输出端。

找到对应的I/O端口:

![]()

![]()

将PlanAhead打开进行引脚分配,也叫引脚约束,然后保存约束,退出。

上图的中的引脚标准电压,为什么是LVCMOS33,我也不知道,我看特权的教程上就是这么用的。好像我用了别的也没有问题。知道了再说。

综合

之后我就可以进入综合的环节了:

同上,综合之后没什么问题,就可以直接进入实现阶段了,关于这些阶段是什么意思,可见我的另一篇博文:Xilinx FPGA开发流程

这是一篇纯理论分析的博文,本博文算是实践性的博文了。

实现

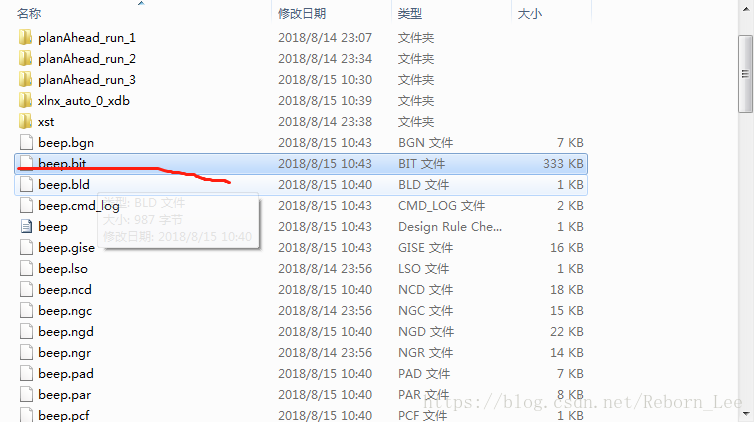

实现包括,转换、映射、布局布线,这三个过程没问题,我就可以进行下一步,产生一个可配置文件了,也就是一个bit流文件。

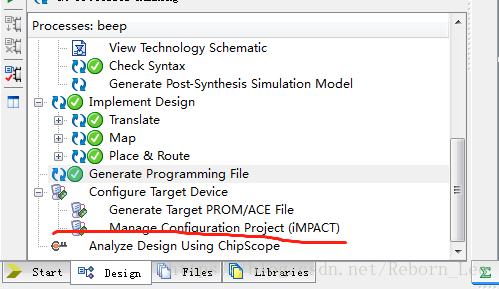

器件配置

之后就可以下载把FPGA开发板上进行调试了:

给FPGA上电,然后把仿真器都连接好,就可以进行如下步骤:

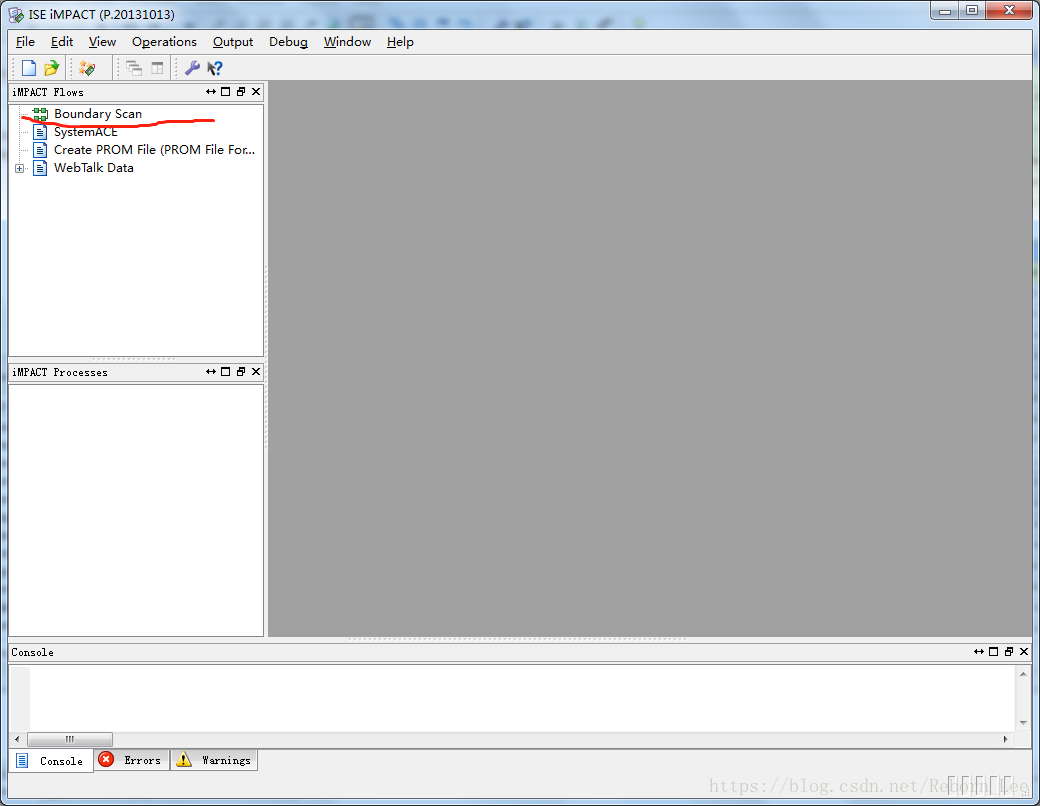

双击IMPACT,出现一下界面并点击Boundary Scan(边界扫描):

右击空白区域,添加Xilinx设备,选择beep.bit:

右击下图中的Xilinx 设备,然后Program:

Program成功之后,你的FPGA上的蜂鸣器就响了。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/81676672

- 点赞

- 收藏

- 关注作者

评论(0)