解读ADC采样芯片(EV10AQ190A)的工作模式(四通道模式)

上篇博文讲了EV10AQ190A这种ADC芯片的工作模式:双通道模式

我十分重视这些内容,因为这是我认识硬件工作模式的起点,当然这也只是理论上的内容,实际采样过程中也许会遇到这样那样的问题,那就需要自己慢慢探索了,理想与工程还是会有一定的差距的!

这篇博文主要讲四通道模式:

这种模式的框架或者组态(configuration)(我真的不知道这个单词如何用中文准确的翻译处理,我总感觉应该是原理框图),算了以后就叫做组态吧,强行翻译。

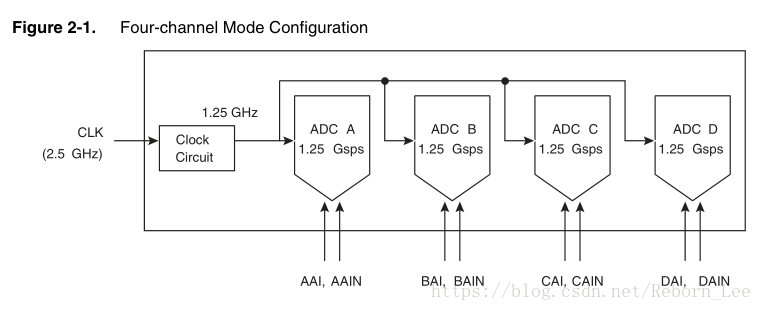

由上图可知,四通道模式有4个输入端口,我们分别称其为A端口,B端口,C端口,与D端口,四个端口分别对应四个通道,也就是说四个输入端口中每个端口分别对应一个ADC采样通道,例如当模拟输入从A端口输入时,就有ADC A进行采样。

从上图我们还可以得知,外部2.5GHz的时钟为该ADC芯片提供时钟源,进入内部时钟电路(Clock Circuit),内部时钟电路相当于一个二分频的作用,产生1.25GHz的时钟信号分别输入四个通道,为其提供时钟信号。

每个通道都是一个ADC核,所以说这个ADC有四个核,(有关这里的时钟关系等我单独一篇博文研究吧!)。

每一个ADC核采样速率都是1.25Gsps,也就是说每秒采样1.25G个点!

下面看看其时序图:

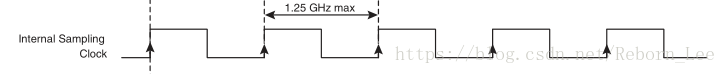

四通道模式的时序图可以说很简洁了。

模拟输入XAI与基准时钟CLK:

这个时钟频率最大为2.5GHz;

CLK时钟二分频得到ADC内部采样时钟:

频率为CLK的一半,最大为1.25GHz;

基准时钟CLK四分频得到采样数据同步时钟:

这个时钟频率就更低了,为基准时钟CLK的1/4;

内部采样时钟的上升沿到达时,开始采样,分别为N,N+1,...

每一个核(每一个通道)每秒采样1.25G个数据点;

同样该模式也采样了流水线结构,ADC的任一个通道采样得到数据后,这时数据的同步也就开始了,关于ADC怎么知道什么时候同步的问题,我想暂且就认为采样得到数据后,内部发出一个信号,这个信号通知ADC该同步了。

最后贴出部分代码,此代码讲了写此程序的部分思路,好多东西需要自己往里面填写,例如adc单通道模式采样模块肯定要用一个IP核产生采样数据,还有时钟产生模块等,这里仅仅为了理解上述同步过程而简写的几行代码!

module adc(...); //由于这是一个不完整的程序,所以省略了输入输出; wire syn_clk; //数据同步时钟,这个时钟一般是由fpga中的IP核产生 wire [9:0] ad_data_a; //adc采样得到的数据,对于四通道模式而言,此为A端口输入模拟信号,采样得到的数据 reg [9:0] ad_data1,ad_data2; //假设该寄存器变量用于存放adc采样得到的数据 //数据同步 always@(posedge syn_clk) //同步时钟上升沿到来时,同步一个数据 begin ad_data1 <= ad_data_a; end always@(negedge syn_clk) //同步时钟下降沿到来时,再同步一个数据 begin ad_data2 <= ad_data_a; end endmodule

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/81057253

- 点赞

- 收藏

- 关注作者

评论(0)