【FPGA】Spartan-6的时钟管理器(CMT)之数字时钟管理器(DCM)

目录

时钟管理器(CMT)

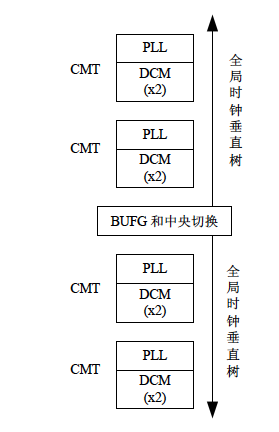

Spartan-6 CMT是一个灵活、高性能的时钟管理模块。它位于芯片中央、垂直的全局时钟网络旁。如图2-17所示,它包含一个PLL和两个DCM。

图2-17 Spartan-6 FPGA CMT片内布局图

DCM(digital clock manager)

组成结构

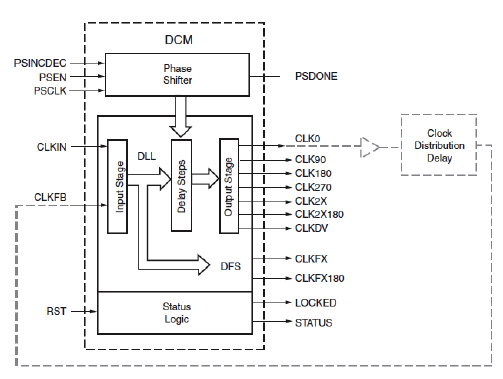

Spartan-6中的DCM,如图2-18所示,由4部分组成。

图2-18 DCM 功能结构图

(1) 延时锁相环(DLL)。

DLL 延时锁相环可以根据输入时钟去除DCM 的输出时钟歪斜,以完全消除时钟分布延迟。其原理是将时钟输入(CLKIN)与一个反馈输入(CLKFB)进行比较,然后控制延迟线选择器,通过在DLL 路径中加入合适的延迟直到CLKIN 与CLKFB 重合。

DLL 输入时钟是CLKIN 和CLKFB,输出时钟信号是CLK0、CLK90、CLK180、CLK270、CLK2X、CLK2X180 和CLKDV。

(2) 数字频率综合器(DFS)。

DFS有两个用户寄存器,用来设置相对于输入时钟(CLKIN)倍频(CLKFX_MULTIPLY)和分频(CLKFX_DIVID)系数。DFS可以单独使用,还可以和DLL一起配合使用;如果DFS不和DLL一起使用,CLKIN和DFS输出之间没有对应的相位关系。DFS的输出为CLKFX和CLKFX180。

(3) 相移单元(PS)。

相移单元PS的输入信号有PSINCDEC、PSEN和PSCLK,输出信号为PSDONE和STATUS[0]。相移模式包括固定相移和可变相移。

固定相移是指DCM的9个时钟的相位输出,通常是输入时钟周期的若干分之一,固定相移值在设计中设定并在FPGA配置时载入FPGA。

除了固定相移,PS还支持可变相移,根据系统要求,通过数字接口(PSINCDEC、PSEN和PSCLK)动态改变相移。每次动态改变的相移值为DCM_DELAY_STEP,DCM_DELAY_STEP对应的范围可参考《Spartan-6数据手册》。

(4) 状态逻辑。

状态逻辑反映DCM的状态,对应两个输出信号LOCKED和STATUS[0]。

DCM原语

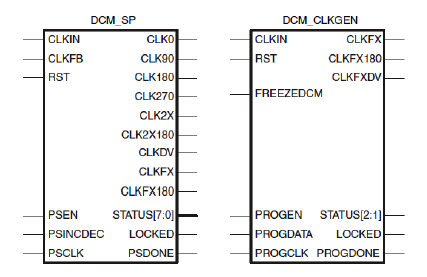

如图2-19所示,主要有2个DCM的原语调用,DCM_SP和DCM_CLKGEN。

图2-19 DCM原语

DCM_SP提供DCM的传统特性:时钟DESKEW、频率综合和固定及可变相移。

DCM_SP所有的属性都是在设计时确定,上电配置的时候编程到FPGA,除了动态相移功能外,所有的属性在运行时是不可以更改的。

DCM_CLKGEN提供了如下更多的DFS性能。

低抖动的CLKFX和CLKFX180输出。提高了输入时钟CLKIN的抖动容限。支持M和D的动态编程,动态设置CLKFX_MULTIPLY和CLKFX_DIVIDE。CLKFX_MULTIPLY和CLKFX_DIVIDE属性值范围更大。当输入时钟丢失时,自激振荡器工作。具有扩频功能。

在设计中特别要注意DCM_SP和DCM_CLKGEN的特性和参数,请参考《Spartan-6 时钟资源用户手册》。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/81288325

- 点赞

- 收藏

- 关注作者

评论(0)