通过仿真和综合认识T触发器(Verilog HDL语言描述T触发器)

这个系列的博文已经写过了两篇,分别是通过仿真和综合认识D触发器(Verilog HDL语言描述D触发器)和通过仿真和综合认识JK触发器(Verilog HDL语言描述JK触发器),分析的方法是完全并行的。

这里再看一下T触发器。

Verilog HDL程序描述

-

//设计1为T触发器,带有异步复位信号

-

module t_trigger(clk,t,rst,q);

-

-

input clk, t, rst;

-

output q;

-

reg q;

-

-

always@(posedge clk or posedge rst)

-

begin

-

if(rst) //复位信号有效, 输出清零

-

q <= 1'b0;

-

else if(t == 1'b1) //t为1时,输出翻转

-

q <= ~q;

-

else //否则,输出保持

-

q <= q;

-

-

end

-

-

-

endmodule

测试文件

-

//1位T触发器的测试文件

-

`timescale 1ns/1ps

-

module t_trigger_tb;

-

-

reg t;

-

reg clk;

-

reg rst;

-

wire q;

-

-

//时钟信号产生,周期为20ns

-

always

-

begin

-

#10 clk = ~clk;

-

end

-

-

//初始化

-

initial

-

begin

-

clk = 1'b0;

-

rst = 1'b0;

-

t = 1'b0;

-

#30 rst = 1'b1;

-

#10 rst = 1'b0;

-

#30 t = 1'b1;

-

#40 t = 1'b0;

-

-

end

-

-

t_trigger u1(.clk(clk), .rst(rst), .t(t), .q(q));

-

-

endmodule

仿真波形

从波形可以看出,前30ns的输出值不确定,这也在预料之内,由于此刻没有复位,所以输出值处于未知,所以直到复位前都将是不确定状态。后面也可以看出,T触发器的作用就是,时钟上升沿触发时刻,t 为0 时,输出保持,t为1时,输出翻转。

综合后:

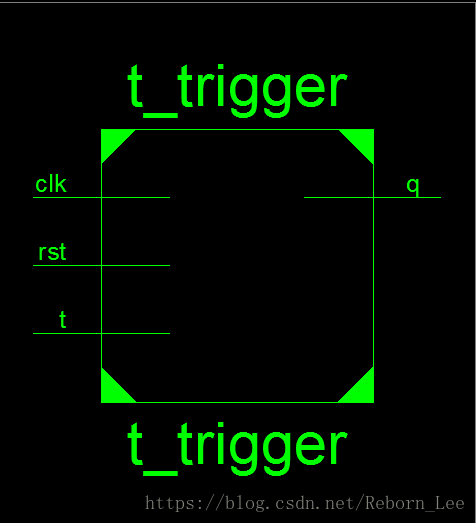

寄存器转换级电路(Register Transfer Level)

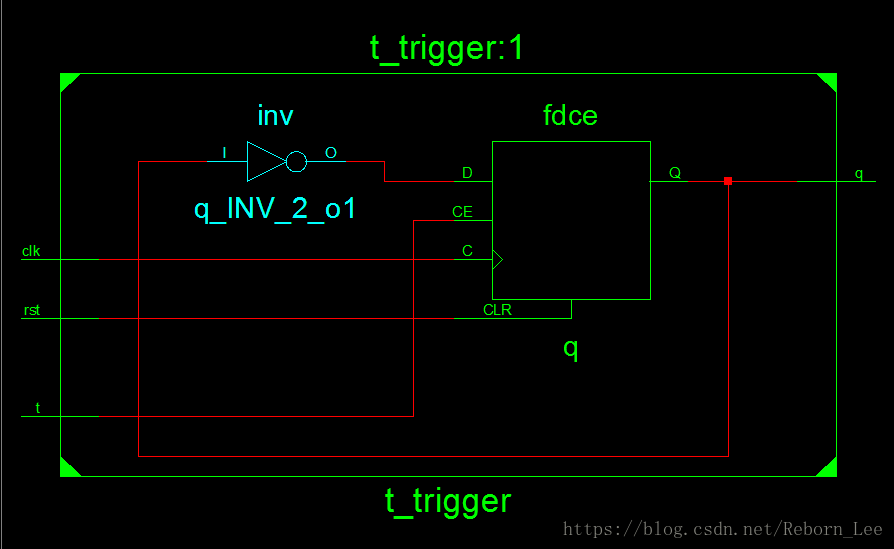

展开后:

这个电路比较有意思了,不复杂,由于是在FPGA中综合出来的电路,所以这个T触发器同样是由D触发器组成的,CE为使能端,CE与t相连,当t(CE)为1时,D触发器工作,由于D触发器的输出q经过一个反相器后与输入d相连,所以此时,输出q为q的前一个状态的翻转,即 。

。

同理当t为0时,时钟上升沿到来时,D触发器没有工作,所以输出保持原来的状态,即 。

。

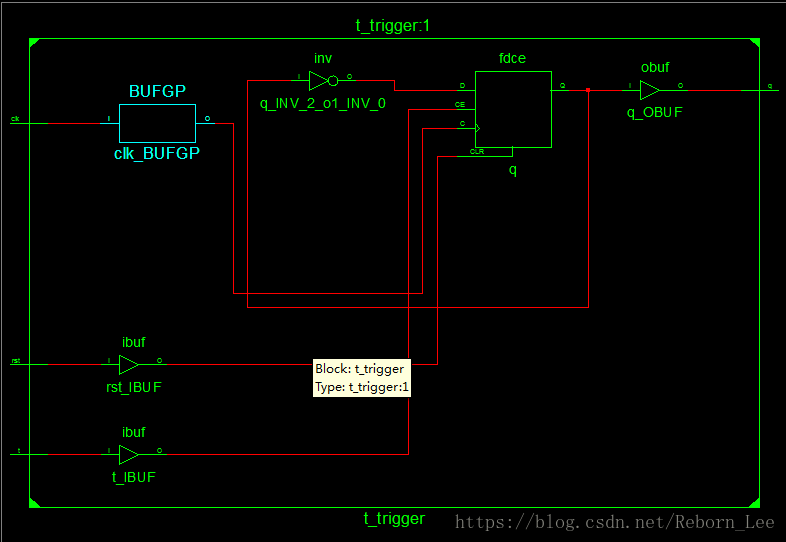

下面再看看Technology Schematic

时钟输入经过一个BUFGP,作用当然是全局时钟缓冲器了,这是FPGA电路里面的规矩,这个BUFGP的好处很多,相关的博文:【FPGA】IBUFG、IBUFGDS、IBUFDS...(这些到底是啥?),都是一类的东西。

这个电路的意思是,上面的RTL电路在FPGA中的实际体现。

由于FPGA中只有D触发器,所以在FPGA中也是由D触发器构成T触发器。

最后也同样给出T触发器的输入输出表格总结:

| T |  |

| 0 |  |

| 1 |  |

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/81332515

- 点赞

- 收藏

- 关注作者

评论(0)