组合逻辑和时序逻辑学习笔记

目录

数字逻辑电路的种类

组合逻辑

输出只是当前输入逻辑电平的函数(有延时),与电路的原始状态无关的逻辑电路。也就是说,当输入信号中的任何一个发生变化时,输出都有可能会根据其变化而变化,但与电路目前所处的状态没有任何关系。

时序逻辑

输出不只是当前输入的逻辑电平的函数,还与电路目前所处的状态有关的逻辑电路。

同步有限状态机

同步有限状态机是同步时序逻辑的基础。所谓同步有限状态机是电路状态的变化只可能在在同一时钟跳变沿时发生的逻辑电路。但状态是否发生变化还要看输入条件,如输入条件满足,则进入下一状态,否则即使时钟不断跳变,电路系统仍停留在原来的状态。利用同步有限状态机可以设计出极其复杂灵活的数字逻辑电路系统,产生各种有严格时序和条件要求的控制信号波形,有序地控制计算逻辑中数据的流动。

数字逻辑电路的构成

组合逻辑构成

由与、或、非门组成的网络。常用的组合电路有:多路器、数据通路开关、加法器、乘法器….

时序逻辑构成

由多个触发器和多个组合逻辑块组成的网络。常用的有:计数器、复杂的数据流动控制逻辑、运算控制逻辑、指令分析和操作控制逻辑。同步时序逻辑是设计复杂的数字逻辑系统的核心。时序逻辑借助于状态寄存器记住它目前所处的状态。在不同的状态下,即使所有的输入都相同,其输出也不一定相同。

组合逻辑举例

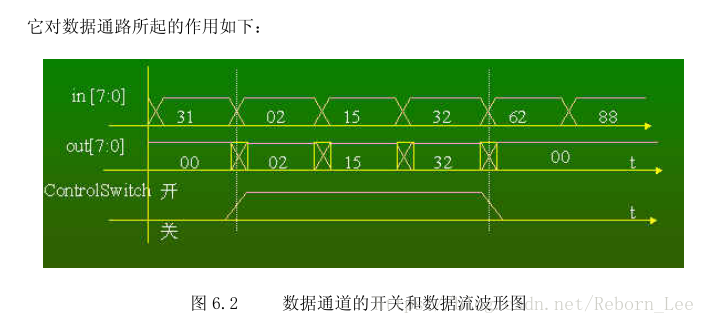

一、一个八位数据通路控制器

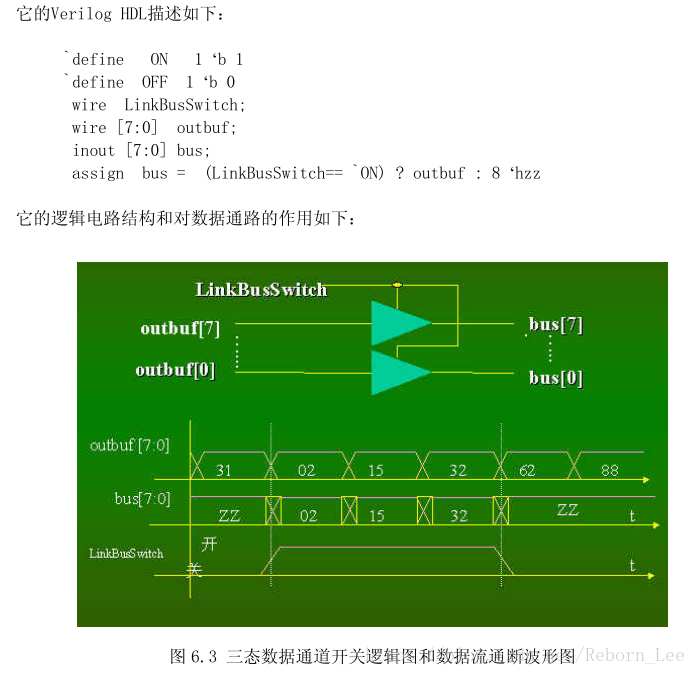

二、一个八位三态数据通路控制器

它与组合逻辑举例之一的差别只在前者在开关断开时输出为零,而后者在开关断开时输出为高阻,即与总线脱离连接。

本文内容来自于:《从算法设计到硬件逻辑的实现》

基础知识,仅供学习交流使用!

下篇精彩博文:数据流动控制学习笔记

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/82316814

- 点赞

- 收藏

- 关注作者

评论(0)