【 FPGA 】FIR 滤波器之多相抽取器(Polyphase Decimator)

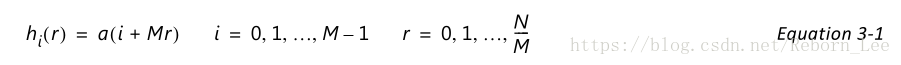

【摘要】 多项抽取滤波器的基本原理:根据等式3-1,将一组N个原型滤波器系数映射到M个多相子滤波器中,映射关系如下:

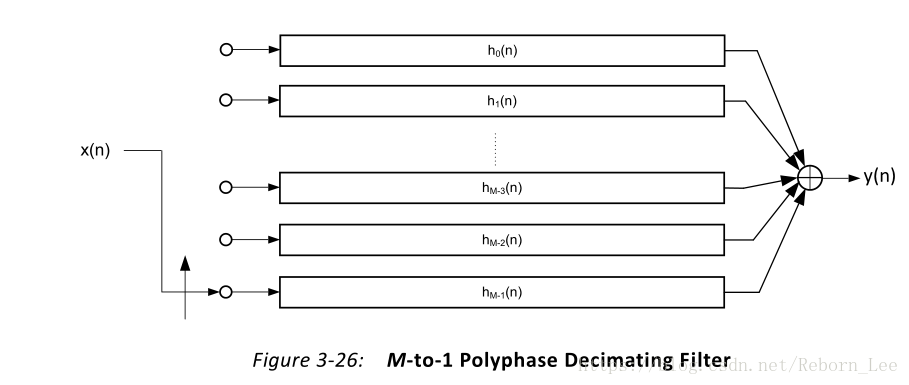

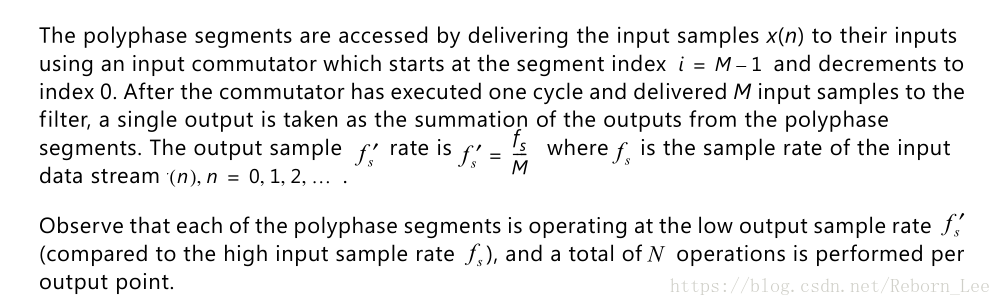

图3-26显示了多相抽取滤波器选项,它实现了计算效率高的M-to-1多相抽取滤波器。

如上图,多相子滤波器从第M个开始逐个以输出采样x(n)作为输入,到第一个输入后完成一轮循环,即将M个采样分别送入M个多相子滤波器后,开始得到输出,输出为...

多项抽取滤波器的基本原理:根据等式3-1,将一组N个原型滤波器系数映射到M个多相子滤波器中,映射关系如下:

图3-26显示了多相抽取滤波器选项,它实现了计算效率高的M-to-1多相抽取滤波器。

如上图,多相子滤波器从第M个开始逐个以输出采样x(n)作为输入,到第一个输入后完成一轮循环,即将M个采样分别送入M个多相子滤波器后,开始得到输出,输出为M个多相子滤波器输出之和,输出采样速率是输入数据流采样速率的1/M。由于输出采样是轮流送入每个多相子滤波器的,因此多相滤波器工作在较低的频率上(相对于较高的输入采样速率),在每个输出点上有N个操作。

下面是英文原文:

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/82909683

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)