【 FPGA 】FIR 滤波器之固定分数率重采样滤波器

FIR滤波器,它以固定的分数比率P/Q实现数据流的重采样,其中P和Q均为整数,最高可达64,可用于Systolic Multiply-Accumulate(SMAC)架构。

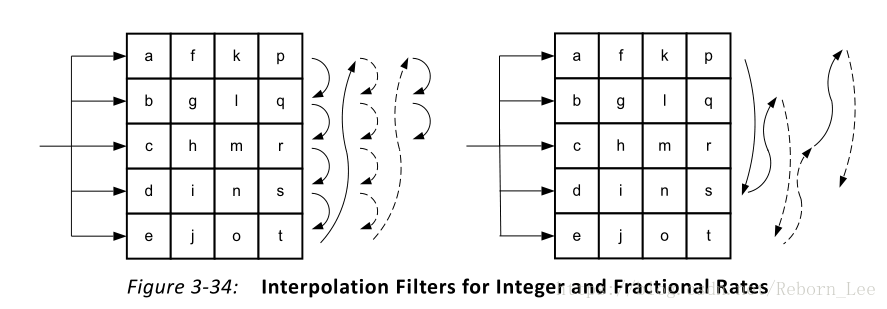

In Figure 3-34, the operation of an interpolation filter with interpolation rate P=5 is contrasted conceptually with the operation of a fixed fractional rate filter with rate P/Q=5/3.

在图3-34中,插值速率P = 5的插值滤波器的操作在概念上与速率P / Q = 5/3的固定分数速率滤波器的操作形成对比。

The normal (integer rate) interpolator passes the input sample to all P phases and then produces an output from each of the phase arms of the polyphase filter structure. In the fractional rate version, the output is taken from a phase arm which varies according to a stepping sequence with step size Q.

正常(整数速率)内插器将输入样本传递到所有P相,然后从多相滤波器结构的每个相臂产生输出。 在分数速率版本中,输出取自相臂,该相臂根据具有步长Q的步进顺序而变化。

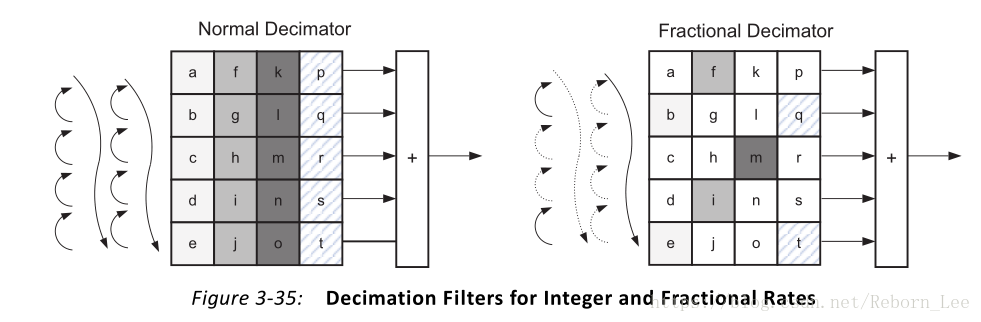

Figure 3-35 shows a similar conceptual method for implementing fractional rate decimators. The integer decimation rate for the left-hand diagram is Q=5, while the fractional-rate shown on the right is P/Q=3/5.

图3-35显示了用于实现分数速率抽取器的类似概念方法。 左侧图的整数抽取率为Q = 5,而右侧所示的分数率为P / Q = 3/5。

The integer rate decimator passes the input samples in sequence to each of the Q phase arms in turn, with the data being shifted through the filter, and the output is generated from the summation of the outputs from each phase arm of the polyphase filter. For the fractional rate implementation, the filter passes the input samples to phases in a stepping sequence based on a step size of P, with zero samples being placed into the skipped phases. The summation across the various phase arms remains the same, but is based on fewer

actual calculations. The implementation details differ somewhat from these conceptual illustrations, but the resulting behavior of the filter is the same. Symmetry is not currently exploited when using the fractional rate structures.

整数速率抽取器依次将输入样本传递给每个Q相臂,数据通过滤波器移位,并且输出由多相滤波器的每个相臂的输出求和产生。 对于分数速率实现,滤波器基于步长P将输入样本传递到步进序列中的相位,其中零样本被置于跳过的相位中。 不同相臂的总和保持不变,但是基于较少的实际计算。 实现细节与这些概念图略有不同,但过滤器的结果行为是相同的。 使用分数率结构时,目前尚未使用对称性。

暂时先这样记,理解深刻了在修改。国庆了,我也要回家了,最近写不了博文,加紧时间把FIR滤波器的这部分内容搞搞,先记下来,再慢慢理解。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/82913990

- 点赞

- 收藏

- 关注作者

评论(0)