【 FPGA 】FIR滤波器的采样速率与系统时钟速率不同时的资源消耗分析

目录

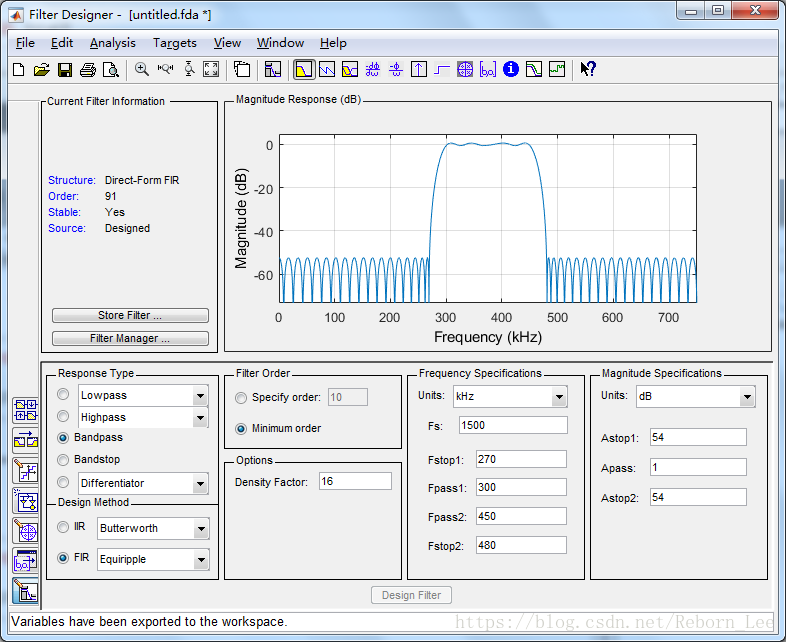

MATLAB操作

在matlab中命令窗口中输入:filterDesigner,设计如下参数的带通滤波器;

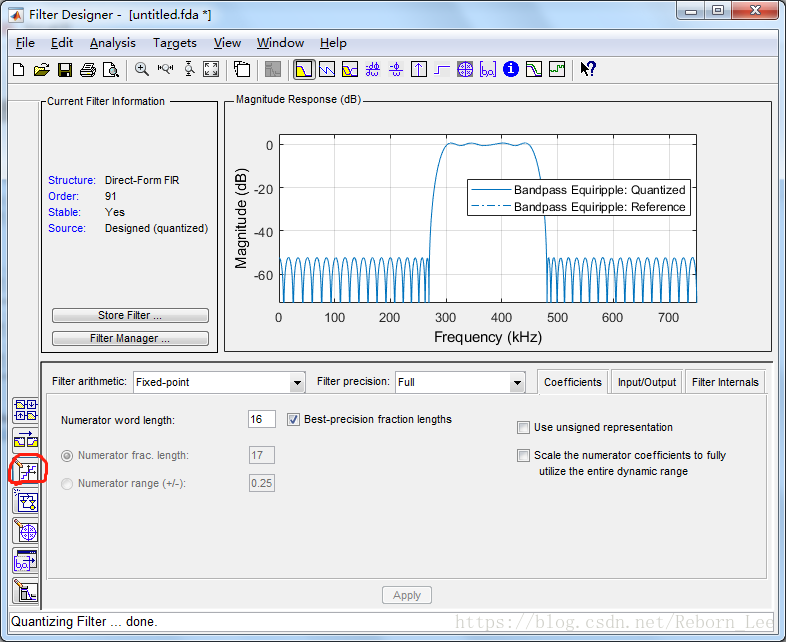

在左侧第三个功能设置:Set quantization parameters,选择Filter arithmetic为Fixed-point,由于只是测试,参数保持默认即可。

在菜单栏中选择targets,展开选择生成Xilinx的coe文件:(自己选择路径,命名)

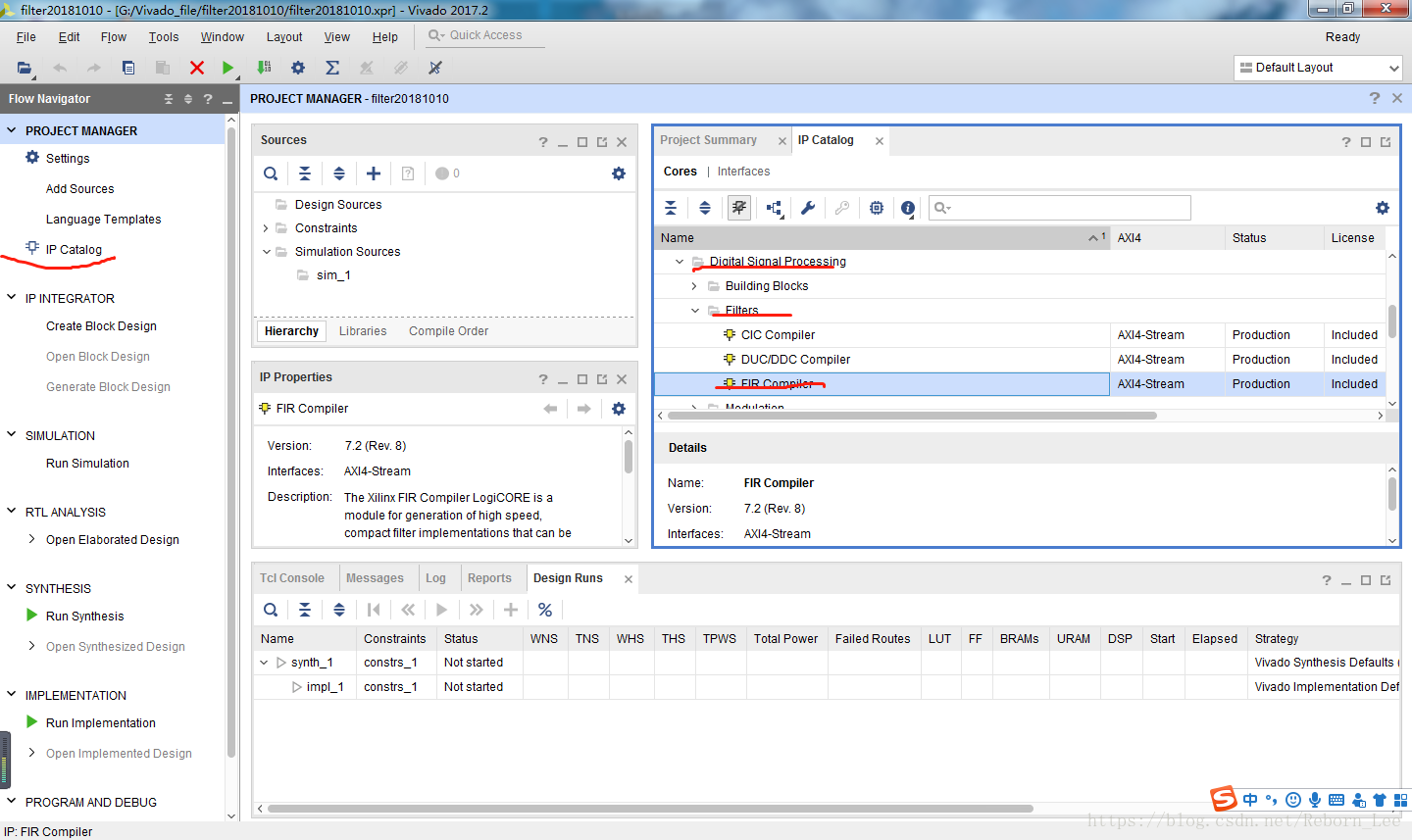

Vivado操作

需要设计的FIR的系数文件搞定了,下面进入Vivado进行IP核设计:

简单的创建一个Vivado工程,这些都无关紧要,随便创建一个工程,然后按照下图的方式创建一个IP核:

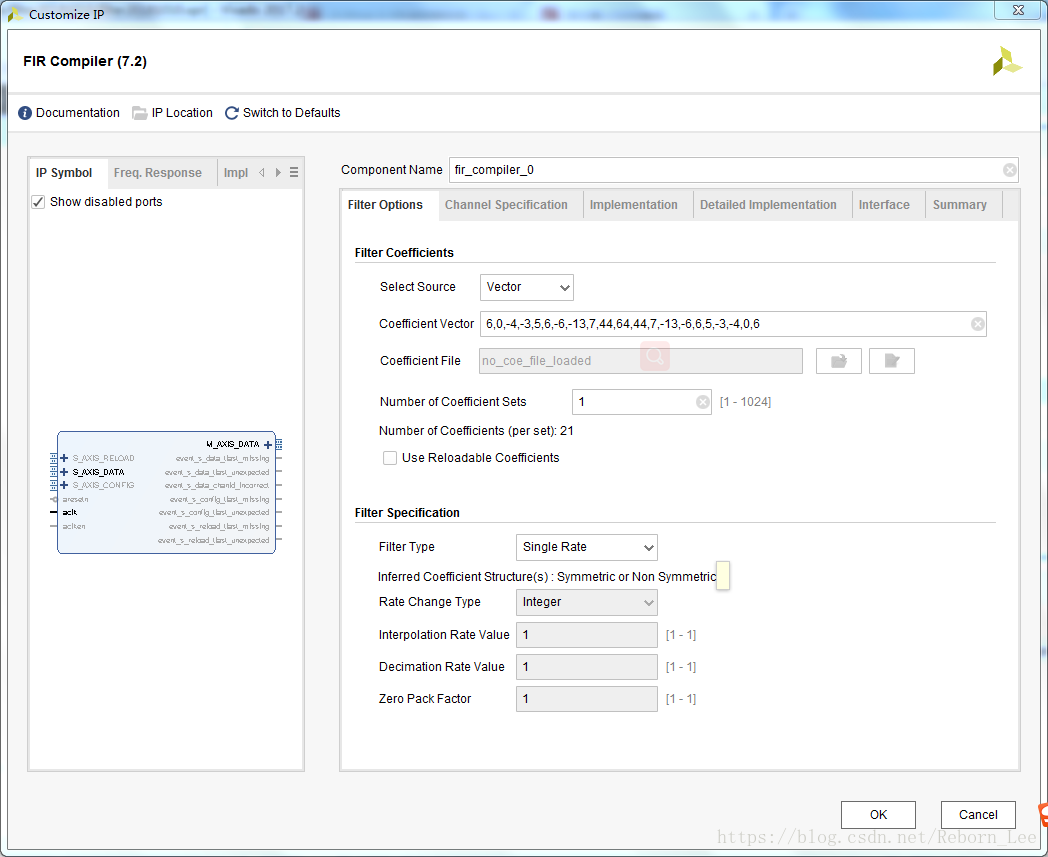

双击FIR compiler,进入初始页面如下:

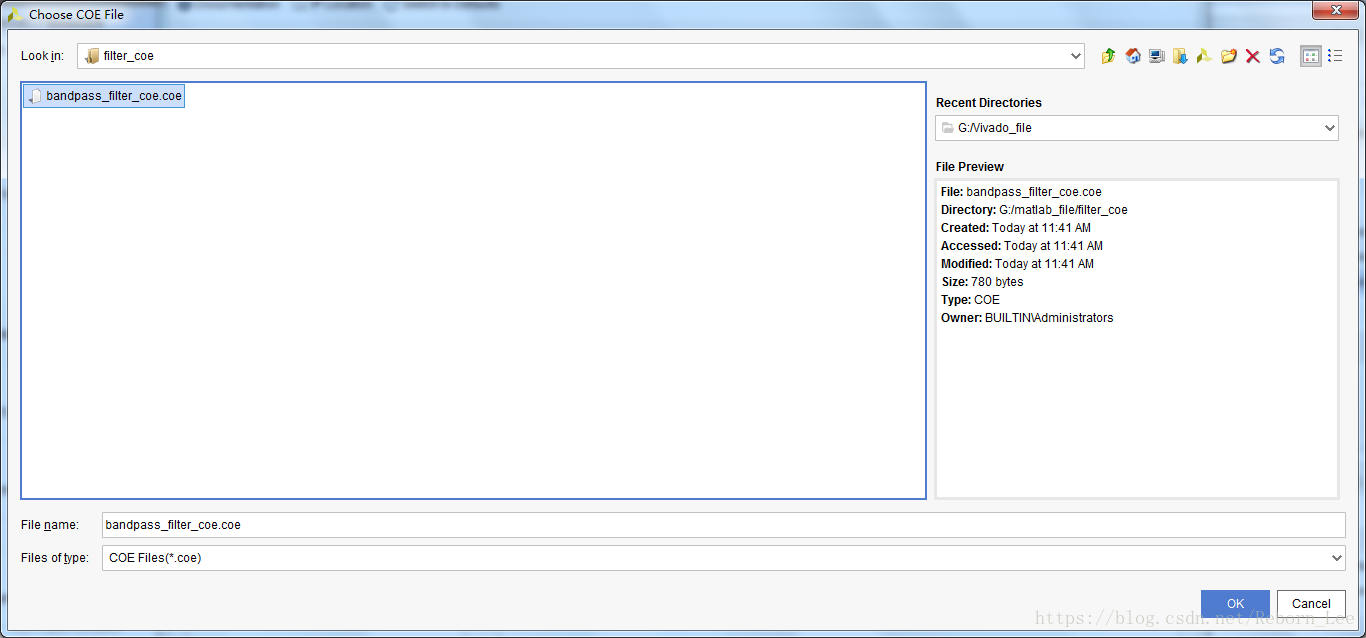

在滤波器系数(Filter Coefficients)下面选择(select sources)为COE File,然后添加你的coe文件,也就是上面用matlab生成的系数文件,加载进去:

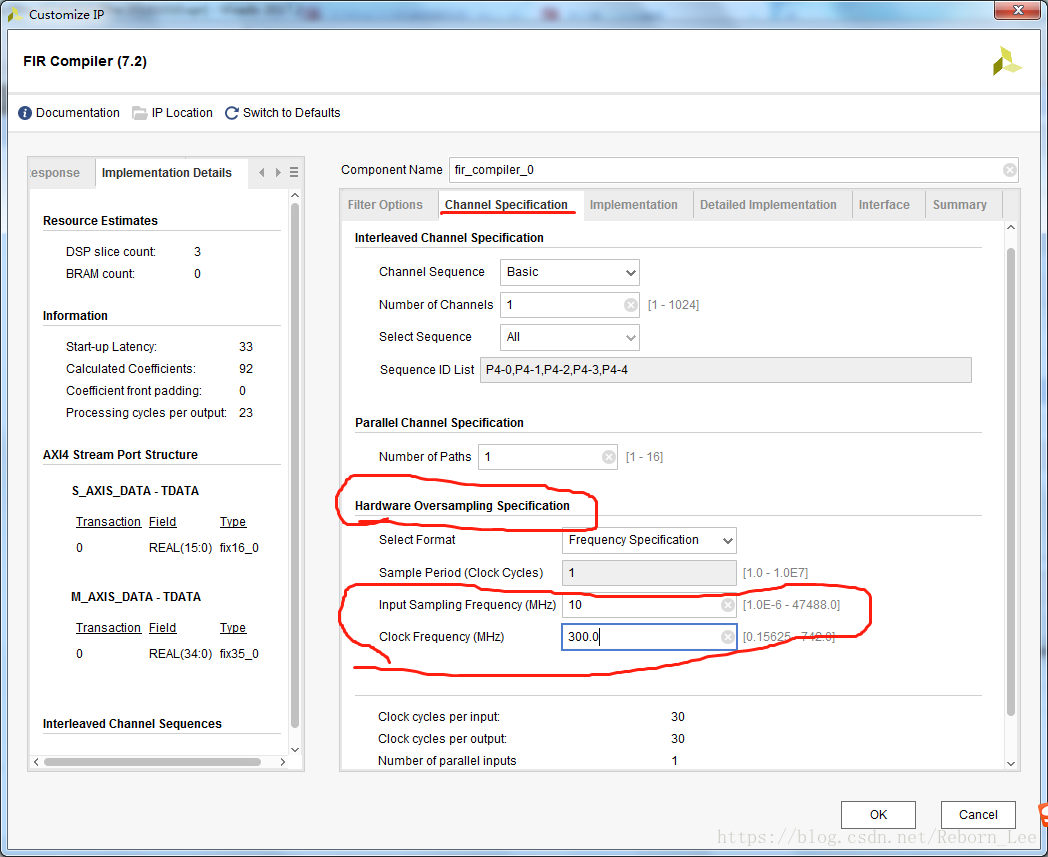

之后,其他基本不需要改,当然到具体的设计中,可以根据需求自己改,这里改下采样速率以及时钟频率等:

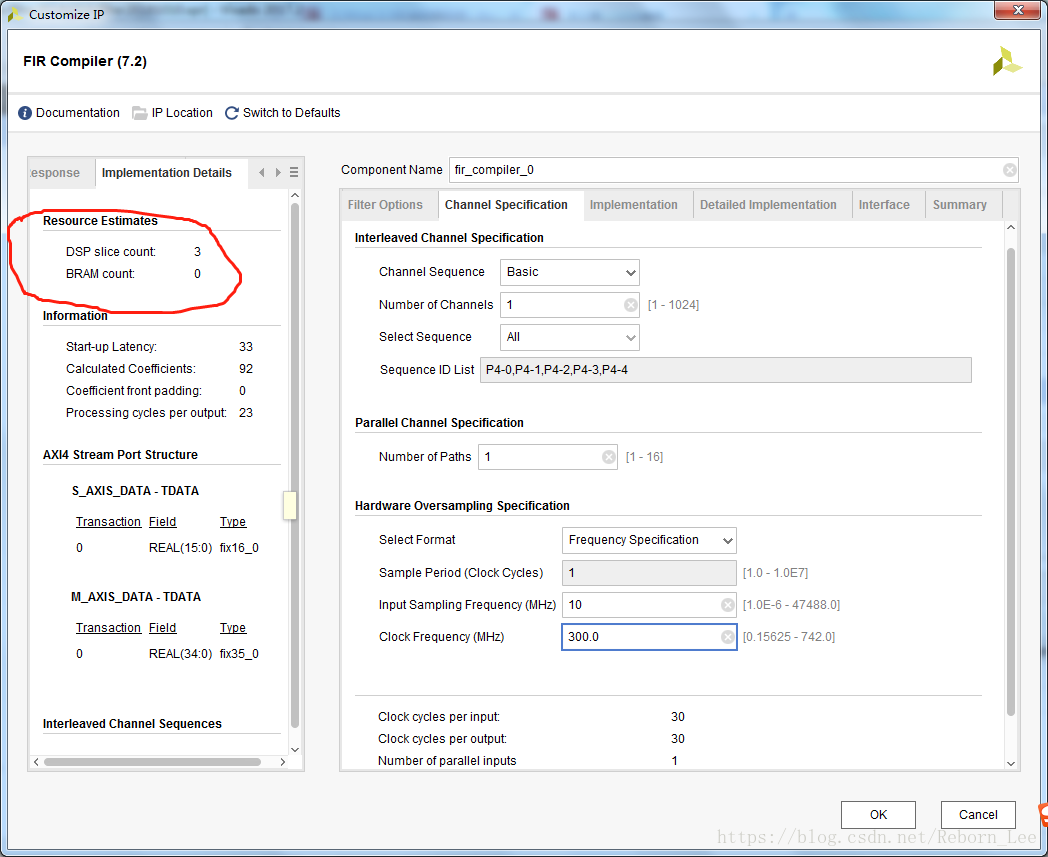

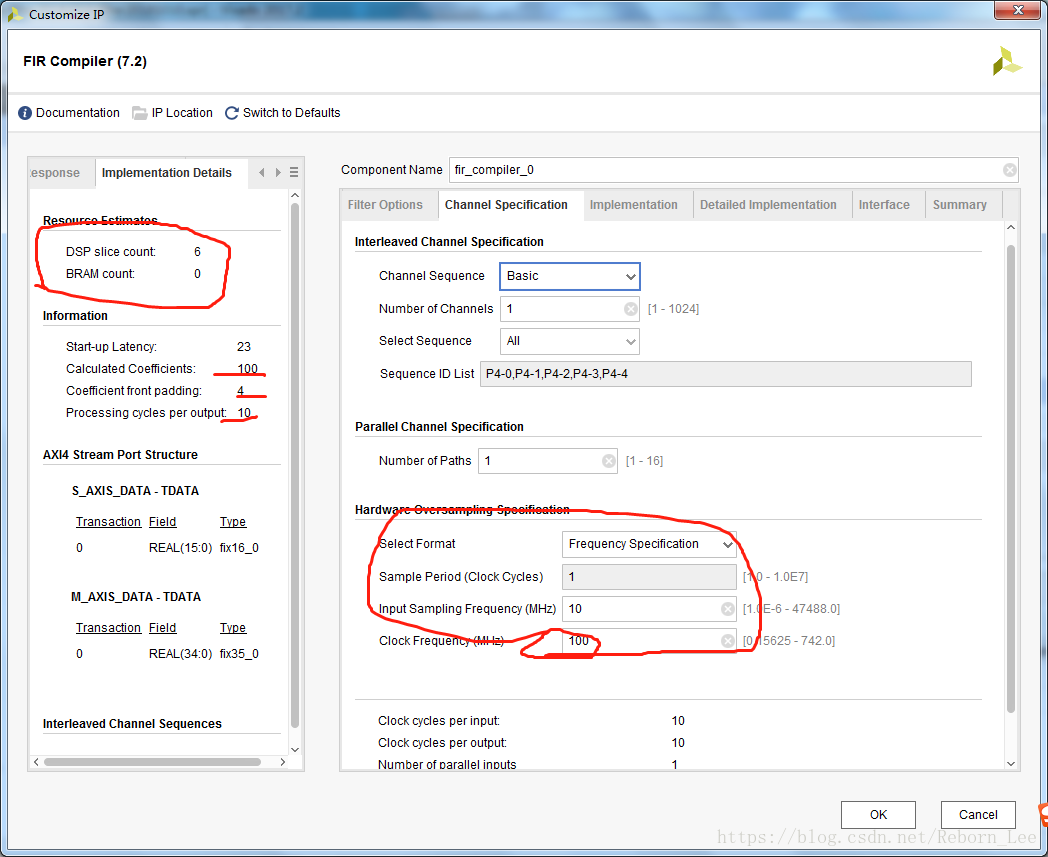

然后我们看下消耗的资源情况:(输入时钟为10MHz,时钟周期为300MHz的情况)

改变下时钟速率为100MHz,采样速率不变的情况:

可见,消耗的资源:dsp slice竟然多了!

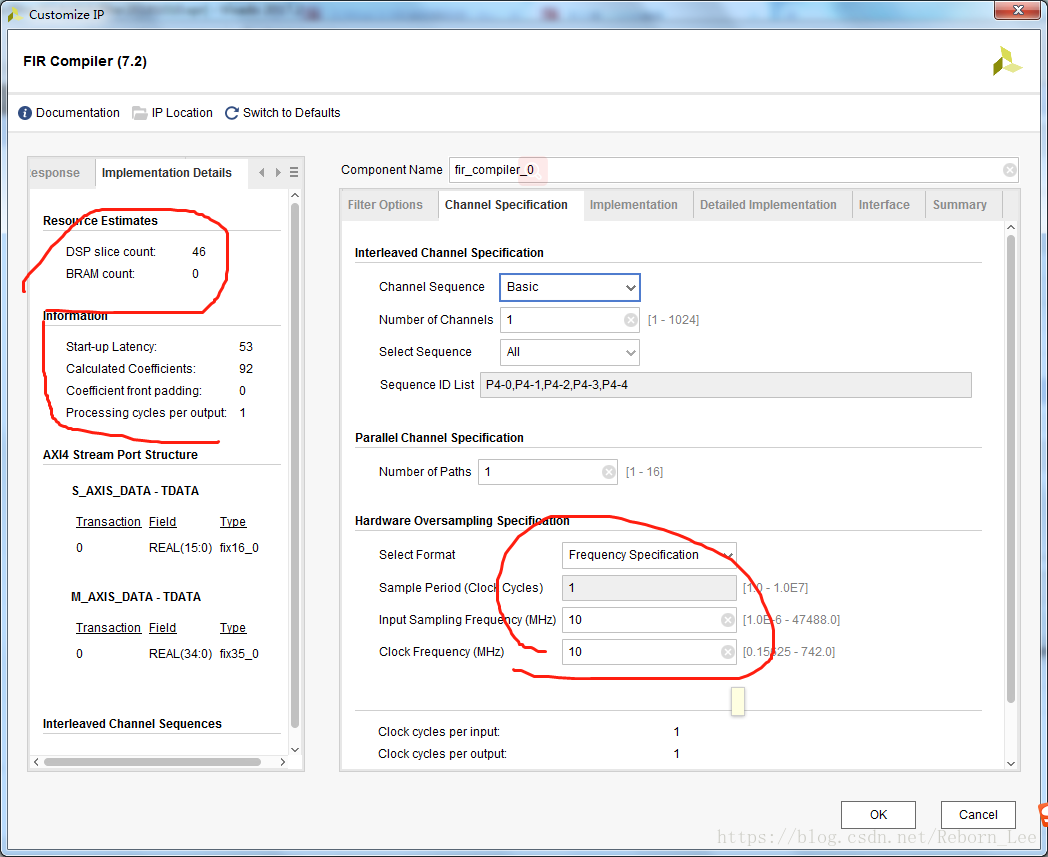

再试:这次改为采样速率不变,时钟速率为10MHz,和采样速率一致,结果如下:

可见,消耗的资源更多了。

这里我们可以得出初步的结论了,那就是如果系统时钟速率降低,那么消耗的资源就越多,反之,时钟速率增高,那么消耗的资源就越少。

我们在这里在提出一个问题,为什么消耗的资源是DSP slice资源?

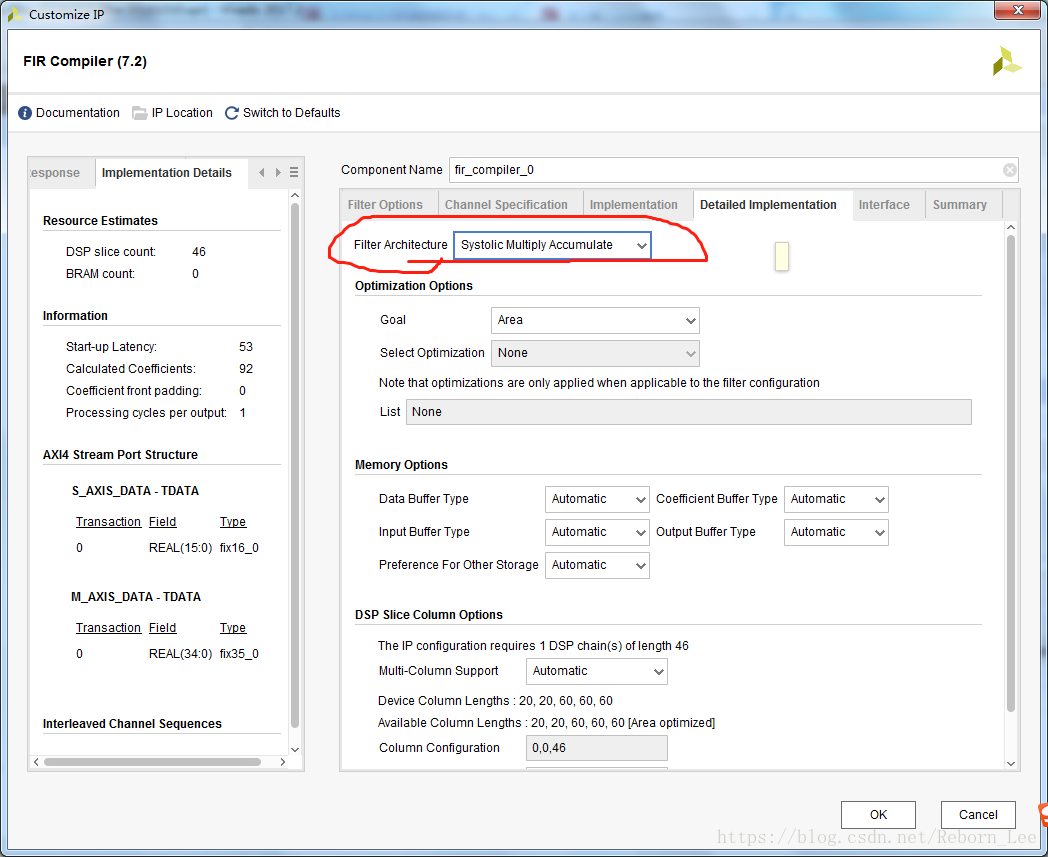

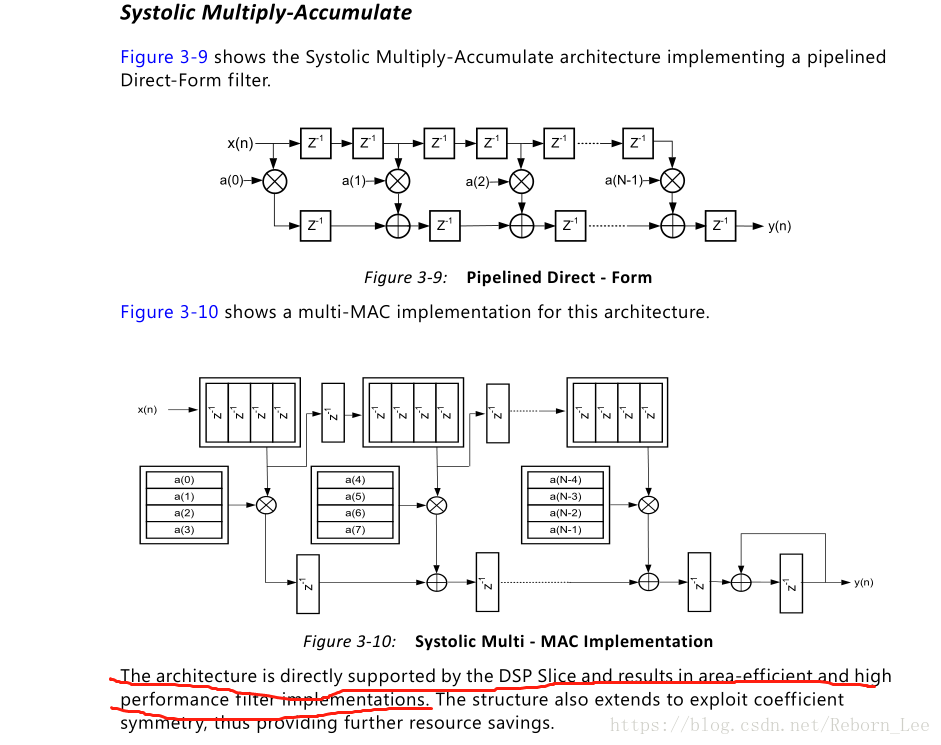

由于使用的SMAC架构:

查询数据手册有如下这句话:

该体系结构直接由DSP片支持,从而实现了区域高效和高性能的过滤器实现。该结构还扩展到利用系数对称,从而进一步节省资源。

原文如下:

也可以见我的博文:【 FPGA 】FIR 滤波器的架构

暂时记录到这里,下篇博文分析下SMAC结构到底是怎么工作的?

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/82994642

- 点赞

- 收藏

- 关注作者

评论(0)