【 FPGA 】抢占式优先级译码器电路

【摘要】 今天看用选择器实现总线设计的程序中(【 FPGA 】总线实现形式之选择器),选择器控制信号部分用到了抢占式优先级译码器,这里单独把这个抢先式优先级译码器抽出来讲讲看:

高位优先,下面是Verilog HDL代码:

`timescale 1ns / 1ps//// Company: // Engineer: // // Create Date: 11:49:31 11/05...

今天看用选择器实现总线设计的程序中(【 FPGA 】总线实现形式之选择器),选择器控制信号部分用到了抢占式优先级译码器,这里单独把这个抢先式优先级译码器抽出来讲讲看:

高位优先,下面是Verilog HDL代码:

-

`timescale 1ns / 1ps

-

//

-

// Company:

-

// Engineer:

-

//

-

// Create Date: 11:49:31 11/05/2018

-

// Design Name:

-

// Module Name: decoder

-

// Project Name:

-

// Target Devices:

-

// Tool versions:

-

// Description:

-

//

-

// Dependencies:

-

//

-

// Revision:

-

// Revision 0.01 - File Created

-

// Additional Comments:

-

//

-

//

-

module decoder(

-

input in0,

-

input in1,

-

input in2,

-

input in3,

-

output [1:0] out

-

);

-

reg [1:0] out;

-

always@(in0,in1,in2,in3)

-

begin

-

-

case({in0,in1,in2,in3})

-

4'b0001: out = 2'b11;

-

4'b0010 - 4'b0011: out = 2'b10;

-

4'b0100 - 4'b0111: out = 2'b01;

-

default: out = 2'b00;

-

endcase

-

-

end

-

-

endmodule

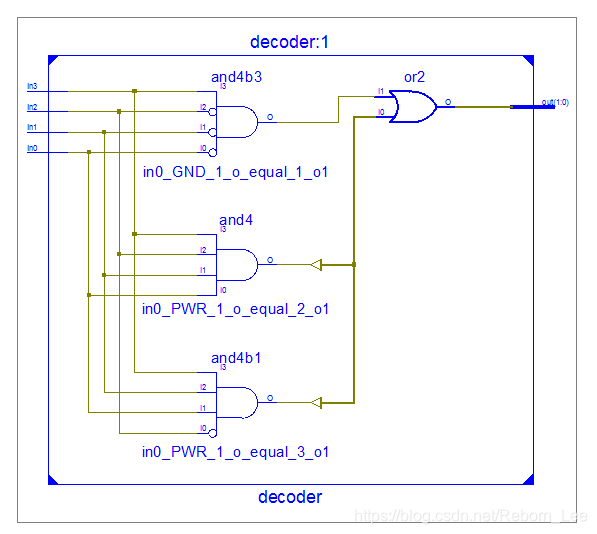

综合出来的电路,首先是RTL原理图:

不奇怪,我也能猜到是这些逻辑门实现的。

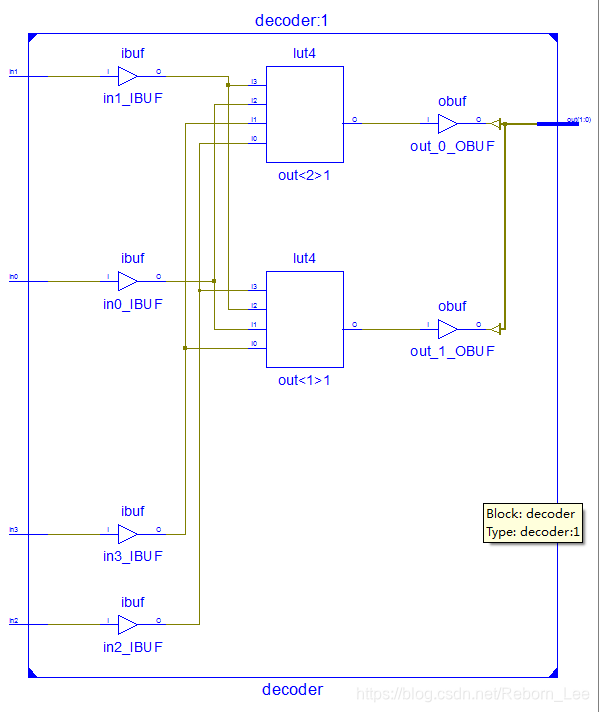

下面看看它们在FPGA中是如何实现的,看看Technology Schematic:

和我想的不一样的是,它是用查找表实现的,当然这是合理的,但是我一开始想的是FPGA中有大量的MUX,也就是多路选择器,应该会用MUX实现,但又一想,FPGA中也有大量的LUT呀, 人家综合成LUT再正常不过了。

这个小电路不过多解读,这种译码器是有优先级的,至于为什么,看看代码就知道了。

你希望那个输入优先,放到高位就可以了,(in0,in1,in2,in3等)随你排列。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/83750618

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)