【 FPGA 】组合逻辑中的竞争与险象问题(四)

上篇博文:组合逻辑中的竞争与险象问题(三)讲解了险象的定义,即竞争引起的非预期输出,同时给出了分析,对什么样的竞争会引起险象。

这篇博文继续讲解险象问题,重要突出险象的分类。

上篇博文最后提出了化简后具有多个半开关的电路,可能会导致险象的阻塞,缩小,传递或方法作用。这篇博文接着这个问题讨论:

(1)一般说来,如果若干个与半开关被一个或半开关级联,或者若干个或半开关被一个与半开关级联,主要会对险象起放大作用;

(2)如果若干个与半开关被一个与半开关级联,或者若干个或半开关被一个或半开关级联,主要会对险象起到截止、缩小作用;

(3)如果若干个与半开关、或半开关被无论是一个与半开关还是或半开关级联,主要会对险象起到传递、缩小的作用。

下面研究险象的一些具体表现形式,概括起来,险象可以分为静态险象和动态险象,下面分别介绍:

静态险象

静态险象,指的是由于竞争,导致的原本输出不应该发生变化的组合逻辑,出现了输出变化现象。从静态险象的定义,我们可以推出,如果一个组合逻辑,在某一种输入条件下存在静态险象,那么其逻辑表达式在该条件下一定可以简化为F = 1或F = 0。

按其所应保持的电平,又可以将这类险象细分为0险象和1险象。

(1)0 险象

0险象指的是组合逻辑的初识输出为0,当其输入改变时,若新输入对应的输出仍应该是0,却在输出端出现了短暂的不为0的情况。(这种情况很常见,上篇博文中,一个两输入的与门半开关就是如此,当输入从1变为0时,就会出现短暂的1逻辑,这种险象就是0 险象。)

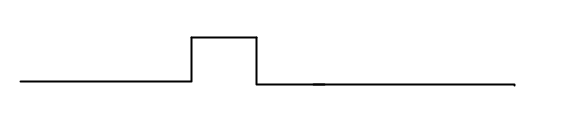

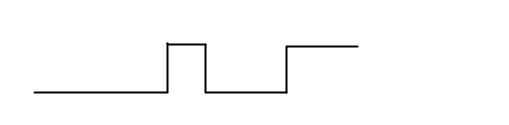

下图为典型的0险象的波形:

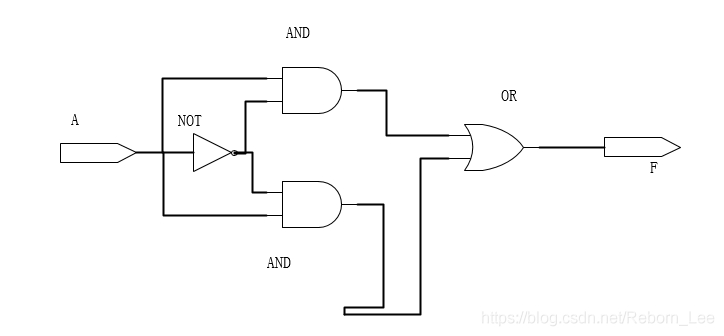

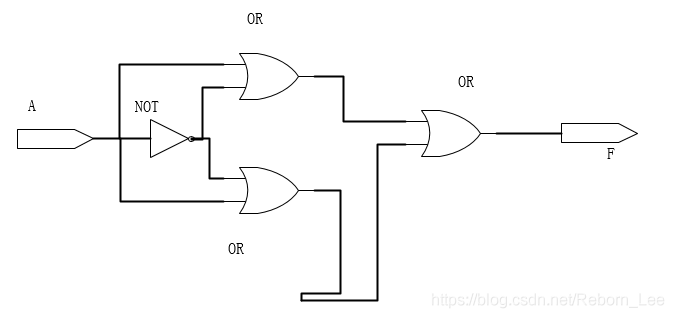

当出现半开关级联的情况,0险象中1的脉冲个数可能不只一个,例如,若简化后的电路如下图,则叠加后的0险象可能会出现两个1脉冲,当然也可能是一个更宽的1脉冲。

上图是两个与门半开关和一个或门半开关级联的情况,如开头所说,这种级联会导致险象的放大。

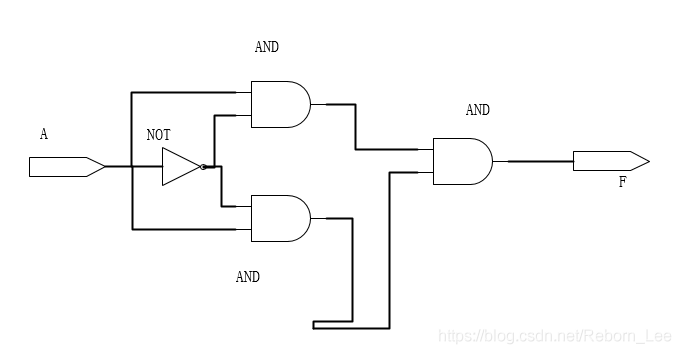

下图是两个与门半开关和一个与门半开关级联的情况,如开头所说,这种级联会缩小险象,如下:

上图的这种级联会消减1脉冲的宽度,甚至会完全阻止1脉冲。

(2)1 险象

1险象是指组合逻辑的输出初始值为1,当其输入改变时,若新输入对应的输出仍应该是1,却出现了短暂不为1的情况。

这种情况和0险象的情况完全对偶,我们可以给出如下两个级联的例子:

上图这种,两个或半开关和一个与门半开关的级联,会使0脉冲变大,或者出现两个0脉冲。

而下图这种级联会使0脉冲缩小,或完全阻塞。

动态险象

动态险象,指的是由于竞争,导致原本输出只应该发生一次变化的组合逻辑,出现了输出多次变化的现象。

如果一个组合逻辑在某一种输入条件下存在动态险象,那么其逻辑表达式在该条件下一定可以化简为 F = A 或 F =  。经过前面的分析,我们得知只有当半开关的M个输入中有0也有1时,竞争才可能导致险象。因此,对于单个半开关来说,它的表达式只能化简为F = 1(或类型半开关)或F = 0(与类型半开关),因此动态险象发生的前提是电路中一定存在半开关的级联,且前级的半开关先导致静态险象。

。经过前面的分析,我们得知只有当半开关的M个输入中有0也有1时,竞争才可能导致险象。因此,对于单个半开关来说,它的表达式只能化简为F = 1(或类型半开关)或F = 0(与类型半开关),因此动态险象发生的前提是电路中一定存在半开关的级联,且前级的半开关先导致静态险象。

按其初始和稳定时所对应的逻辑电平,又可将这类险象细分为01险象和10险象。

(1)01 险象

01 险象,是指组合逻辑初始输出为0,当其输入改变时,对应新的输出应该为1,本来输出只应该出现一次从0到1的翻转,但实际中却出现了多次的0,1翻转情况。

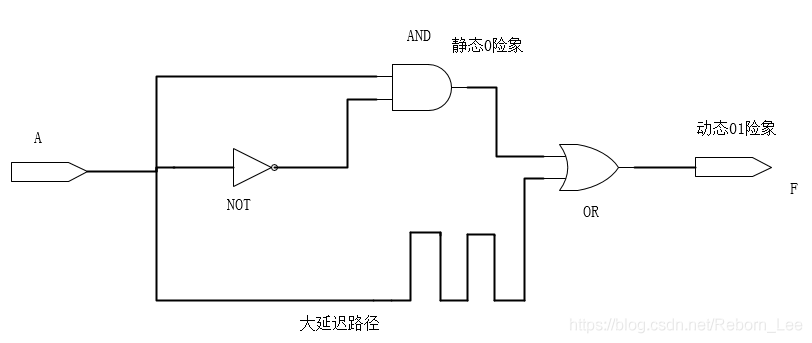

典型的 01 险象如下图:

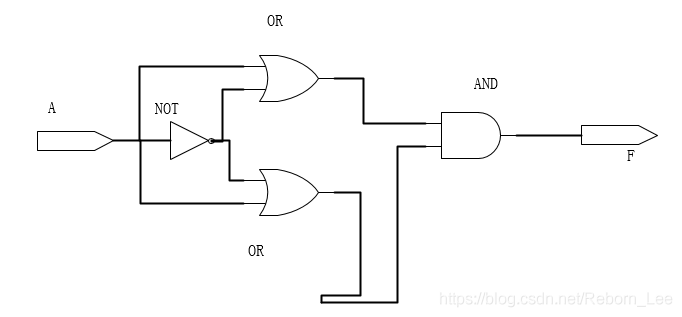

例如,若简化后的电路图如下图,就会出现上述典型的01险象:

上述电路中,当输入端A从0变化到1时,由于下半部分路径延迟比较大,导致或类型半开关先传递了上半部分的静态0险象后输出恒为1,因此形成了动态01险象。如果简化电路再复杂一些,则01险象的翻转次数也可能会更加多一些,例如若本例或类型半开关上半部分输入的是一个叠加后成双1脉冲的0险象,那么输出就可能翻转3次。

(2)10 险象

上面的讨论分析了01险象,有了01险象,那么10险象就很容易了。

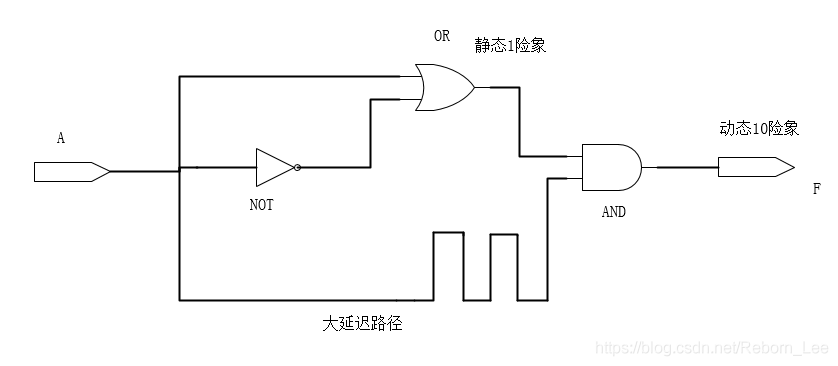

如下电路:

当输入端从1变化到0时候,由于下半部分延迟较大,所以与类型半开关先传递了上半部分的静态1险象后,再传递下半部分,输出恒为0,形成了10险象。

这篇博文暂时到这里,下篇博文讲解险象对数字电路的影响以及如何对待险象。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/84500867

- 点赞

- 收藏

- 关注作者

评论(0)