【 FPGA 】状态机的模型之Moore型状态机

上篇博文:状态机,FPGA的灵魂,说到了状态机的基础知识,讲到了状态机的组成六要素,工作四要素。

这篇博文来讲状态机的模型之Moore状态机,从标题也能看出,状态机的知识并没有结束,后面还会提到Mealy型状态机。

Moore型状态机

根据状态机的输出与其现态、输入之间的关系,可将FPGA中的状态机抽象为三种基本模型——Moore、Mealy和Mix,即摩尔型,米利型和混合型。

如果一个状态机的输出仅由现态决定,那么它就是一个Moore型的状态机。按照驱动输出的数字电路特征,又将Moore型状态机细分为Moore 1 型,Moore 2 型和Moore 3型。详细介绍如下:

(1)Moore 1型

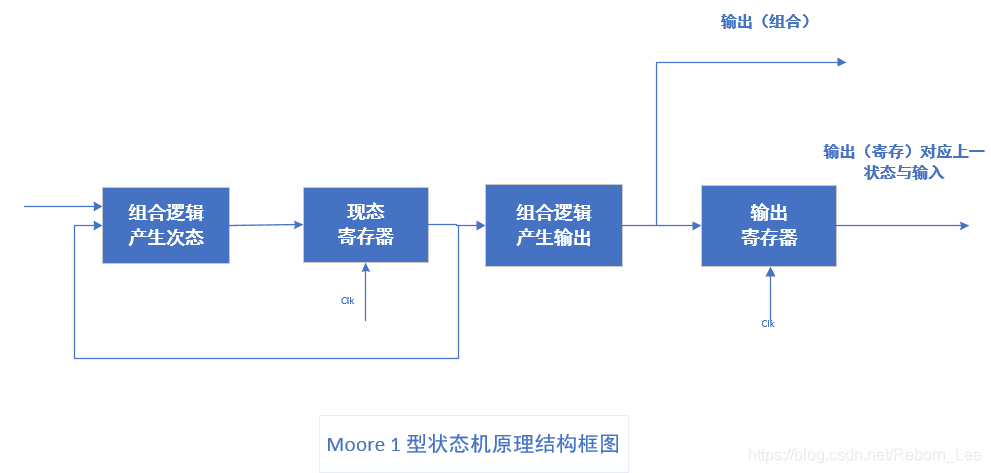

如下图1为Moore 1型的原理结构框图:

从上图可以看出,Moore 1型状态机的结构可以划分为两大部分,状态转移部分和输出生成部分。

上图的左半部分为状态转移部分,输入和现态(现态寄存器的输出)通过组合逻辑,共同作用产生了次态,当下一次时钟有效边沿到来的时候,现态寄存器发生更新,刚才产生的次态即成为了新的现态,而新的现态和新的输入共同作用产生新的次态,如此往复。

输出生成部分如上图右半部分所示,现态(现态寄存器的输出)直接通过组合逻辑产生当前的输出(这点也是Moore状态机和Mealy状态最显著的区别。)有时候,我们不希望将这部分组合逻辑的延迟影响到后续模块的处理,那么可以仿照上图通过添加输出寄存器来解决这个问题,但是需要特别注意的一点是,由于输出寄存器的更新需要等到下一次时钟的有效边沿,因此,经过输出寄存器寄存后的输出其实对应的是上一个状态。

(2)Moore 2 型

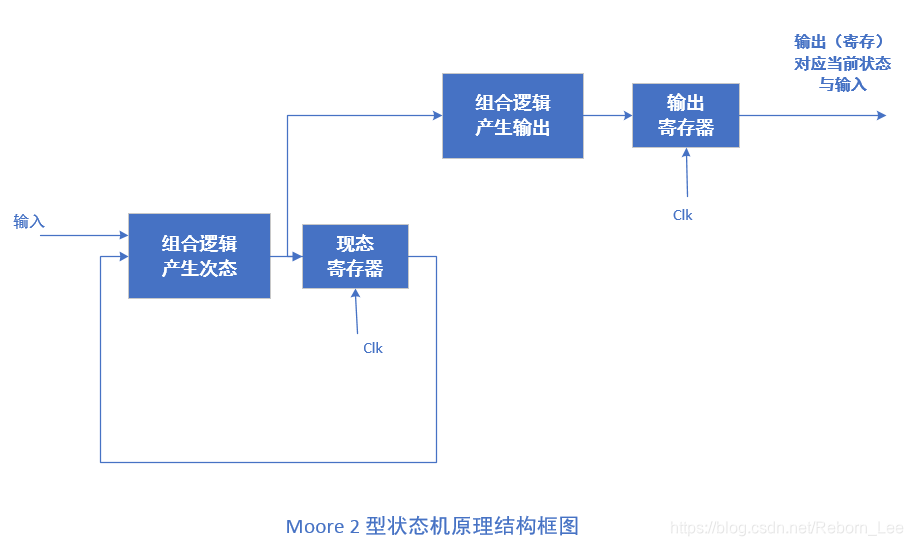

Moore 1 型状态机的缺点是寄存后的输出并不对应于此时的现态,这可能为后续模块的一些处理带来不便和延迟;除此之外,如果不通过输出寄存器输出,组合逻辑中存在着竞争,使得输出即使仅为1bit位宽,有可能会发生险象,如果后续模块是对电平敏感的,便会导致错误发生,因此通过对Moore 1型状态机的原理结构框图进行一些简单地修改,可得Moore 2型状态机的原理结构框图,如下图2:

同样,Moore 2型状态机的结构也可以分为两部分, 一部分是状态状态部分,位于上图的左边,另一部分是输出生成部分,位于上图的右边。

对比Moore 1型状态机,可以发现不同点仅仅为输出生成部分的输入端由之前的现态(现态寄存器的输出)变为了次态(有现态和输入通过组合逻辑产生)。

这样一来,由于次态和次态决定的输出在同一个时钟周期内变得有效,那么在下一次时钟有效沿到来时,现态寄存器和输出寄存器将会同时进行更新,至此,次态变为新的现态,次态决定的输出变成新的输出。因此,Moore 2 型状态机中经过寄存后的输出是对应于当前状态的。

(3)Moore 3型

相比于Moore 1型,Moore 2型状态机也有其自身的缺点,那就是产生输出的组合逻辑延迟较大,因为它相当于Moore 1型状态机中产生次态的组合逻辑和产生输出的组合逻辑的级联,而这点便会限制状态机本身的时钟工作频率。由此,可见Moore 1型和Moore 2型状态机各有优缺点。

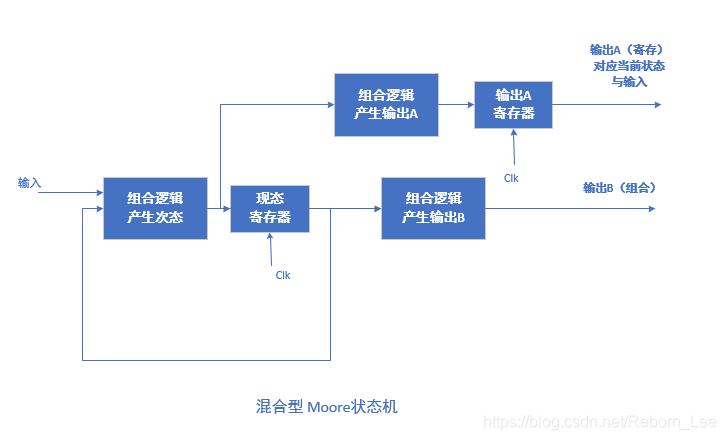

仔细观察Moore1和Moore2 型状态机的原理结构框图,可以发现,它们的本质区别就是“由状态产生输出”这部分的组合逻辑所处的位置。如果像Moore 1型那样,将该部分逻辑至于现态寄存器之后,那么该组合逻辑的时间延迟会影响到后续电路的工作;反之,如果像Moore2型那样,将该部分逻辑置于次态产生逻辑之后,那么该组合逻辑的时间延迟会影响到状态机自身的工作。因此,将Moore 1和Moore 2型状态机的缺点最小化,优点最大化,便有了Moore3型状态机,它的原理结构框图如下:

现实中,状态机的输出往往不止一个,通过上图可以看出,Moore3型状态机就是将那些适合使用组合逻辑的输出采用Moore1型的方式来处理,而将那些适合使用寄存器的输出采用Moore2型的方式来处理,因此Moore3型状态机也叫混合型Moore状态机。

那到底什么样的输出适合采用组合的形式,而什么样的输出适合采用寄存的形式呢?如果后续模块为电平敏感的,那么自然应该选择寄存形式的输出,不过FPGA中一般应该为全同步逻辑设计,所以绝大多数情况下,状态机的前级输入、后级输出及其本身是工作在一个时钟域内的,此时,假设由现态,输入产生次态的组合逻辑时间延迟为T1,有状态产生输出的组合逻辑的时间延迟为T2,而后续使用该输出的电路中,又会在输出信号到达下一个寄存器前引入时间延迟最大为T3的组合逻辑。

那么根据短板效应,如果T1 + T2 <= T2 + T3,则该输出采用Moore2型的寄存方式处理可能提升整个系统的性能;反之,该输出采用Moore1型的组合方式处理可以提升整个系统的性能。

当然了,上述方法仅仅是从理论上去理解如何进行输出形式选择,其实并不可能严格地参考使用,因为布局布线的不同对T1、T2和T3的取值影响很大,因此实际中都是凭经验或者大概估计一下各个组合逻辑的复杂度和级联情况,然后大概估算后作出选择,而更多的时候,是需要根据后续时序分析报告中的结果,来对状态机的输出形式进行调整。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/84634128

- 点赞

- 收藏

- 关注作者

评论(0)