【 FPGA 】关于FPGA中复位的设计问题(包含异步复位,同步释放方案)

目录

复位的目的

复位的基本目的是使器件进入到可以稳定工作的确定状态,这避免了器件在上电后进入到随机状态导致跑飞了。在实际设计过程中,设计者必须选择最适合于设计本身的复位方式。

耳熟能详的是同步复位和异步复位,分别介绍如下:

同步复位

同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。同步复位的Verilog HDL描述为:

-

module syn_reset(

-

input rst_n,

-

input clk,

-

input data_in,

-

output out

-

);

-

-

reg out;

-

always@(posedge clk)

-

begin

-

if(!rst_n)

-

out <= 1'b0;

-

else

-

out <= data_in;

-

end

-

-

-

endmodule

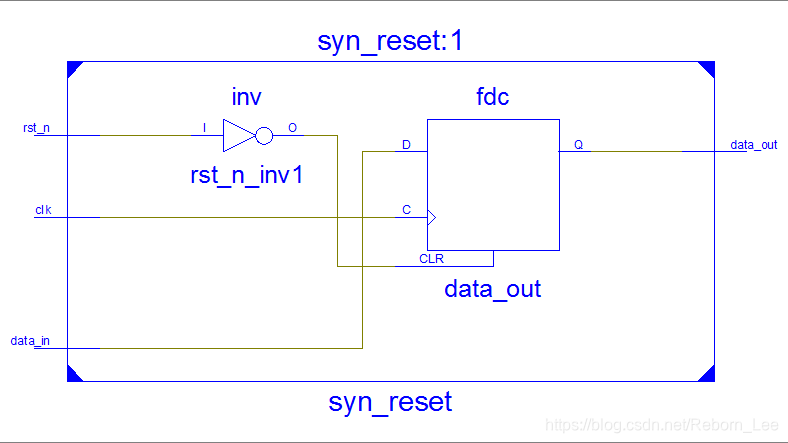

综合后的RTL图为:

复位有效的时候,要等到时钟有效沿输出才复位为0,否则正常运行。

图中,MUX可以换成与门。

异步复位

异步复位是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。异步复位的Verilog HDL描述为:

-

module test

-

(

-

input clk,

-

input rst_n,

-

input data_in,

-

output out

-

);

-

reg out;

-

always @ (posedge clk or negedge rst_n)

-

if(!rst_n) out <= 1'b0;

-

else out <= data_in;

-

endmodule

综合后的RTL图为:

既然同步复位使用了Quartus进行了综合,这里也试下,觉得Altera这个公司的工具还真不错,综合出来的电路很简洁。

优缺点比较

同步复位的优点:

- 一般能够确保电路是百分之百同步的。

- 确保复位只发生在有效时钟沿,可以作为过滤掉毛刺的手段。

同步复位的缺点:

- 复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位。同时还要考虑如:时钟偏移、组合逻辑路径延时、复位延时等因素。

- 由于大多数的厂商目标库内的触发器都只有异步复位端口,采用同步复位的话,就会耗费较多的逻辑资源。

异步复位优点:

- 异步复位信号识别方便,而且可以很方便的使用全局复位。

- 由于大多数的厂商目标库内的触发器都有异步复位端口,可以节约逻辑资源。

异步复位缺点:

- 复位信号容易受到毛刺的影响。

-

复位结束时刻恰在亚稳态窗口内时,无法决定现在的复位状态是1还是0,会导致亚稳态。(复位撤离时间不满足复位恢复时间会导致亚稳态。)

异步复位,同步释放(撤离)

-

module Reset_test(

-

input clk,

-

input rst_nin,

-

output reg rst_nout

-

);

-

-

reg rst_mid;

-

-

always@(posedge clk or negedge rst_nin)

-

begin

-

if(!rst_nin)

-

begin

-

rst_mid <= 0;

-

rst_nout <= 0;

-

end

-

else

-

begin

-

rst_mid <= 1;

-

rst_nout <= rst_mid;

-

end

-

end

-

endmodule

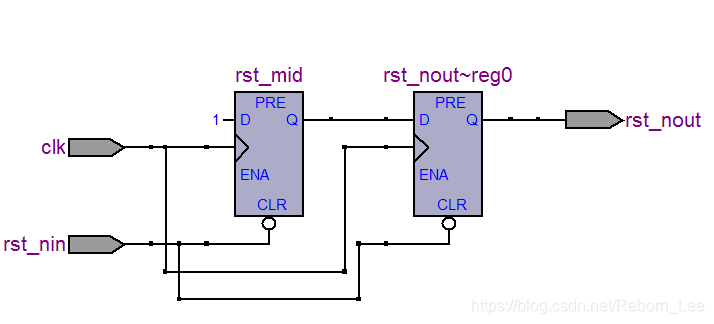

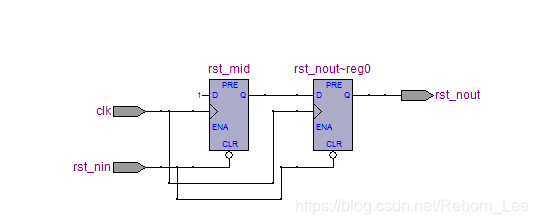

异步复位、同步释放机制,既解决了同步复位浪费资源问题,又解决了异步复位带来的亚稳态。

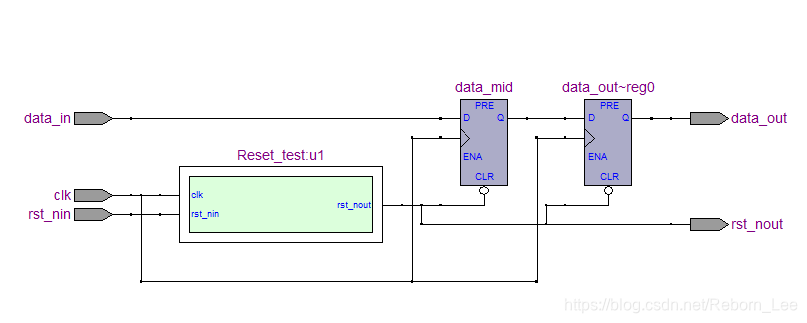

下面调用上面的异步复位,同步释放处理后的复位信号,并给出RTL电路图:

-

`timescale 1ns / 1ps

-

-

module test_main(

-

input rst_nin,

-

input clk,

-

input data_in,

-

output rst_nout,

-

output reg data_out

-

);

-

-

reg data_mid;

-

-

Reset_test u1(.clk(clk),.rst_nin(rst_nin),.rst_nout(rst_nout));

-

-

always@(posedge clk or negedge rst_nout)

-

begin

-

if(!rst_nout)

-

data_mid <= 1'b0;

-

else

-

data_mid <= data_in;

-

end

-

always @ (posedge clk or negedge rst_nout)

-

if(!rst_nout)

-

data_out <= 1'b0;

-

else

-

data_out <= data_mid;

-

-

-

-

endmodule

RTL电路图如下,其中的复位处理模块一并给出:

关于异步复位,同步释放的分析,放到下一篇博客分析。

参考文献:

FPGA深度解析

https://zhuanlan.zhihu.com/p/32071206

https://www.cnblogs.com/yfwblog/p/4793118.html

http://www.cnblogs.com/qiweiwang/archive/2010/11/25/1887888.html

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/84728636

- 点赞

- 收藏

- 关注作者

评论(0)