【 FPGA 】Vivado和ISE设计流程比较(重点是Vivado IDE)

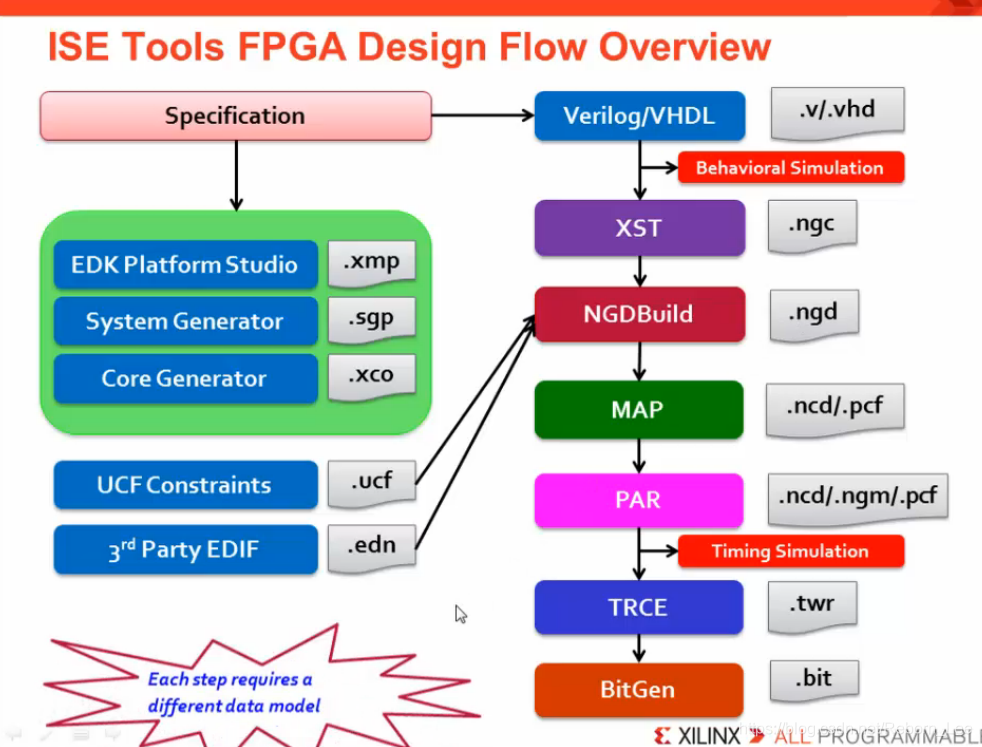

ISE工具设计流程:

NGDBuild表示翻译,MAP表示映射,PAR表示布局和布线。具体查看博文:XIlinx FPGA开发基本流程(一)(总介绍)

每一步都需要不同的数据模型。

Vivado设计流程:

也分为三个步骤,设计输入,综合,实现,红色标记的小步骤都会生成响应的dcp文件,不像ISE生成不同的文件模型。所以说,Vivado是贯穿于整个设计流程的统一的数据模型。

Vivado的设计输入可以来自于RTL代码,这里的RTL代码可以是自己编写的RTL代码也可以是由HLS、System Generator、IP生成的RTL :

从上图可以看出,这些设计输入(包括自己编写的RTL代码)都可以经过IP packaging 封装成IP放入IP Catalog中,所以说Vivado是以IP为核心的设计。

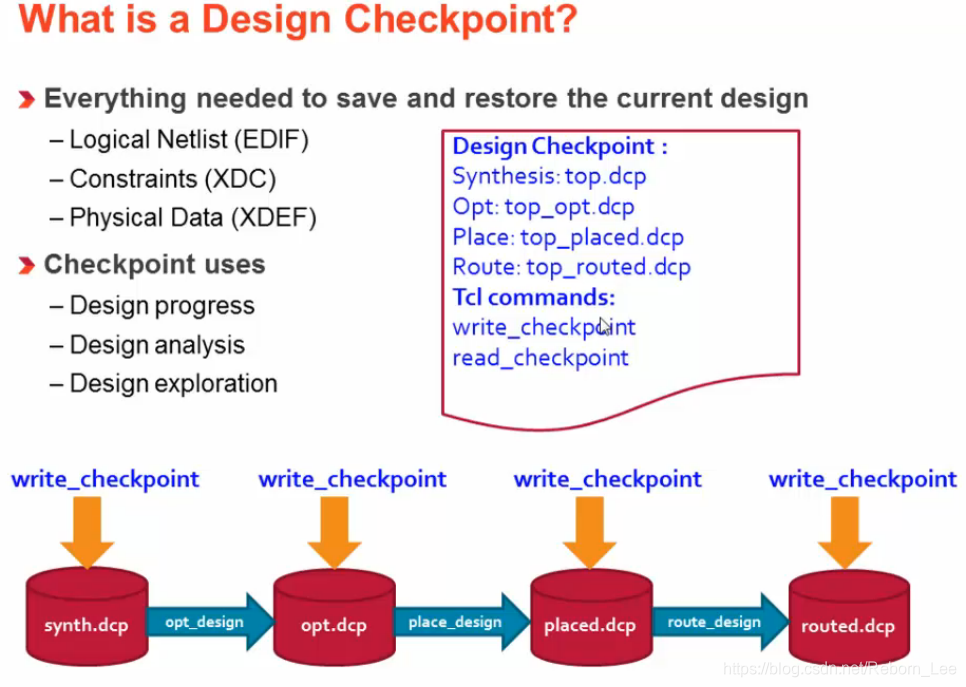

什么是Design Checkpoint(dcp)?

Design Checkpoint在synth(综合)、opt(优化)、placed(布局)、routed(布线)四个环节会生成。

dcp命令很有规则,例如工程名为top,则综合后生成的dcp命名为top.dcp,Opt之后生成的dcp命名为top_opt.dcp,同理,place之后为top_placed.dcp,Route之后为top_routed.dcp。

当然也可以用tcl脚本来生成以及读取已经生成的脚本。生成为write_checkpoint,读取为read_checkpoint。

Vivado共享数据库,只不过不同环节生成的dcp所用到的网表等不同。

Vivado支撑不同的设计输入,可以将不同的设计输入放到不同的文件夹里,Vivado的使用方式可以是Project Mode以及Non_Project Mode。

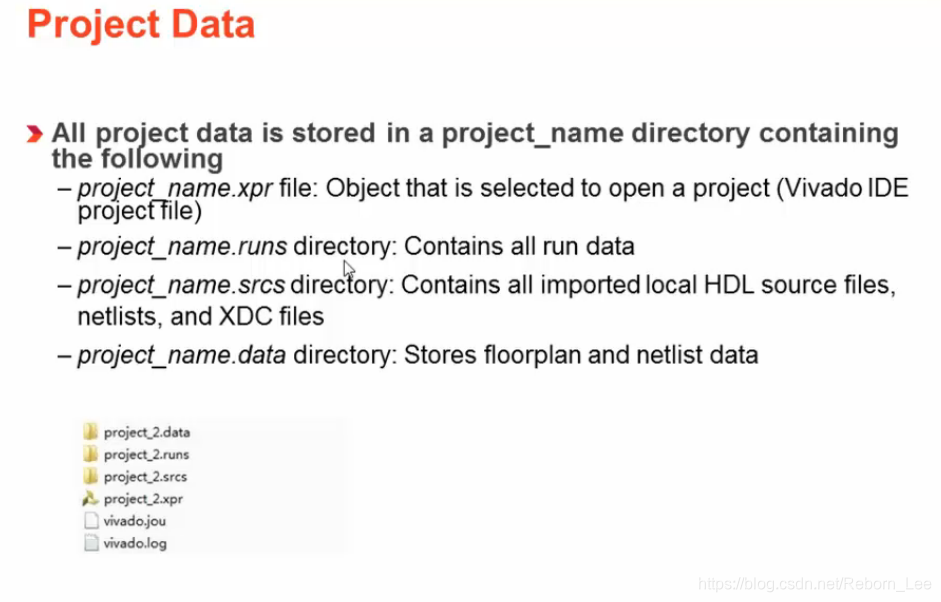

其中,以Project_Mode方式会生成下面的文件夹:

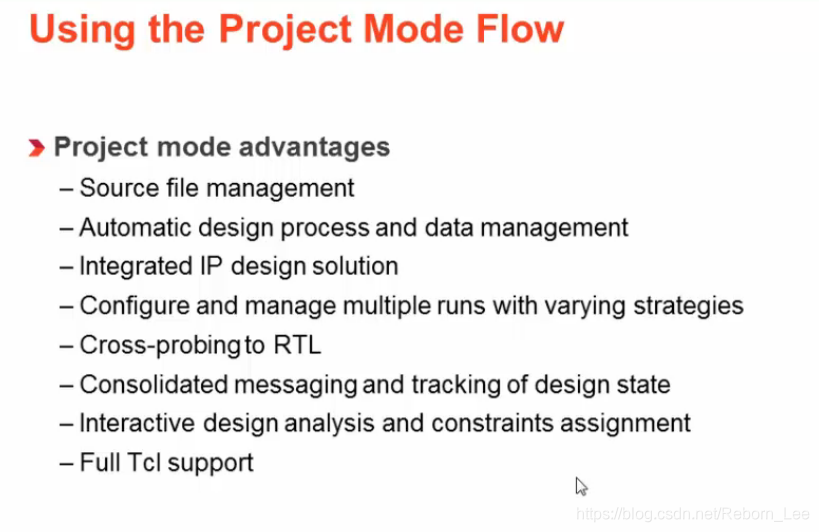

Project Mode的优势:

具有很强的交互式能力,除此之外,对于文件管理,流程控制,IP设计都非常有利。

Non_Project Mode优势:

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/84960738

- 点赞

- 收藏

- 关注作者

评论(0)