【 FPGA 】时钟偏斜及其影响

时钟偏斜的概念有很多人知道,也有很多人写成了博客,但是时钟偏斜的影响却很少有人提及,有幸偶看《高性能FPGA系统——时序设计与分析》,上面对时钟偏斜的分析可谓之全面了,记录下来备忘!

时钟偏斜的概念?

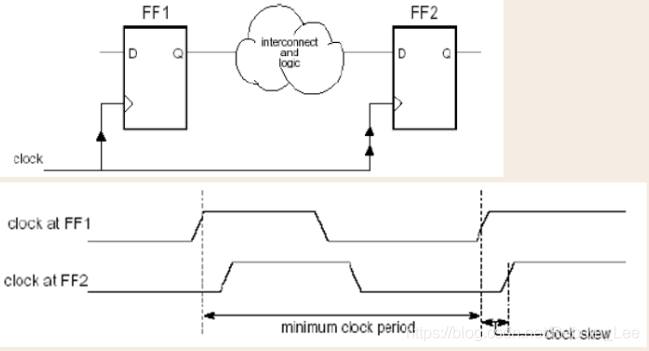

时钟偏斜是一个时钟信号沿着同一个时钟网络到达源寄存器与目的寄存器的时间差。如下图示意:

也就是说由于时钟网络布线存在传输延迟,因此时钟偏斜是同一个时钟网络上的同一个时钟沿同时作用域源寄存器和目的寄存器时的相位差。

通常布线资源的延迟是不可预测的,所以时钟网络布线应该使用FPGA提供的专用时钟资源,否则时钟偏斜会非常严重。

时钟偏斜分为正时钟偏斜和负时钟偏斜,主要对时钟周期产生影响。时序分析器能够报告时钟偏斜问题。

时钟偏斜的分类及影响?

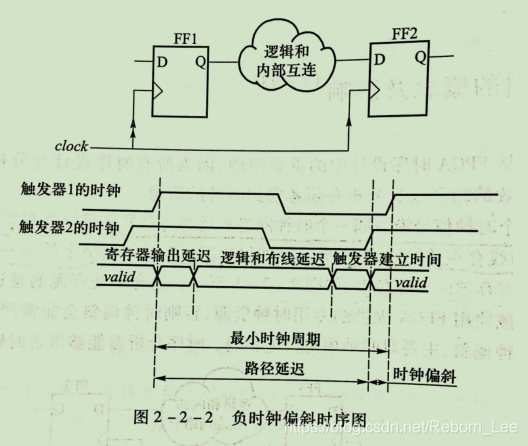

负时钟偏斜:

所谓的负时钟偏斜,即当目标寄存器时钟早于源寄存器时钟到达时,时钟偏斜称为负时钟偏斜。如下图:

负时钟偏斜意味着时钟周期必须大于两个寄存器之间的路径延迟加上负时钟偏斜的绝对值。

为了满足数据传播要求,则:

上面三个符号分别代表着寄存器之间的时钟周期、路径延迟和时钟偏斜。其中路径延迟包括,FF1(源寄存器)的输出延迟,两级寄存器之间的所有组合电路延迟和布线延迟以及FF2的建立时间。

上图展示了在负时钟偏斜情况下,最小时钟周期大于路径延迟,因此负时钟偏斜不利于提高工作时钟频率。

神来一笔:从上图可以看出,负时钟偏斜这种情况会导致,允许的路径延迟变小,或者路径延迟不变的情况下,时钟周期要求更大,大于路径延迟加时钟偏斜绝对值。

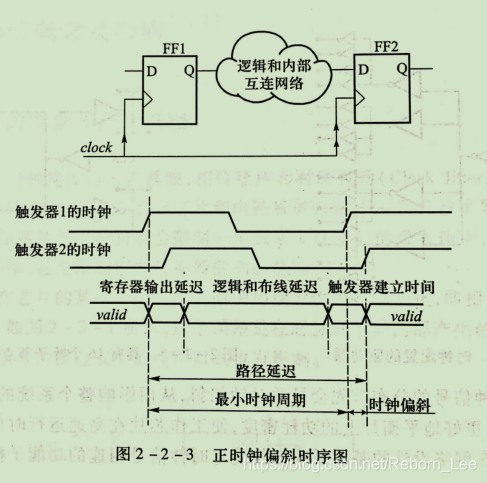

正时钟偏斜:

当源寄存器时钟早于目的寄存器时钟到达时,时钟偏斜称为正时钟偏斜。如下图:

正时钟偏斜意味着时钟周期只需大于两个寄存器之间的路径延迟减去正时钟偏斜,即

符号的意思同上一种情况。

在正时钟偏斜的情况下,最小时钟周期小于路径延迟,因此正时钟偏斜有利于提高工作时钟频率。

神来一笔:在正时钟偏斜的情况下,路径延迟不变的话,我们的时钟周期可以设计的小于路径延迟,但需同时满足上述公式。

如何降低时钟偏斜?

采用时钟分布技术降低时钟偏斜。

简单地说,就是让时钟上“树”,时钟树可以使时钟到达各个寄存器的时钟偏斜最小,关于时钟树的文章:

这里介绍再次介绍下,意思都是大同小异的。

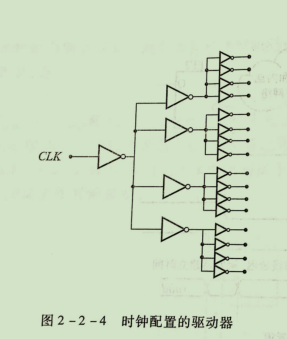

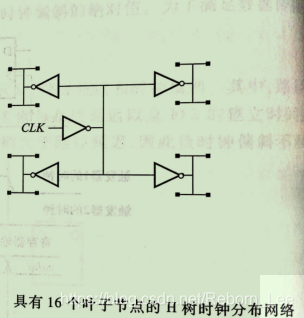

在时钟的分配路径中包含缓冲器是控制时钟偏斜最简单有效的方法,驱动器树可把时钟连线分成几段较短的长度并提供尺寸合理的缓冲器。

为了保证电路系统中时钟信号的全局统一和稳定,通常时钟分布技术都是利用均衡路径的原则将时钟信号分配到各层节点上。在不考虑芯片制造工艺和使用环境等条件下,在路径均衡时,到达各个时钟节点的信号是相同的且不存在时钟偏斜。

总之,时钟分布网络设计的基本要求就是使与时钟信号相连的功能子模块的互连线大致等长,从而保障时钟偏斜的最小化。

(时钟到达各个寄存器的延迟不是最小,而是尽可能一致。)

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/84930353

- 点赞

- 收藏

- 关注作者

评论(0)