【 FPGA 】时钟抖动浅记

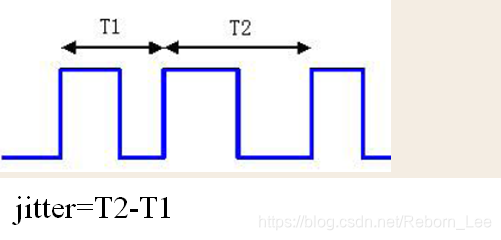

【摘要】 时钟抖动是指芯片的某一个给定点上时钟周期发生暂时的变化,即相邻两个时钟周期之间存在差值。这个误差是时钟发生器内部产生的,和晶振或者PLL内部电路有关,时钟信号传播过程中的噪声对其也有影响。

时钟抖动有两种类型:确定性抖动和随机性抖动。(暂时不展开)

降低时钟抖动的方法:

1、选择相位噪声特性好(时钟抖动小)的晶体振荡器。

2、采用合理的逻辑电平并以差分形式传输时钟...

时钟抖动是指芯片的某一个给定点上时钟周期发生暂时的变化,即相邻两个时钟周期之间存在差值。这个误差是时钟发生器内部产生的,和晶振或者PLL内部电路有关,时钟信号传播过程中的噪声对其也有影响。

时钟抖动有两种类型:确定性抖动和随机性抖动。(暂时不展开)

降低时钟抖动的方法:

1、选择相位噪声特性好(时钟抖动小)的晶体振荡器。

2、采用合理的逻辑电平并以差分形式传输时钟信号。诸如采用LVDS或LVPECL等差分方式传输信号,都能极大地降低时钟抖动;这种差分通路还能消减信号通路上的所有共模噪声、干扰和串扰。

3、谨慎处理印制板时钟信号的走线。

4、采用FPGA片内的锁相环(PLL)对输入时钟进行锁相。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/84933106

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)