【 FPGA 】Vivado中常用的5个Tcl命令

本博文内容是学习课程做的笔记,只记录了一些,由于没有基础,且讲的也不是太清楚,只吸收了一部分内容,记录下来备忘。

目录:

Objects的基本概念?

首先讲解Vivado中objects的基本概念,然后是如何使用这5个Tcl命令。

cell可以是Verilog中的实例化后的模块,也可以是一些LUT、DSP48E等资源,它们有相应的pin,pin与pin之间的连线为net,port与pin不同,port是FPGA和外部打交道的管脚。

每个port会占用一个FPGA外部管脚,称为package pin,每个package pin都在IO Bank中。

下面是五个常用的Tcl命令,它们都有一些常用的共同的参数,下面分别介绍:

上图也可以看出,-hierarchical可以简写为-hier

-of_objects则可以简写为-of

-filter意思是过滤出符合条件的objects。

隶属关系(-of_objects)?

下图是一个例子,使用这5个Tcl命令来联系-of这个参数的使用,中括号表示层次关系,从里往外读:

先是通过get_cells wbDataForInput_INUF_inst 找到图中IBUF这个cell,然后获得其pin:get_pins -of[get_cells wbDataForInput_INUF_inst] -filter{DIRECTION == OUT},注意这里有一个过滤条件,是通过cell找到pin,这个pin是输出的pin;

通过pin去找到net:get_nets -of[get_pins -of[get_cells wbDataForInput_INUF_inst] -filter{DIRECTION == OUT}],找到上面蓝色的net,最后通过net找到与之相连的cell:

get_cells -of [get_nets -of [get_pins -of [get_cells wbDataForInput_INUF_inst] -filter {DIRECTION == OUT}]]

得到三个与之相连的cells:

wbDataForInputReg_reg validForEgressFifo_reg[o]_i_1 wbDataForInput_IBUF_inst

下面继续举例,如何使用参数 -of_objects:

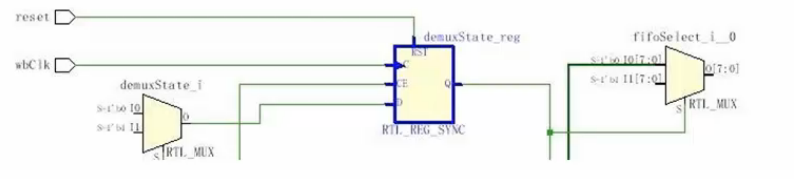

放大电路:

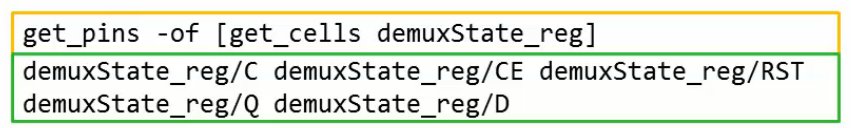

先指定蓝色cell,get_cells demuxState_reg,使用Tcl命令get_pins -of获得它的pins:

get_pins -of [get_cells demuxState_reg]

得到上面绿色框内的pins;

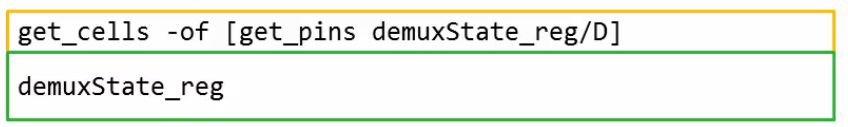

再获得指定pin的cell,通过下面的Tcl命令找到响应pin的cell:

get_cells -of [get_pins demuxState_reg]

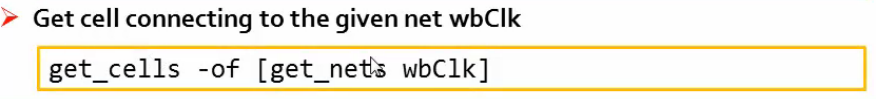

通过特定的net找到相应的cell:

下面例子雷同:

-hierarchical 解释?

-hier 表示按层次寻找:

例如:

Tcl命令: get_cells {A* B*}

注意A后面的* 是通配符,使用上面的Tcl命令后就得到

A B这两个模块。结果可以看出,它只从顶层寻找,并没有再往下找:

如果使用参数 -hier,例如下Tcl命令: get_cells -hier [A* B*]

得到: A A/A1 A/A2 B B/B1 B/B2

如果使用分隔符“/”呢?

例如Tcl命令: get_cells B/*

很容易想到得到如下结果: B/B1 B/B2

注意,分隔符和参数 -hier不能同时使用,如果同时使用,就会找不到与之匹配的模块,上图中有示意。

最后讲下带有参数 -filter的Tcl命令,用于过滤出一些符合条件的模块显示出来:

例如Tcl命令:get_cells -hier -filter {NAME =~ *B*}

就会得到: B B/B1 B/B2

最后需要注意的是B2的实例化名字为:

I/O Port属性?

I/O Bank 和 Package Pin的属性?

跟不上了,过段时间自己总结。

笔记来源:《Vivado入门与提高》

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/84977359

- 点赞

- 收藏

- 关注作者

评论(0)