【 FPGA 】时序分析中的基本概念和术语

这个笔记记录的是《Vivado入门与提高》课程的关于时序分析的这一节的内容,目的是为了备忘。

其实,以前也有这样的博文了,这里再次记录下是为了加深印象与理解。静态时序分析

目录

Launch vs Capture Edges

有的书上也叫做 Launch and Latch Edges,Launch Edge是源端寄存器发送数据的边沿,通常为上升沿,Capture Edge为目的寄存器捕获数据的边沿,二者之间的距离为一个时钟周期,Capture Edge也称为下一个Launch Edge。

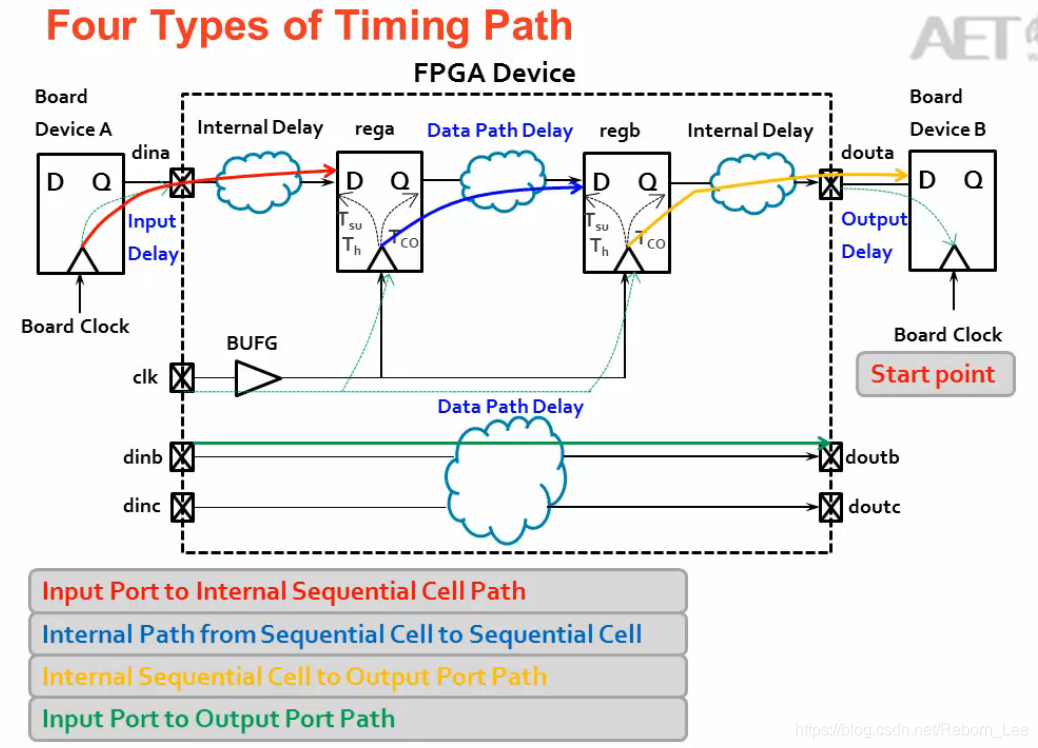

Timing Path

有四种类型的时序路径如下图所示,第一类路径为外部器件的时钟端到FPGA内部时序器件的路径,如下图红色箭头表示;

第二类路径为FPGA内部时序器件到时序器件的路径,具体就是时序器件的时钟输入端口到另一个时序器件的数据输入端口之间的路径,如下图蓝色箭头所示;

第三类路径为FPGA内部的时序器件到外部器件端口的路径,如下图黄色箭头所示;

第四类路径为输入端口到输出端口之间的路径,如下图绿色箭头所示。

我们要关注的是这些路径的起始点(start point)和终止点(end point)。如下图:

第一类路径的起始点是外部器件的末端寄存器的时钟输入端,终点是FPGA内部寄存器的数据输入端,其他类似。

前三类有共同的特点就是一个寄存器的时钟输入端到另一个寄存器的数据输入端,只不过寄存器可能在同一个芯片中,也可能不在同一个芯片中。

最后一类是纯组合逻辑。

Timing Path Sections

源端时钟路径:起点为clk input port,终点为发射寄存器的clk pin。

数据路径:发射寄存器的clk pin到捕获寄存器的data input pin。

目的端时钟路径:时钟输入端口到捕获寄存器的clk pin。

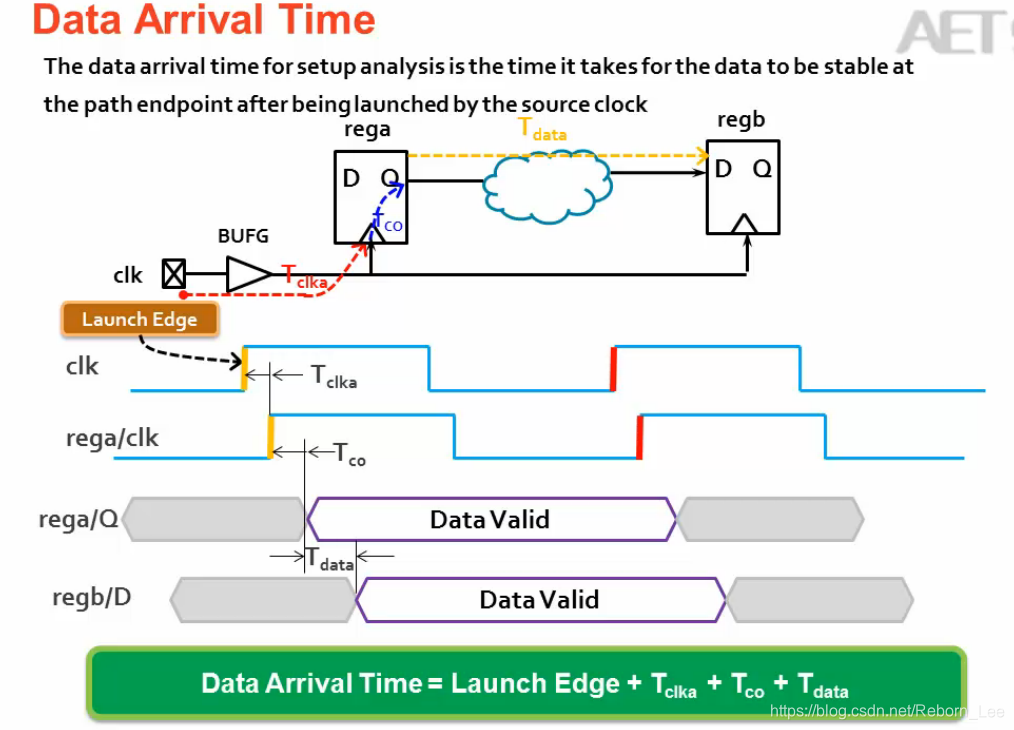

Data Arrival Time

Tclka为时钟到达寄存器的时钟输入端的延迟,Tco为数据从时钟有效沿开始到输出之间的延迟,Tdata为数据经过组合逻辑以及布线延迟到达目的寄存器输入输入端之间的延迟。

数据到达时间就是上面三种延迟的叠加。

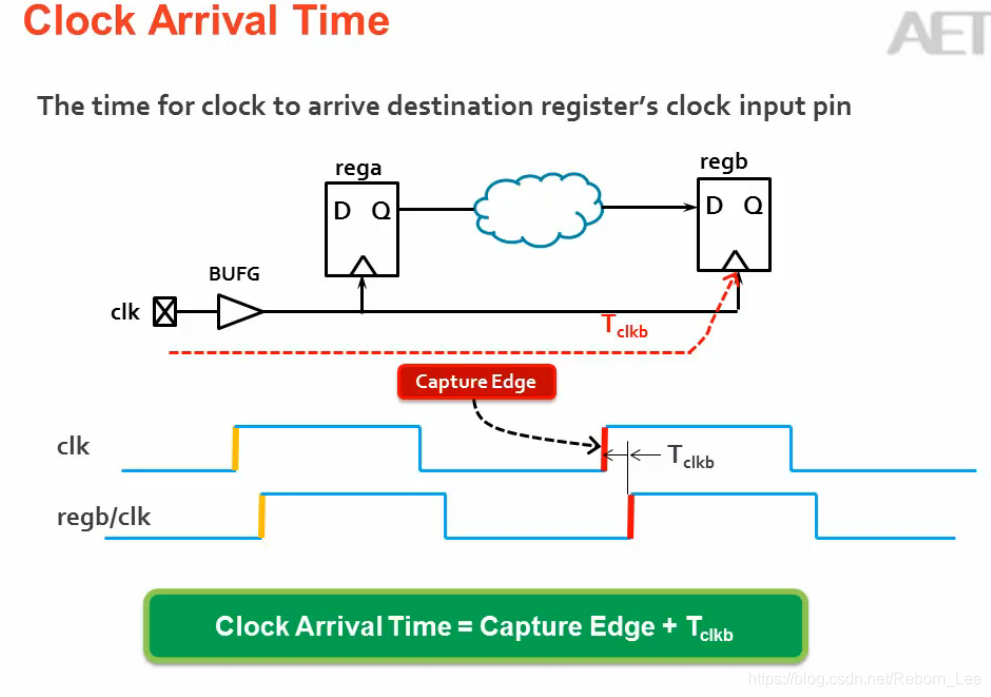

Clock Arrival Time

时钟到达时间就是时钟到达捕获寄存器的时钟输入端之间的延迟。如上图,捕获寄存器的参考时钟对于系统时钟有一定的延迟。

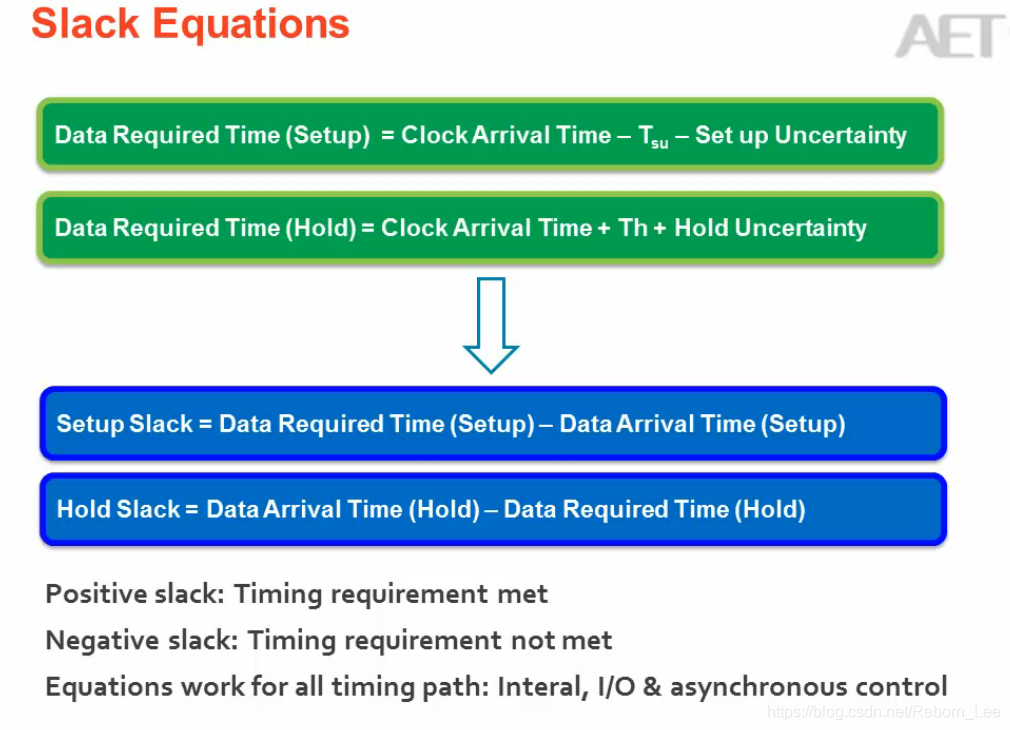

Data Required Time - Set up

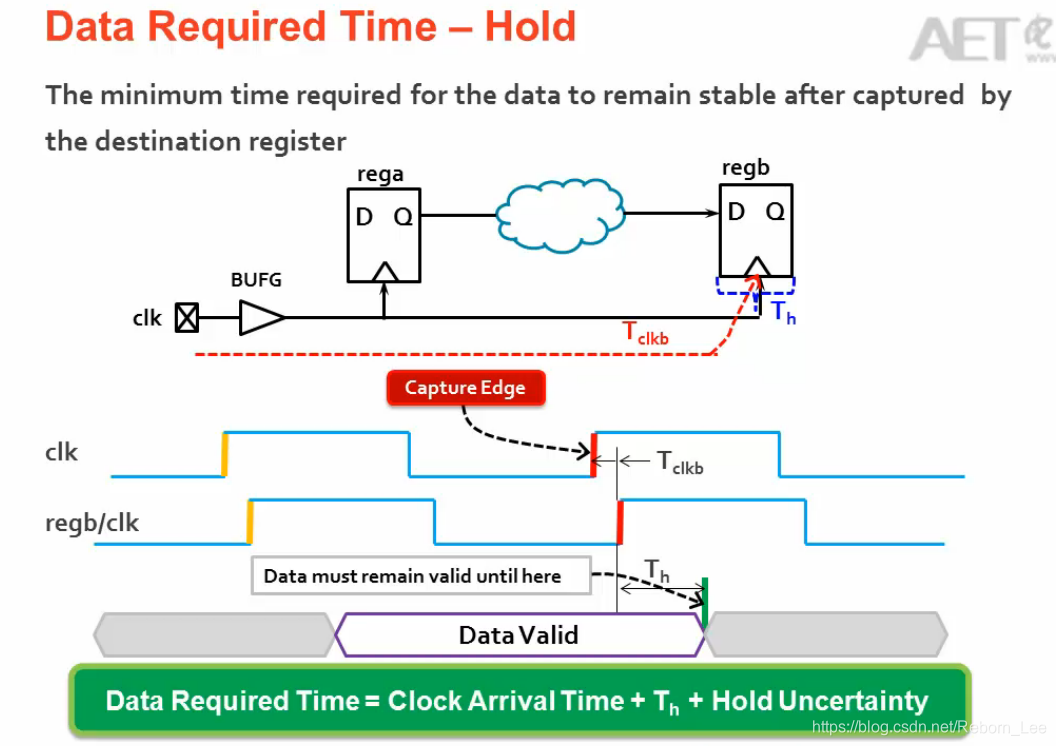

Data Required Time - Hold

Setup Slack

数据到达目的寄存器后到数据建立时间之前的一段时间为数据建立时间裕量。

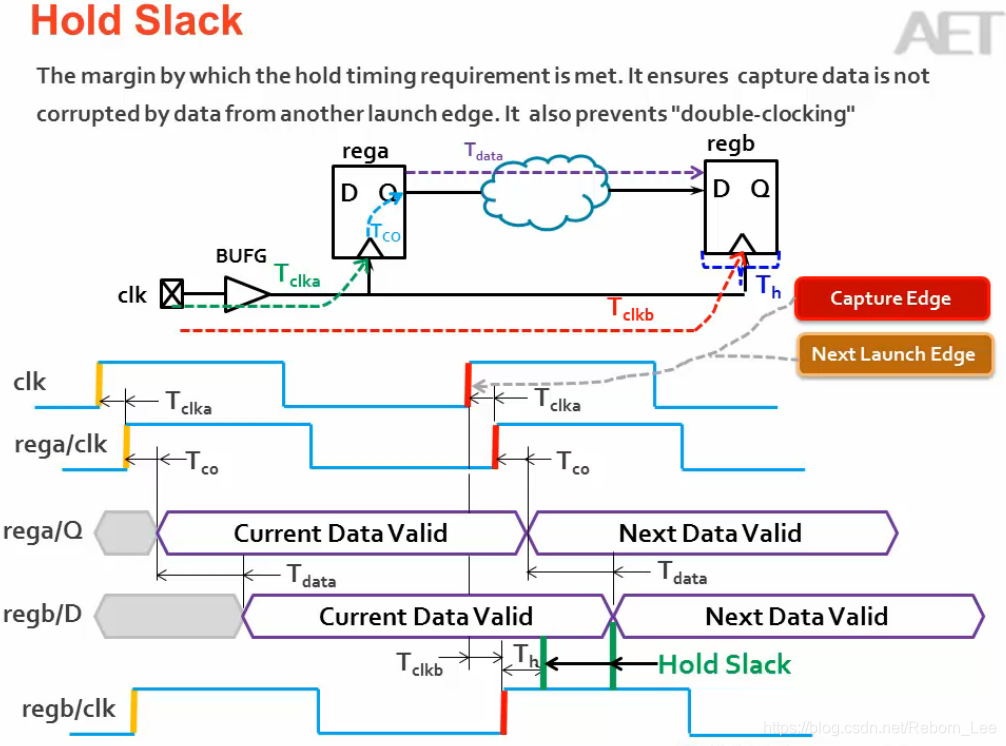

Hold Slack

平心而论,这里讲的真的很模糊,是靠视频弄清楚一些东西还是很难的,还是要看之前的博文:时序分析之静态时序分析。

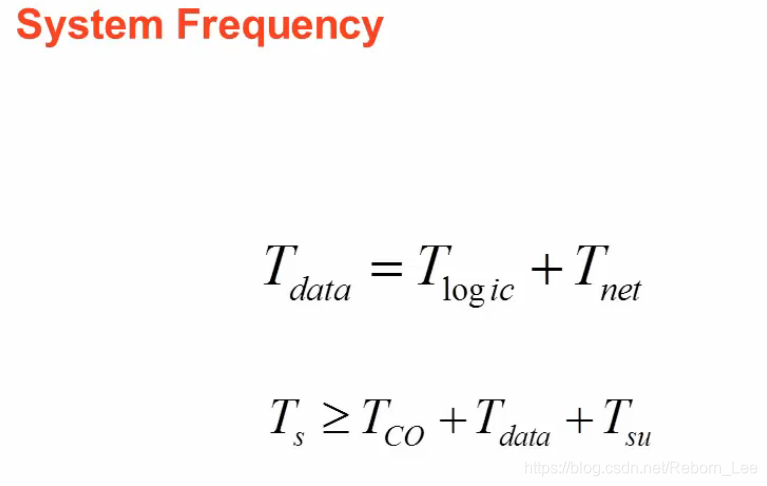

系统时钟最小为:

建立时间裕量为0,就得到了系统最小时钟周期。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/84990766

- 点赞

- 收藏

- 关注作者

评论(0)