【 FPGA 】Xilinx设计约束(XDC)中时钟约束的表示方法

目录

时钟描述

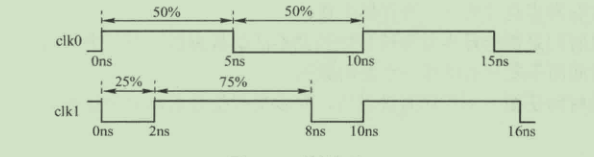

(1)clk0的时钟属性:周期为10ns,占空比为50%,相移为0ns;(相移也可以用°来表示,例如相移位0°,相移为90°等)

(2)clk1的时钟属性:周期为8ns,占空比为75%,相移为2ns;(相移为2ns,也就是相移为90°)

描述时钟,默认第一个值为上升沿,占空比是高电平占周期的比。

则上图中时钟的描述方法可以为:

(1)clk0: period = 10, waveform = {0 5}

(2)clk1: period = 8, waveform = {2 8}

周期和波形属性表示了一个时钟的理想特性。点进入FPGA元器件或者通过时钟树传播时,时钟边沿存在延迟,并且由于噪声和硬件行为导致时钟发生变化,这些特性称为时钟网络延迟和时钟的不确定性。不确定性包括时钟抖动、相位误差,以及由设计者指定的任何其他不确定性。

通常,由板上的元器件通过FPGA输入引脚为FPGA中的时钟资源提供时钟。此外也可以通过FPGA内称为时钟修改模块的特殊原语生成时钟,如MMCM,DCM,PLL等。

基本时钟

一个基本时钟是指PCB上的时钟,它通过下面方式输入设计中:

(1)一个输入端口;

(2)一个吉比特收发器输出引脚。

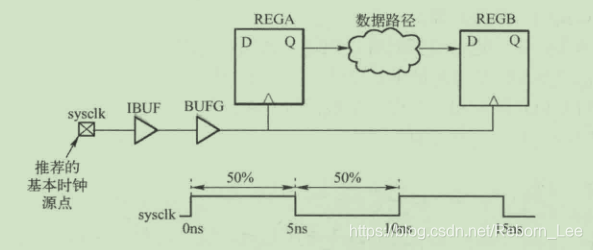

下面给出一个基本时钟例子:

在这个例子中,通过名字为“sysclk”的端口,将PCB上的时钟引入FPGA元器件中,并且通过输入缓冲器和一个时钟缓冲器,最终到达路径上的寄存器。该时钟的属性为:周期为10ns,占空比为50%,无相移。

在Xilinx设计约束中(XDC),将该时钟约束表示为:

create_clock -period 10 [get_ports sysclk]

类似地,PCB上一个名为“devclk”的时钟通过端口CLKIn输入FPGA内。该时钟属性为:周期为10ns,占空比为25%,相移为90°。则在XDC,将时钟约束表示为:

create_clock -period 10 -waveform{2.5 5} [get_ports CLKIn]

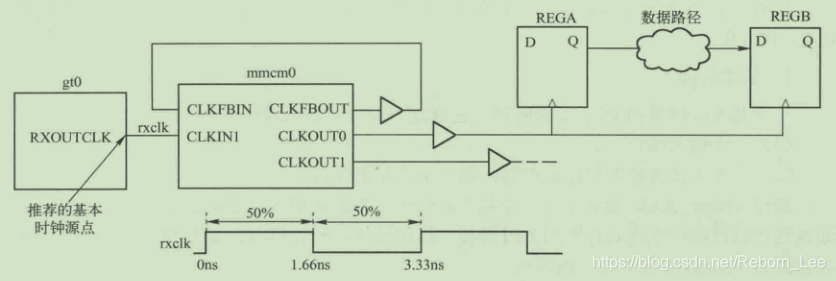

下面给出一个GT基本时钟的例子。

一个收发器gt0用于从PCB的一个高速链路中恢复时钟rxclk,该时钟属性为:周期为3.33ns,占空比为50%,该时钟连接mmcm0,该模块生成一些补偿后的时钟,用于设计。

在XDC,将该时钟约束表示为:

create_clock -name rxclk -period 3.33 [get_pins gt0/RXOUTCLK]

虚拟时钟

昨天博文写到这里就断了,因为傻傻弄不明白虚拟时钟是什么意思?

今天看了博文,恍然大悟,博文链接:https://www.cnblogs.com/IClearner/p/6658822.html

作者以多时钟同步约束为话题,提到了虚拟时钟,这里借用一下:

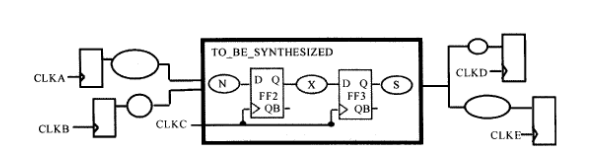

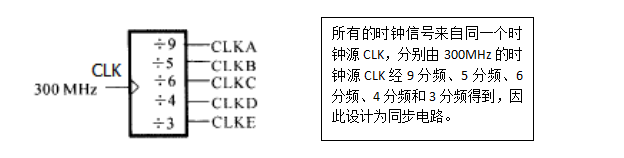

我们要综合的模块的时钟是CLKC,但是前后模块的时钟不一定是CLKC,但是前后模块的时钟跟CLKC是来源于同一个时钟的,比如说经过锁相环分频或者倍频,这里拿分频来举例,比如说CLKA、 CLKB、CLKC、CLKD、CLKE都是由同一个时钟CLK经过分频得来,如下图所示:

在我们要综合的电路中,只有一个时钟端口CLKC,即只有CLKC时钟驱动要综合电路中的寄存器。其他的时钟CLKA,CLKB,CLKD和CLKE在我们要综合的电路中并没有对应的时钟端口。因此,它们并不驱动要综合电路中的任何寄存器。它们主要用于为输入/输出端口延时作约束,可能会出现一个端口有多个约束的情况。

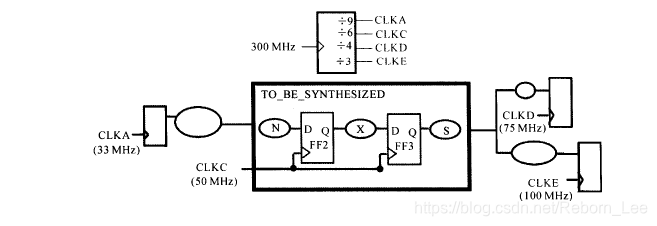

下面我们根据上面的例子作多时钟的同步设计约束,也就是为下面的电路类型做约束:

CLKC在要综合的设计中有对应的输入端口,其定义与单时钟时一样,即:

create_clock -period 20 [get_ports CLKC]

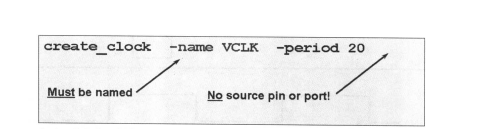

由于CLKA,CLKD和CLKE在要综合的设计中没有对应的输入端口,因此需要使用虚拟(virtual)时钟。虚拟时钟在设计里并不驱动触发任何的寄存器,它主要用于说明相对于时钟的I/O端口延迟,DC将根据这些约束,决定设计中最严格的约束。建立虚拟时钟的格式如下:

上面定义了名字为VCLK的虚拟时钟,周期为20ns。因为虚拟时钟不驱动设计中的任何寄存器,设计中没有其对应的输入端口。所以定义中没有源端口或引脚。由于虚拟时钟没有对应的时钟端口,我们必须给它一个名字。与一般时钟一样,虚拟时钟是DC的内存里已定义的时钟物体(设计对象),它(们)不驱动(触发)当前设计中的任何寄存器。用作为输入/输出端口设置延迟。

就到这里,具体的话还是要看,参考的博文。

不得不说,互联网上的高人还是很多的,很多写书人以及讲课人根本就没有考虑到去解释什么是虚拟时钟,就连何宾老师的Xilinx FPGA权威设计指南,这块写的也是让人一头雾水,不知所云,更别提一些视频上的说法了,直接略过。这里感谢上面的博主。

这里需要重点说明的是,在输入输出延迟约束中使用虚拟时钟前,一定要首先定义虚拟时钟。

至于输入和输出延迟约束的问题,会有专门的博文来总结。

生成时钟

生成时钟由设计内特殊的称之为时钟修改模块(例如MMCM)的单元或者一些逻辑生成,生成时钟总是和一个基本时钟或者其他生成时钟相关。通过它们的主时钟,可以直接得到生成时钟的属性。在生成时钟中,不指定它们的周期和波形,而是设计者描述正在修改的电路如何对主时钟进行变换。

首先定义所有的基本时钟,它们用于定义所要生成的时钟。

1)用户定义的时钟

通过命令create_generated_clock定义用于所需要的时钟;

将其连接到一个网表对象,最好是时钟树根引脚。

使用“-source”选项指定主时钟,该选项表示在设计中通过一个引脚或者端口传播主时钟。常见的是,“-source”选项可以使用主时钟源点或者生成时钟源单元的输入时钟引脚。

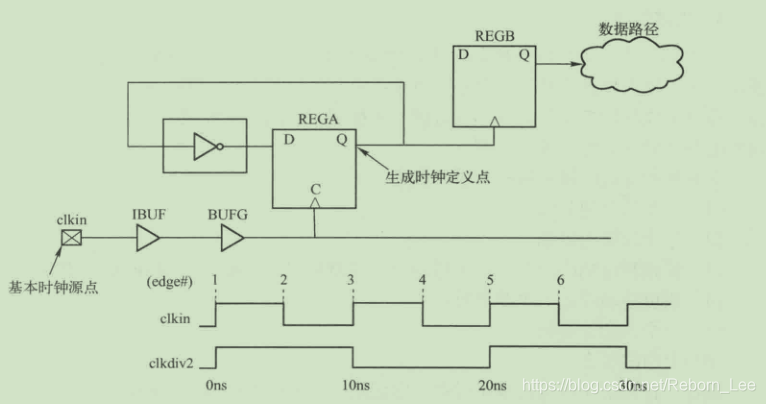

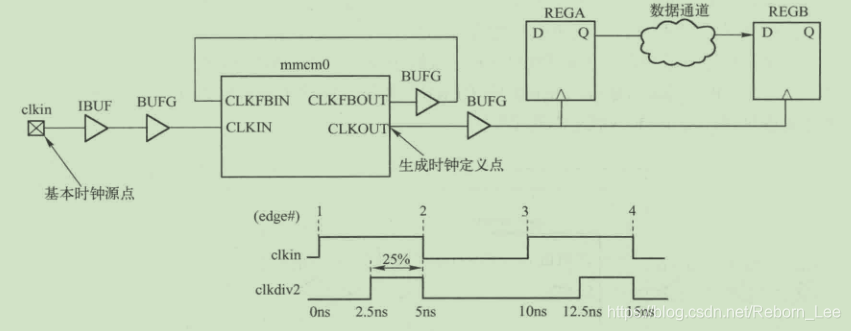

如下图给出一个生成时钟的例子:该例中基本时钟的周期是10ns,通过REGA进行二分频,该分频时钟驱动另一个寄存器的时钟引脚。相应的,将生成的时钟称为clkdiv2.

在XDC中,其等效的约束表示为:

先列出基本时钟:

create_clock -name clkin -period 10 [get_ports clkin]

生成时钟可以由两种方式写出:

(1)

create_generated_clock -name clkdiv2 -source [get_ports clkin] -divide_by 2 [get_pins REGA/Q]

(2)

create_generated_clock -name clkdiv2 -source [get_pins REGA/C] -divide_by 2 [get_pins REGA/Q]

此外,可以不适用-divide_by选项,而是用-edge选项代替它,根据主时钟的沿直接描述生成时钟的波形。它的参数是主时钟边沿的索引,以列表形式给出。该列表用于定义生成时钟沿的位置,它起始于时钟的上升沿。

如:

create_generated_clock -name clkdiv2 -source [get_pins REGA/C] -edges {1 3 5} [get_pins REGA/Q]

当需要相移时,可以使用选项"-edge_shift",可以对生成时钟波形的每个沿移动正值或者负值。

见下面这个例子:

clkin是主时钟,其属性可以表示为:周期为10ns,占空比为50%。该时钟最终连接mmcm0模块,由该模块产生一个时钟,其属性表示为:占空比为25%,相移为90°。这个生成时钟参照主时钟沿1、2和3定义,这些沿发生在0ns,5ns,和10ns。为了得到希望的波形,将第一个和第三个沿移动2.5ns。

在XDC中,该生成时钟表示为:

create_clock -name clkin -period 10 [get_ports clkin]

create_generated_clock -name clkshift -source [get_pins mmcm0/CLKIN] -edge {1 2 3} -edge_shift {2.5 0 2.5} [get_pins mmcm0/CLKOUT]

同样是针对上面的那个图,这里给出最后一个例子,我们要产生一个生成时钟,它是对主时钟乘以4/3.在XDC中,推荐将生成的时钟表示为:

created_generated_clock -name clk43 -source [get_pins mmcm0/CLKIN] -multiply_by 4 -divide_by 3 [get_pins mmcm0/CLKOUT]

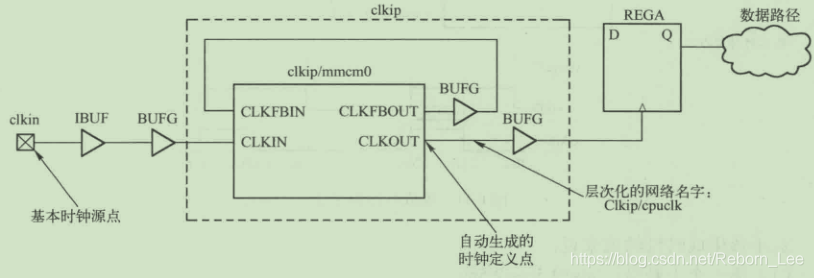

2)自动得到的时钟

自动得到的时钟也称为自动生成的时钟。Vivado集成开发环境在时钟修改模块(Clock Modifying Blocks,CMB)的输出引脚自动创建这些约束。(CMB是MMCM、PLL原语)

如果在相同的网表对象上定义了用户(基本的或者生成的)时钟,则不会创建自动生成的时钟。自动生成的时钟的名字取决于和定义点直接相连的网络名字。

下图给出一个例子:

该例子说明了由MMCM生成的时钟。在该例子中,主时钟clkin驱动clkip/mmcm0的CLKIN输入。自动生成的时钟名字是“cpuclk”,它的定义点是“clkip/mmcm0/CLKOUT”。

可以使用命令:

get_clocks -of_objects <pin/port/net>查询自动生成的时钟。

这篇博文暂时讲到这里,下篇博文继续讲解相关内容。

本文总结参考文献:Xilinx FPGA权威设计指南——Vivado 2014集成开发环境

https://www.cnblogs.com/IClearner/p/6658822.html

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/85040929

- 点赞

- 收藏

- 关注作者

评论(0)