【 FPGA 】设置输出延迟(Output Delay)

【摘要】 上篇博文是设置输入延迟:设置输入延迟,这篇博文基本和上篇博文一致,下面一起看看:

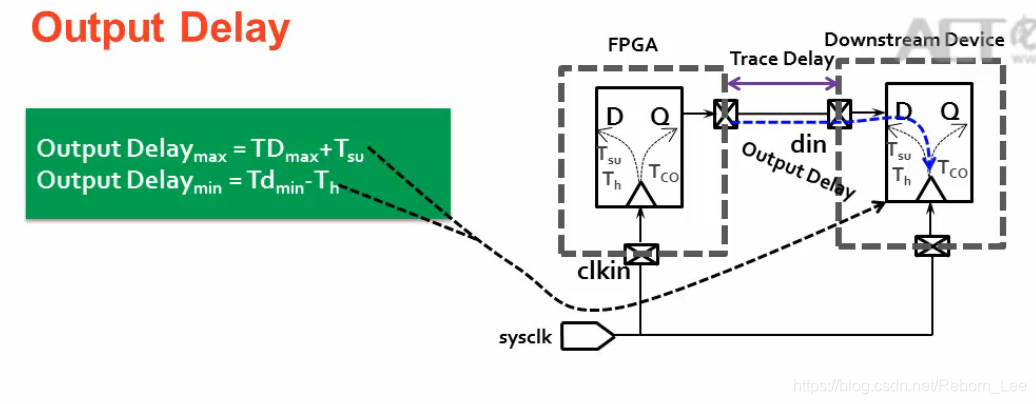

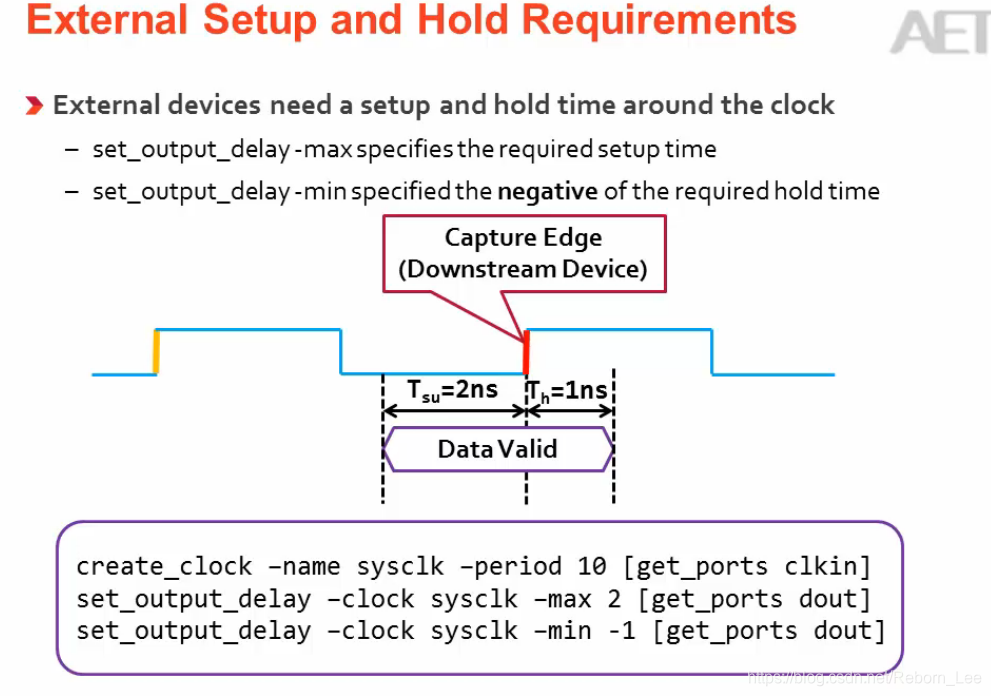

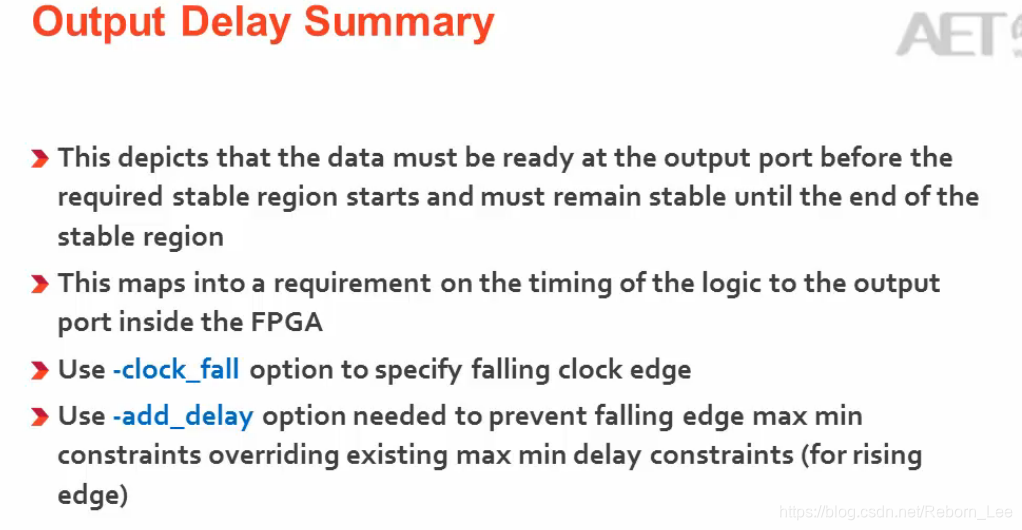

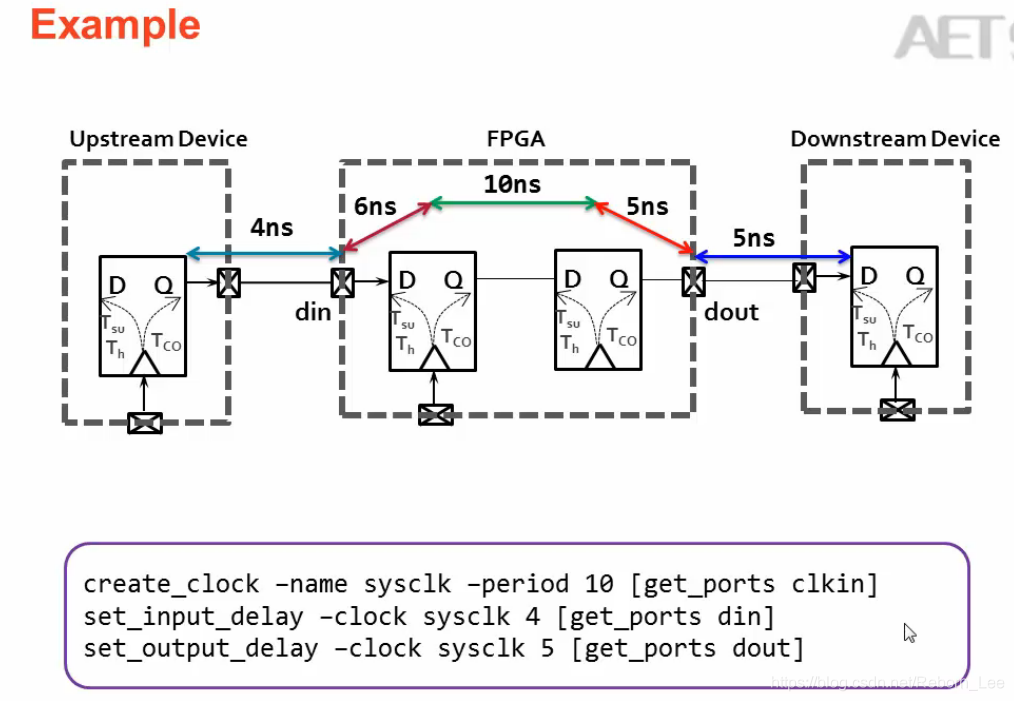

在XDC中,参考点为下游芯片的捕获沿,相比于ISE的UCF,参考点是发送沿。二者之间的关系如上图所示。

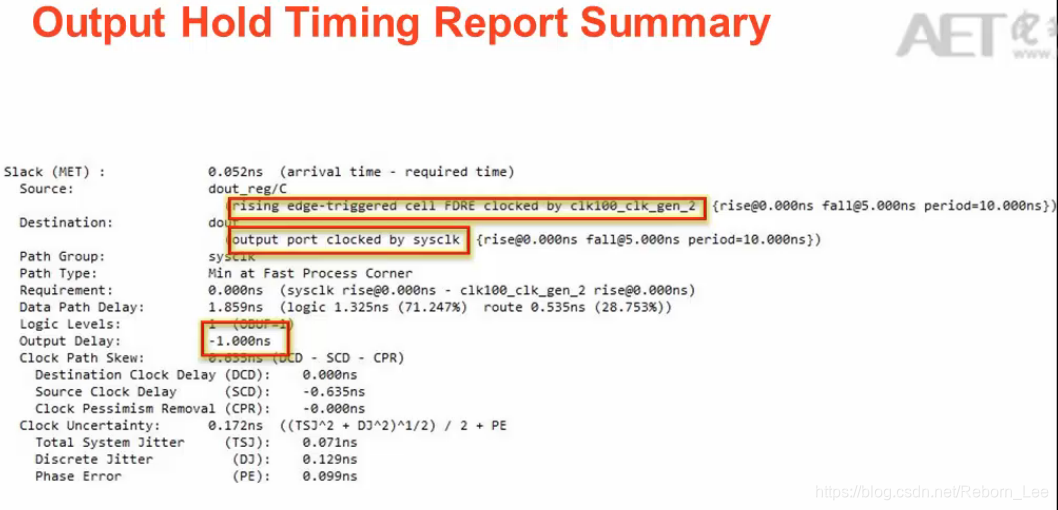

由于是下游芯片的捕获沿为参考点,所以建立时间为正,保持时间为负。

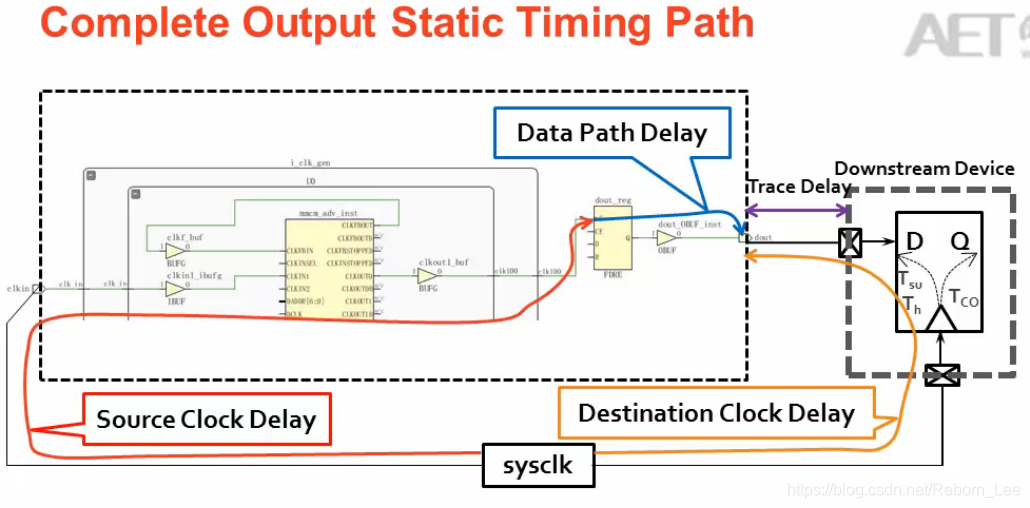

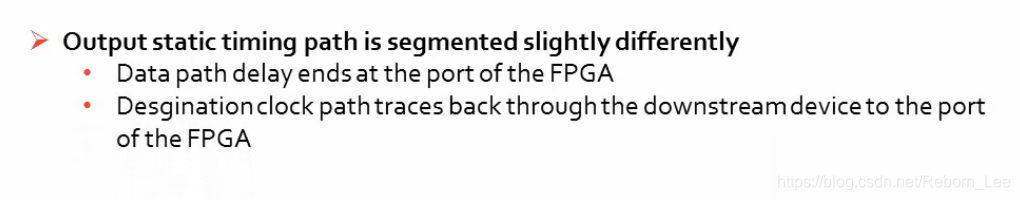

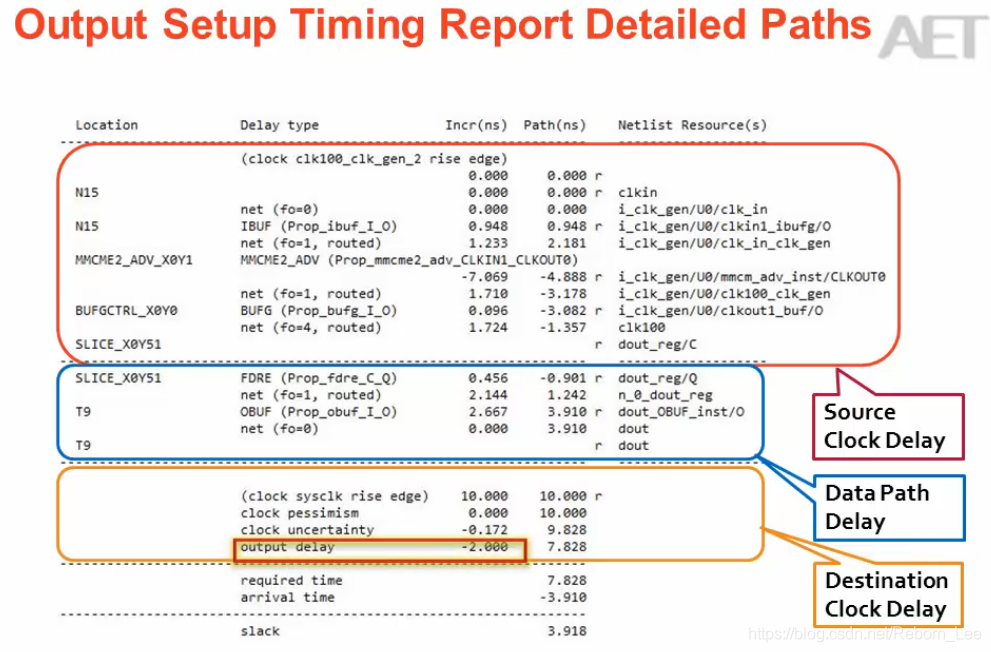

下面分析静态时序路径:

...

上篇博文是设置输入延迟:设置输入延迟,这篇博文基本和上篇博文一致,下面一起看看:

在XDC中,参考点为下游芯片的捕获沿,相比于ISE的UCF,参考点是发送沿。二者之间的关系如上图所示。

由于是下游芯片的捕获沿为参考点,所以建立时间为正,保持时间为负。

下面分析静态时序路径:

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/85056982

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)