【 FPGA 】设置伪路径

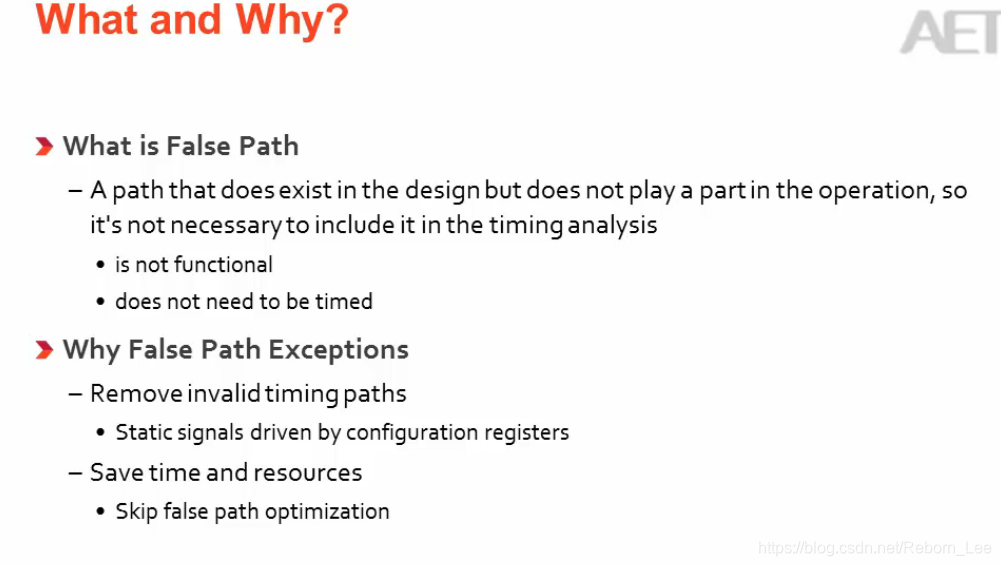

什么是伪路径?

伪路径就是存在,但是不起作用的路径,因此没有必要对它进行时序分析。

为什么要排除伪路径?

这样可以移除无效的时序路径;

跳过路径优化,因此可以节省时间和资源。

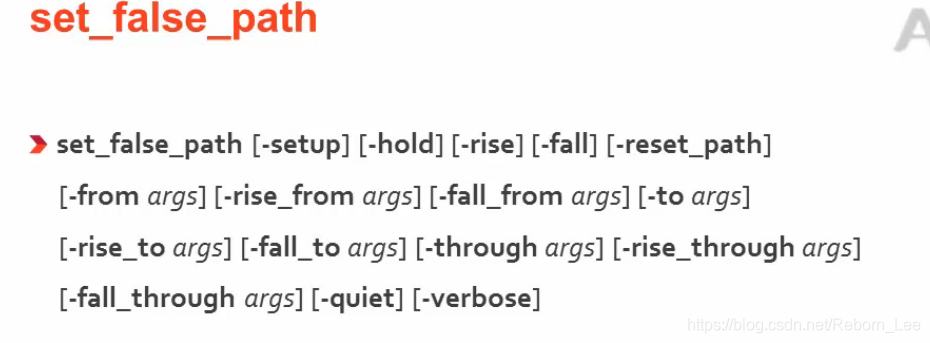

设置伪路径需要用到的Tcl命令语法?

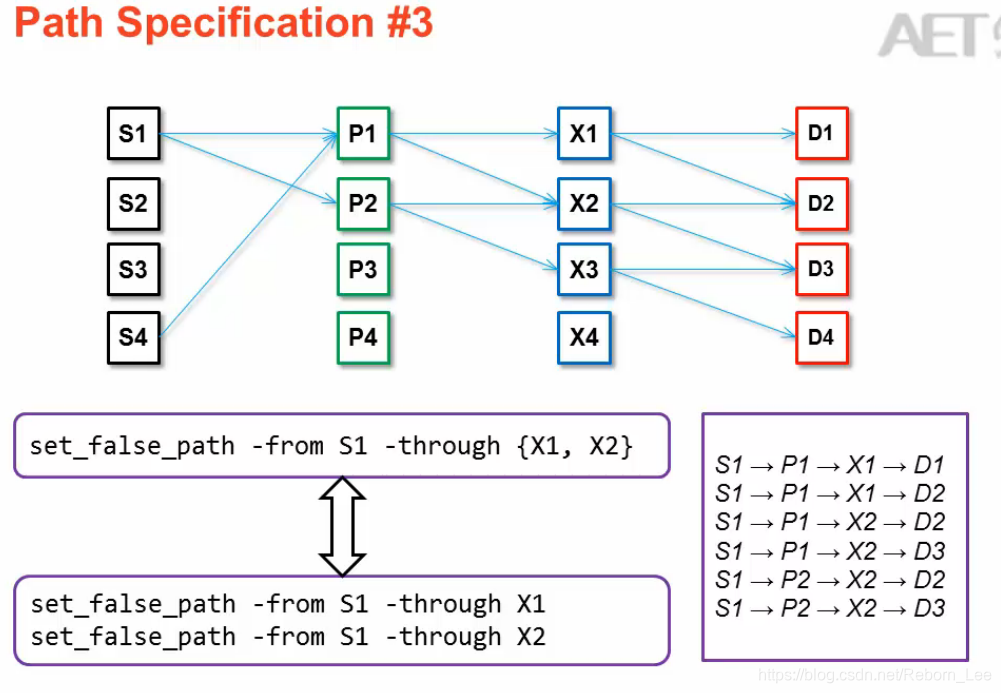

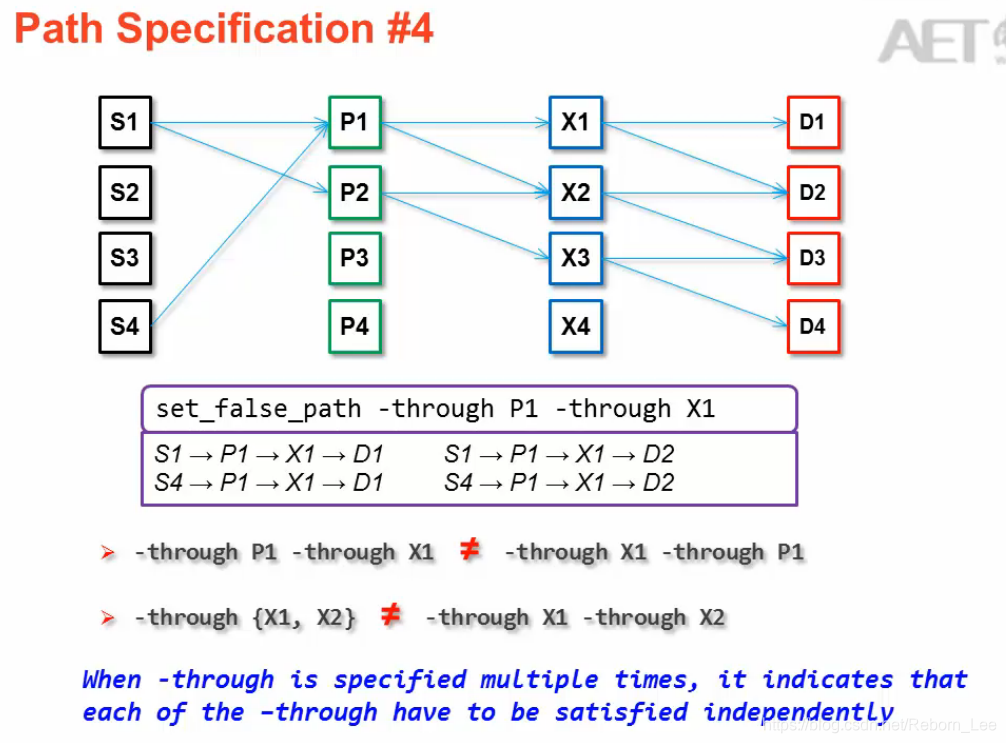

如下图所示,比较常用的参数是-from -through - to等。

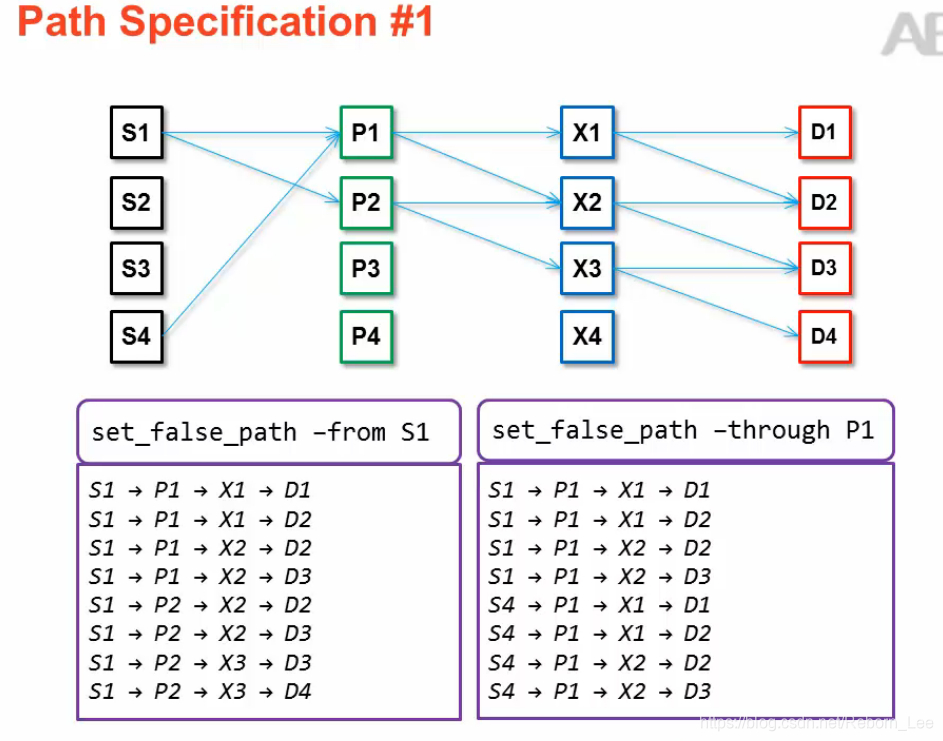

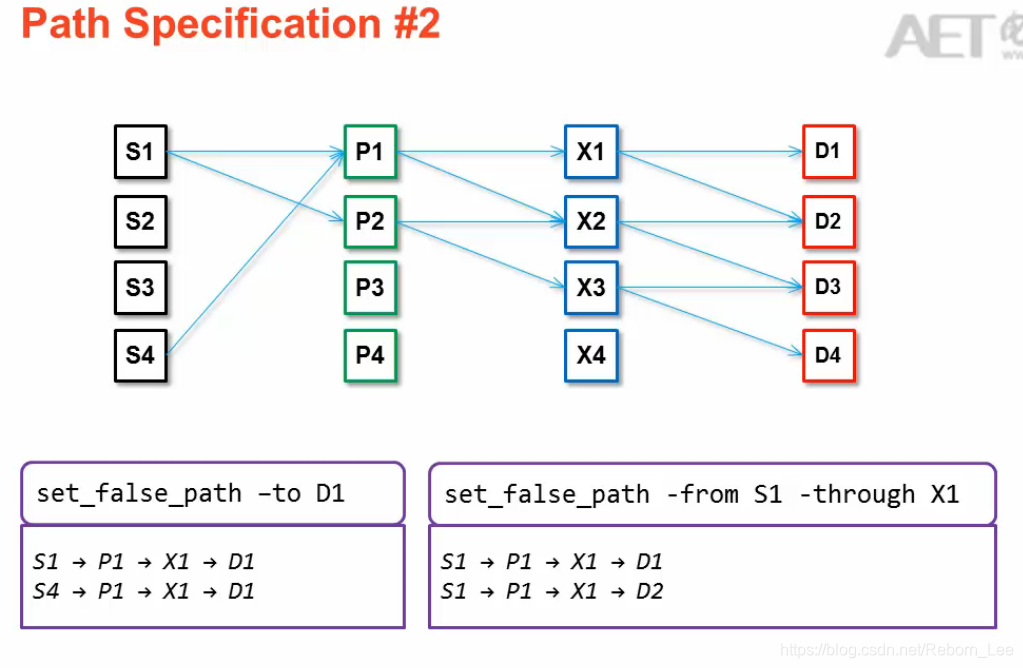

举例说明各参数的含义:

典型伪路径的含义:

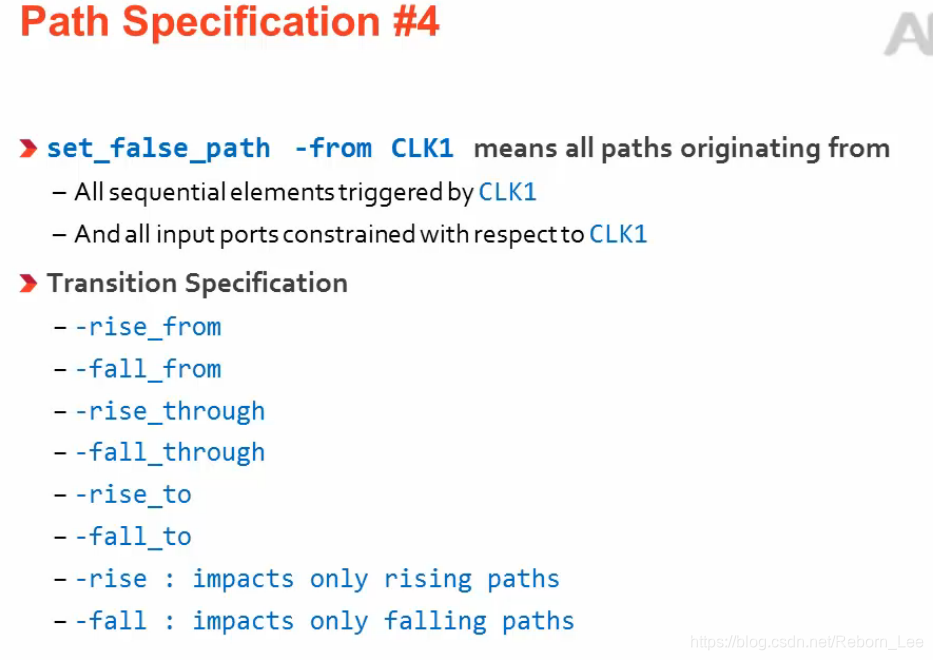

set_false_path -from CLK1,这条Tcl命令意味着这样的路径被设置为伪路径:

路径源于有CLK1驱动的所有时序元件;

源于被CLK1约束的输入端口。

伪路径的类型?

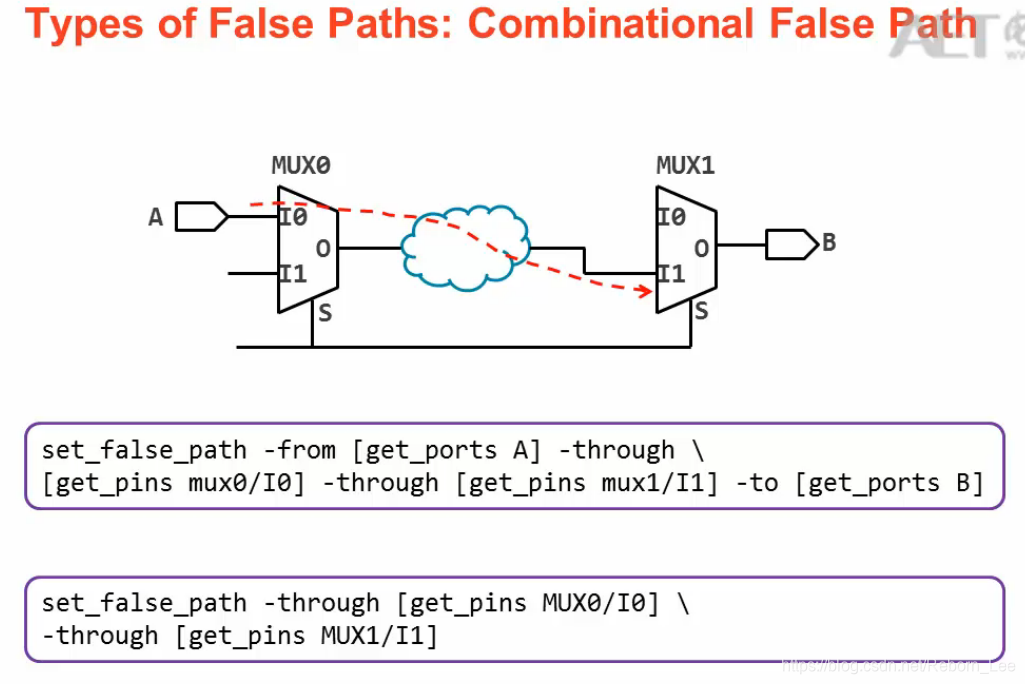

组合逻辑路径:如下图的组合路径,由两个多路选择器构成,且控制端由同一控制信号驱动,明显这条路径根本没有存在的必要,因为它没有作用,因为控制信号一致,mux选择的端口也一致,但是二者之间的连接却不是一致的,这样的话,路径的存在就没有意义。

下图给出了两种设置这个伪路径的方式,第一种过于繁琐,推荐第二种。

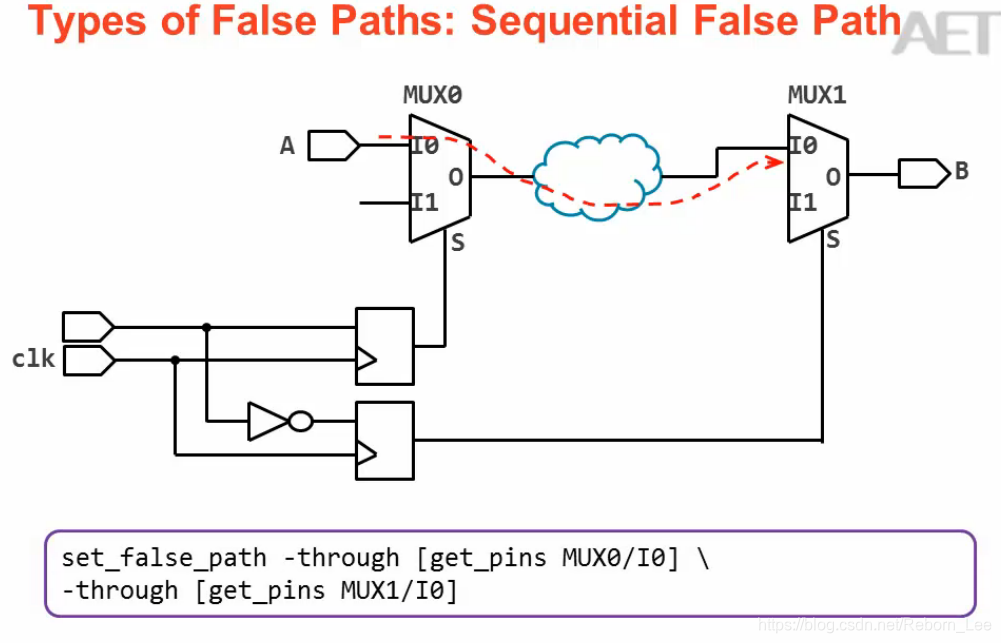

再给出一种伪路径的类型,这个类型是上一个类型的进化版,加上了时序元件而已,但是这条路径同样没有什么意义?

因为尽管二者的mux选中的端口连接到了一起,但是控制信号却是相反的,例如,mux1选中I0的时候,Mux0选中I1。搞笑?

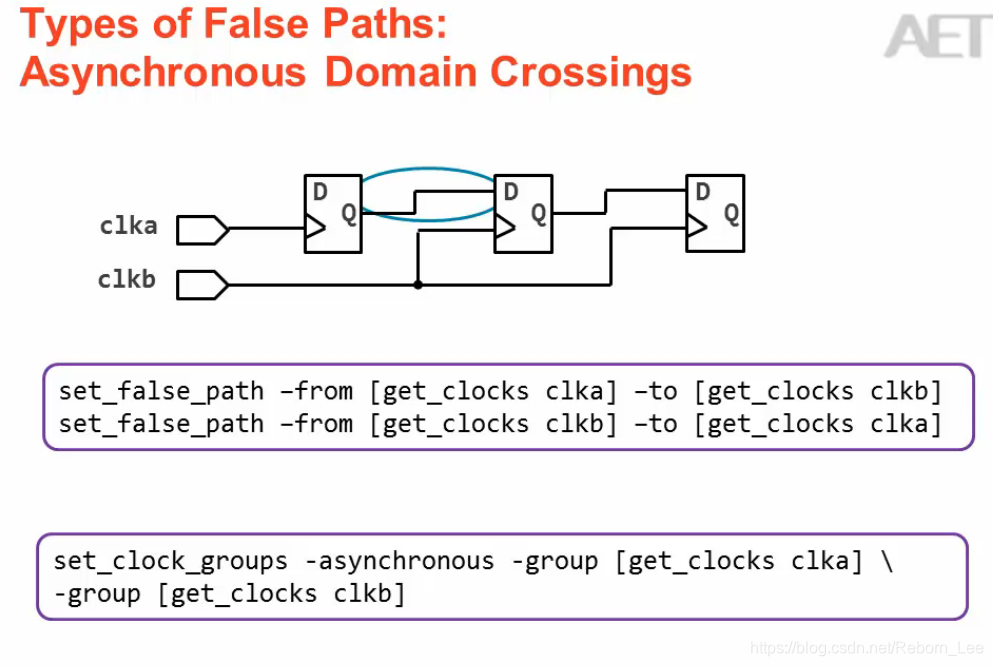

下图这种伪路径的类型比较常见,为跨时钟域的伪路径。

为了不对其进行时序分析,所以可以设置伪路径,功能与设置异步时钟组一致。

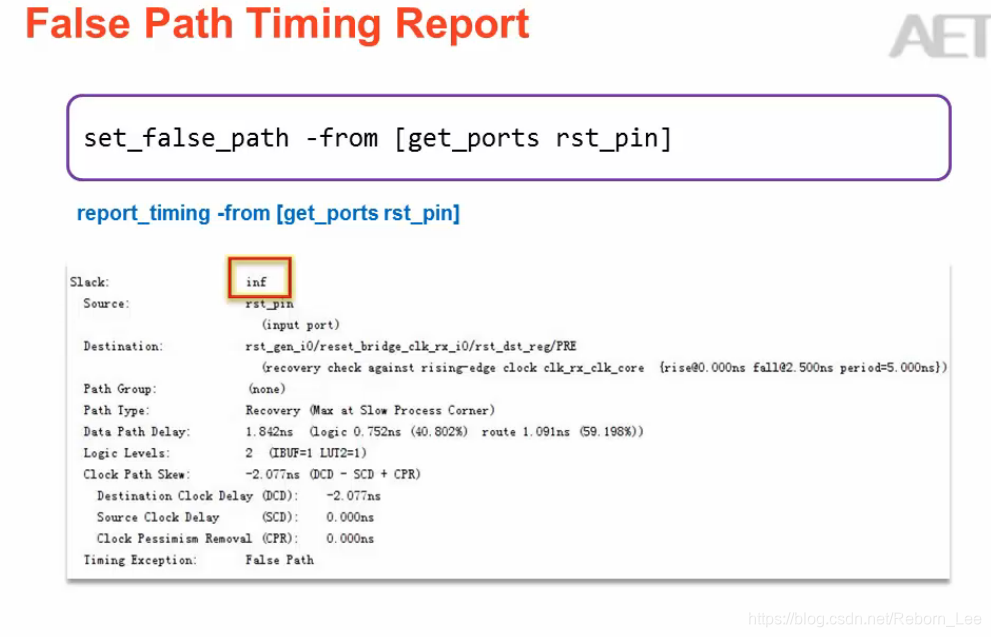

最后给出一个伪路径的时序报告案例:

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/85060377

- 点赞

- 收藏

- 关注作者

评论(0)