【 FPGA 】7 Series FPGA中对SRL的设计指导

Xilinx 7 Series FPGA and Zynq-7000 All Programmable SoC Libraries Guide for HDL Designs

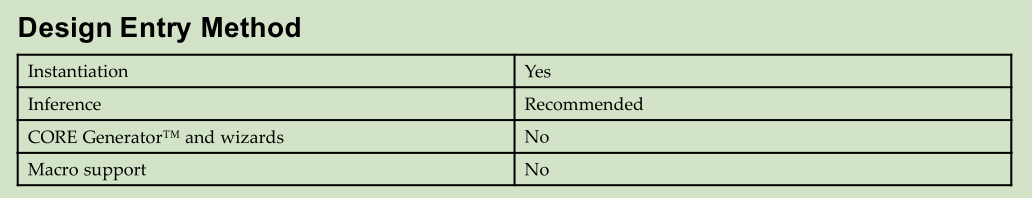

最近在看关于Ultrafast设计方法学的视频以及Vivado design Methodology的用户手册时,总是提到SRL,我总是很困惑,总是用这个缩写,到底是啥,也许没有看这些东西的时候,我还知道它就是移位寄存器,可是我总以为这里面提到的东西是什么高级的玩意,误导了自己,以为是什么更高级的结构,于是一探究竟,查看了7系列FPGA的元件库设计指导,也就是开头提到的那一串英文,不就是一个移位寄存器LUT嘛。

这篇博文简单对其进行一个介绍,以便能更深入地理解它。

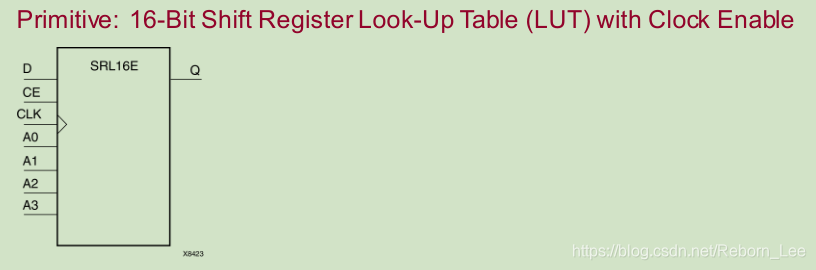

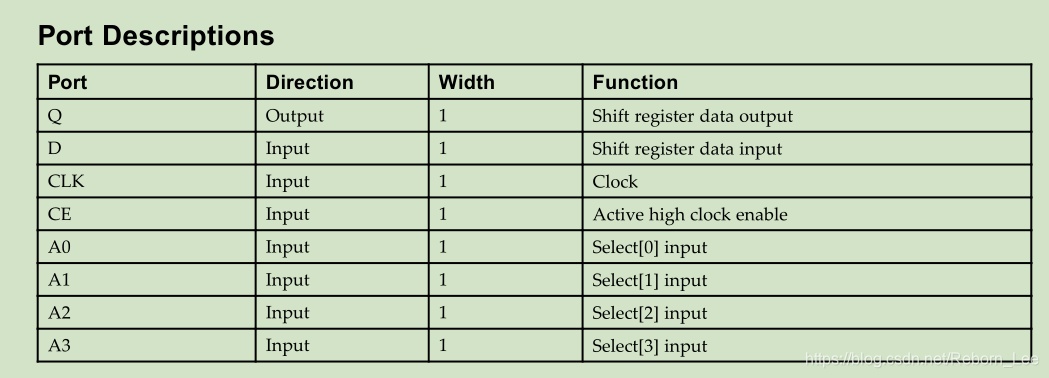

SRL16E

该设计元素是移位寄存器查找表(LUT)。 输入A3,A2,A1和A0选择移位寄存器的输出长度。

移位寄存器可以是固定的静态长度,也可以动态调整。

•创建固定长度的移位寄存器 - 使用静态值驱动A3至A0输入。 移位寄存器的长度可以在1位到16位之间变化,由下式确定:长度=(8 x A3)+(4 x A2)+(2 x A1)+ A0 +1如果是A3,A2, A1和A0都是零(0000),移位寄存器是一位长。 如果它们都是1(1111),则它是16位长。

•动态更改移位寄存器的长度 - 更改驱动A3至A0输入的值。 例如,如果A2,A1和A0都是1(111)并且A3在一(1)和零(0)之间切换,则移位寄存器的长度从16位变为8位。

在内部,移位寄存器的长度始终为16位,输入线A3至A0选择16位中的哪一位到达输出。

通过将四位十六进制数分配给INIT属性来初始化移位寄存器LUT内容。 第一个或最左边的十六进制数字是最重要的位。 如果未指定INIT值,则默认值为四个零(0000),以便在配置期间清除移位寄存器LUT。

当CE为高电平时,数据(D)在低电平到高电平时钟(CLK)转换期间被加载到移位寄存器的第一位。 在随后的低到高时钟转换期间,当CE为高电平时,数据在加载新数据时转移到下一个最高位位置。 当达到由地址输入确定的移位寄存器长度时,数据出现在Q输出上。 当CE为低电平时,寄存器忽略时钟转换。

Verilog InstantiationTemplate

// SRL16E: 16-bit shift register LUT with clock enable operating on posedge of clock (Mapped to a SliceM LUT6)

// 7 Series

// Xilinx HDL Libraries Guide, version 14.7

SRL16E #(

.INIT(16'h0000) // Initial Value of Shift Register

) SRL16E_inst (

.Q(Q), // SRL data output

.A0(A0), // Select[0] input

.A1(A1), // Select[1] input

.A2(A2), // Select[2] input

.A3(A3), // Select[3] input

.CE(CE), // Clock enable input

.CLK(CLK), // Clock input

.D(D) // SRL data input

);

// End of SRL16E_inst instantiation

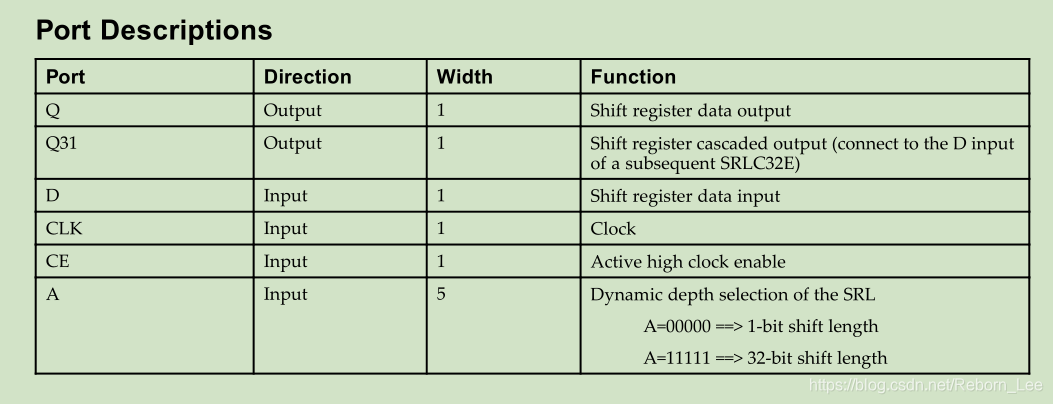

SRLC32E

该设计元素是在单个查找表(LUT)内实现的可变长度,1至32个时钟周期移位寄存器。 移位寄存器可以是固定长度,静态长度,也可以通过改变组件的地址线来动态调整。 该元件还具有高电平有效时钟使能和级联功能,其中可以级联多个SRLC32E,以创建更大的移位长度。

如果实例化,则应对此组件进行以下连接:

•将CLK输入连接到所需的时钟源,将D输入连接到要移位/存储的数据源,将Q输出连接到FDCE或FDRE输入或其他适当的数据目标。

•CE时钟使能引脚可以连接到设计中的时钟使能信号,或者如果不使用则连接到逻辑1。

•5位A总线可以连接到0到31之间的静态值,以表示固定的1到32位静态移位长度,或者它可以连接到适当的逻辑,以在1和32位之间的任何位置启用变化的移位深度。

•如果要创建比32更长的移位长度,请将Q31输出引脚连接到后续SRLC32E的D输入引脚,以级联并创建更大的移位寄存器。

•将Q31输出连接到除另一个SRLC32E以外的任何其他设备无效。

•如果需要,可选Q输出仍可在级联模式下使用。

•可以指定由32位十六进制值组成的可选INIT属性,以指示移位寄存器的初始移位模式。

•(INIT [0]将是第一个移出的值。)

Verilog InstantiationTemplate

// SRLC32E: 32-bit variable length cascadable shift register LUT (Mapped to a SliceM LUT6)

// with clock enable

// 7 Series

// Xilinx HDL Libraries Guide, version 14.7

SRLC32E #(

.INIT(32'h00000000) // Initial Value of Shift Register

) SRLC32E_inst (

.Q(Q), // SRL data output

.Q31(Q31), // SRL cascade output pin

.A(A), // 5-bit shift depth select input

.CE(CE), // Clock enable input

.CLK(CLK), // Clock input

.D(D) // SRL data input

);

// End of SRLC32E_inst instantiation

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/85114343

- 点赞

- 收藏

- 关注作者

评论(0)