【 Vivado 】Working with Sources in Non-Project Mode

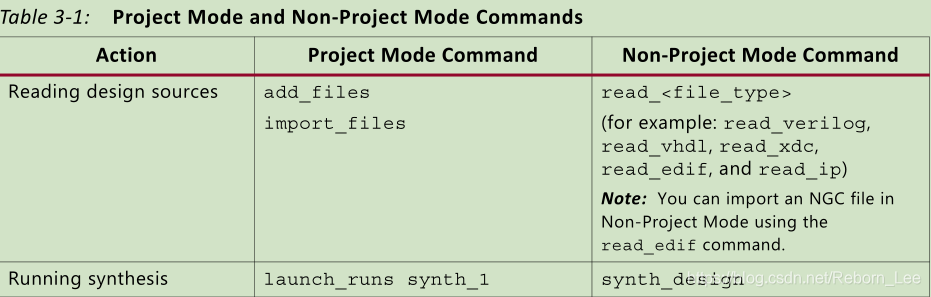

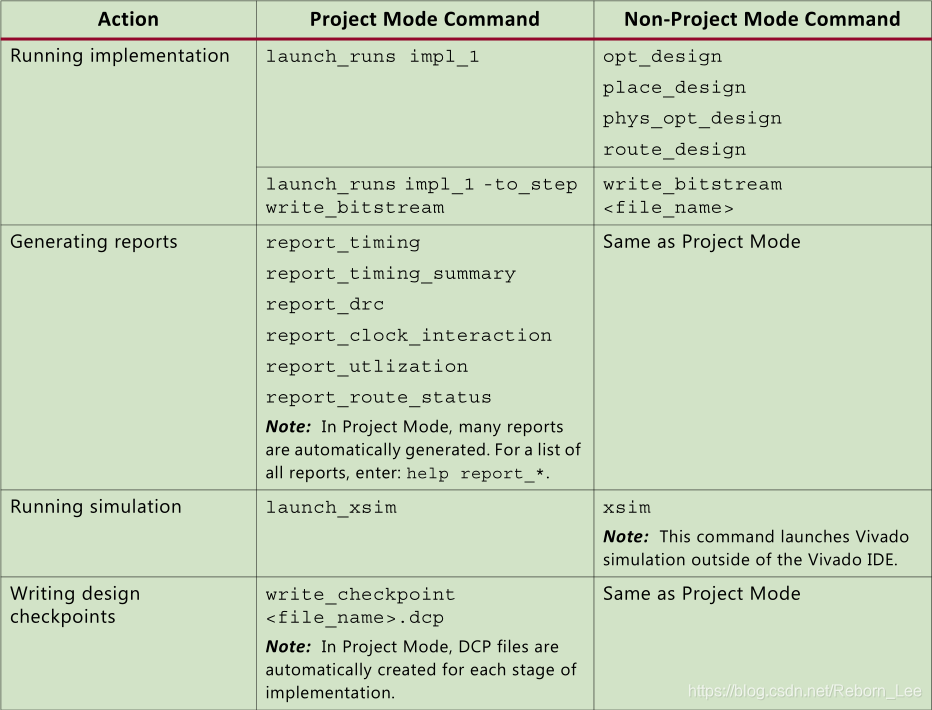

与为您管理源文件的项目模式不同,源文件在非项目模式下由您控制。 使用Tcl命令,指定要处理和输出要生成的文件的文件,包括网表,比特流和报告文件。 项目模式和非项目模式命令显示常用的项目模式命令和相应的非项目模式命令。

For more information on Project Mode and Non-Project Mode, see this link in the Vivado Design Suite User Guide: Design Flows Overview (UG892) [Ref 1].

For more information on Tcl commands, see the Vivado Design Suite Tcl Command Reference Guide (UG835) [Ref 4].

Note: In Non-Project Mode, files are compiled in the order the read_* commands are listed in the Tcl script.

Note: To Select a new part in the current installation, close the current project and upgrade the current installation to add additional part.

Following is an example of a Non-Project Mode script, which reads in various source files:

# create_bft_batch.tcl

# bft sample design

# A Vivado script that demonstrates a very simple RTL-to-bitstream batch flow

#

# NOTE: typical usage would be "vivado -mode tcl -source create_bft_batch.tcl"

#

# STEP#0: define output directory area.

#

set outputDir ./Tutorial_Created_Data/bft_output

file mkdir $outputDir

#

# STEP#1: setup design sources and constraints

#

read_vhdl -library bftLib [ glob ./Sources/hdl/bftLib/*.vhdl ]

read_vhdl ./Sources/hdl/bft.vhdl

read_verilog [ glob ./Sources/hdl/*.v ]

read_xdc ./Sources/bft_full.xdc

#

# STEP#2: run synthesis, report utilization and timing estimates, write checkpoint

design

#

synth_design -top bft -part xc7k70tfbg484-2 -flatten rebuilt

write_checkpoint -force $outputDir/post_synth

report_timing_summary -file $outputDir/post_synth_timing_summary.rpt

report_power -file $outputDir/post_synth_power.rpt

#

# STEP#3: run placement and logic optimzation, report utilization and timing

estimates, write checkpoint design

#

opt_design

place_design

phys_opt_design

write_checkpoint -force $outputDir/post_place

report_timing_summary -file $outputDir/post_place_timing_summary.rpt

#

# STEP#4: run router, report actual utilization and timing, write checkpoint design,

run drc, write verilog and xdc out

#

route_design

write_checkpoint -force $outputDir/post_route

report_timing_summary -file $outputDir/post_route_timing_summary.rpt

report_timing -sort_by group -max_paths 100 -path_type summary -file

$outputDir/post_route_timing.rpt

report_clock_utilization -file $outputDir/clock_util.rpt

report_utilization -file $outputDir/post_route_util.rpt

report_power -file $outputDir/post_route_power.rpt

report_drc -file $outputDir/post_imp_drc.rpt

write_verilog -force $outputDir/bft_impl_netlist.v

write_xdc -no_fixed_only -force $outputDir/bft_impl.xdc

#

# STEP#5: generate a bitstream

#

write_bitstream -force $outputDir/bft.bit

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/85240043

- 点赞

- 收藏

- 关注作者

评论(0)